Bei der IC-Prüfung wird festgestellt, ob der Chip Konstruktionsfehler oder physikalische Mängel aufweist, die durch den Herstellungsprozess verursacht wurden. Der Prozess kann mit verschiedenen Prüfverfahren durchgeführt werden.

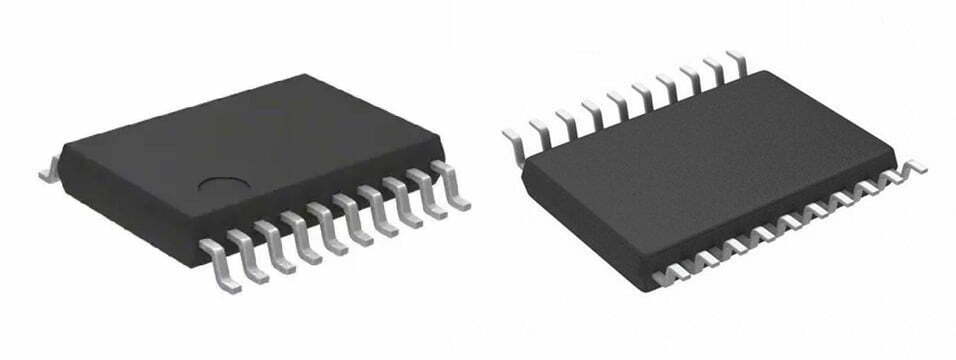

Bei der IC-Verpackung wird ein integrierter Schaltkreis (IC) in eine Schutzhülle eingeschlossen. Dieser Prozess schützt den IC vor Beschädigungen und stellt sicher, dass er ordnungsgemäß funktioniert. Außerdem ermöglicht er den Anschluss des IC an andere Geräte und Schaltkreise.

Wie testet man einen IC mit einem IC-Tester?

IC-Testkit

Auf dem Markt sind verschiedene Arten von IC-Testkits erhältlich, die jeweils für einen bestimmten Zweck entwickelt wurden. Einige IC-Testkits sind beispielsweise für allgemeine Testzwecke konzipiert. Andere sind für bestimmte Anwendungen wie Automobil-ICs oder Leistungs-ICs ausgelegt.

Die meisten IC-Testkits enthalten eine Vielzahl von grundlegenden Zubehörteilen, wie ein Multimeter, Sonden, einen digitalen IC-Tester und Messleitungen. Einige Kits enthalten möglicherweise auch speziellere Geräte, wie ein Oszilloskop oder einen Logikanalysator.

Prüfverfahren

Es gibt verschiedene Möglichkeiten, ICs zu testen, aber die gängigste Methode ist das sogenannte In-Circuit-Testing (ICT). Bei dieser Art von Test wird eine Testvorrichtung an das zu testende Gerät (DUT) angeschlossen. Anschließend führen wir eine Reihe von Tests durch, um die grundlegenden Funktionen zu überprüfen.

ICT kann sowohl zum Testen digitaler als auch analoger ICs verwendet werden. Bei digitalen ICs sendet der Tester eine Reihe von Eingangssignalen an das DUT. Anschließend werden die Ausgänge überprüft, um festzustellen, ob sie mit den erwarteten Ergebnissen übereinstimmen. Analoge ICs werden in der Regel mit einer Technik namens dynamischer Test getestet. Während dieses Prozesses sendet der Tester eine Reihe von Signalen an das DUT und misst dann die Reaktion.

Es gibt verschiedene Hersteller von ICT-Testern. Sie müssen einen Tester auswählen, der mit Ihren speziellen ICs kompatibel ist. Sobald Sie einen Tester haben, müssen Sie eine Testvorrichtung erstellen, die mit dem DUT verbunden wird. Die Testvorrichtung kann die erforderlichen Signale an den DUT senden und auch die Reaktion messen.

Sobald Sie beides haben, müssen Sie als Nächstes ein Testprogramm schreiben, um die Ergebnisse zu überprüfen. Dies kann ein zeitaufwändiger Prozess sein, aber es ist wichtig, um sicherzustellen, dass Ihre ICs ordnungsgemäß funktionieren.

Testarten

IC-Durchgangsprüfung

Der IC-Durchgangstest ist einfach und kann verwendet werden, um festzustellen, ob ICs ordnungsgemäß funktionieren.

Dieser Test wird durchgeführt, indem ein Multimeter an den IC angeschlossen und der Widerstand zwischen den verschiedenen Pins gemessen wird.

Wenn der IC ordnungsgemäß funktioniert, sollte der Widerstand niedrig sein (in der Regel weniger als 10 Ohm). Andernfalls ist der Widerstand hoch (in der Regel mehr als 10 Ohm).

Niveautests

IC-Level-Tests sind eine Art von elektrischen Tests, mit denen die Funktion und Leistung von integrierten Schaltkreisen (ICs) bestimmt wird.

Diese Prüfung wird in der Regel an ICs durchgeführt, die bereits auf einer Leiterplatte installiert sind.

Der Zweck der Prüfung besteht darin, zu überprüfen, ob der IC ordnungsgemäß funktioniert und die Spezifikationen für den vorgesehenen Verwendungszweck erfüllt.

Es gibt eine Vielzahl verschiedener Testmethoden für IC-Level-Tests, darunter Logiktests, Funktionstests und parametrische Tests.

Entwicklungsweg für IC-Gehäuse

Die Verpackung hat in etwa den folgenden Entwicklungsprozess durchlaufen:

1. In Bezug auf die Struktur:

TO –> DIP –> PLCC –> QFP –> BGA –> CSP –> WLP und SiP usw.

2. Materialien:

Metall, Keramik -> Keramik, Kunststoff -> Kunststoff;

3. Pin-Form:

Lange Inline-Leitungen -> kurze Leitungen oder keine Leitungen -> Kugelkontakte

4. Montageverfahren:

Durchsteckmontage -> Oberflächenmontage -> Direktmontage

5. Die treibende Kraft für die kontinuierliche Verbesserung der Verpackung:

Kleinere Größe, mehr Chip-Typen, mehr I/O

6. Schwierigkeiten:

Der Prozess wird immer komplexer, und es ist notwendig, die Wärmeableitung und die elektrische Leitfähigkeit zu berücksichtigen und gleichzeitig das Volumen zu reduzieren.

Merkmale und Kernkompetenzen

1. Starke Fertigungsmerkmale

Die Produktionskapazität hängt vollständig von der Beschaffung von Ausrüstung (Kapitalinvestitionen) ab und durchläuft wie die traditionelle Fertigung auch den Prozess der Kapazitätssteigerung und Prozessoptimierung. Mit der Größe kommen die gesammelten Erfahrungen und die Vorteile führender Technologie.

2. Der Umfang der Verpackung und Prüfung bestimmt die Kundenstruktur.

Große Designhersteller arbeiten nur mit Testherstellern zusammen, die eine bestimmte Größe haben. Wenn die Größe nicht zunimmt, ist es schwierig, große Aufträge anzunehmen und die Kundenstruktur zu optimieren. Daher werden Unternehmen mit führender Technologie und Größe in einen positiven Kreislauf eintreten: führende Technologie → Kundenentwicklung → Finanzierung der Expansion → Steigerung der Produktionskapazität → Prozessoptimierung → führende Technologie, und werden den Abstand zu ihren Mitbewerbern nach und nach vergrößern.

3. Kernkompetenz

Die beiden oben genannten Branchenmerkmale bestimmen die Kernkompetenz von professionellen IC-Testunternehmen:

Forschungs- und Entwicklungskapazitäten: Fokus auf der Entwicklung von Testverfahren und Testlösungen.

Grad der Marktorientierung: Die Fähigkeiten zur Entwicklung von Testprogrammen und zur Prozessoptimierung basieren auf den Testerfahrungen mit verschiedenen Chiptypen, die von einer Vielzahl von Kunden eingebracht werden.

Perfekter Testprozess: Durch die enge Integration von vorgelagerter Entwicklung und Wafer-Verarbeitung werden der Testprozess und die Verfahren kontinuierlich optimiert.

Kapitaloperationsfähigkeit: Die derzeitige Entwicklungsphase im Inland bestimmt, dass Größe die Voraussetzung für Entwicklung ist. Daher ist eine Finanzierungsfähigkeit, die der Technologie und Marktstärke entspricht, die Grundlage für die Entwicklung und das Wachstum von Unternehmen.

Markt für IC-Gehäuse und -Prüfung

1. IC-Verpackung und Testumfang

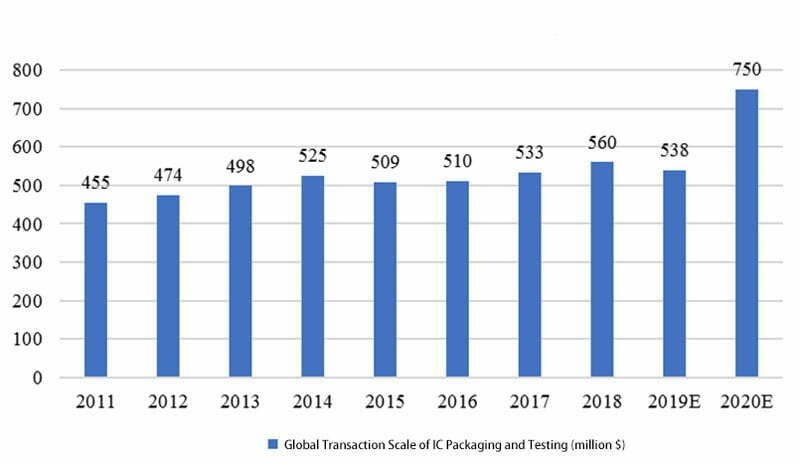

1.1 Globale Transaktionen im Bereich IC-Verpackung und -Prüfung (2011–2020)

Im Jahr 2019 verlangsamte sich die gesamte Halbleiterindustrie und verzeichnete ebenso wie der Markt für Chipverpackung und -prüfung ein negatives Wachstum. Letzterer erholte sich jedoch aufgrund der Nachfrage nach 5G, KI, IoT, Cloud Computing und Big Data. Experten prognostizierten, dass der Gesamtmarkt für Chipverpackung und -prüfung im Jahr 2024 ein Volumen von 75 Milliarden US-Dollar erreichen könnte.

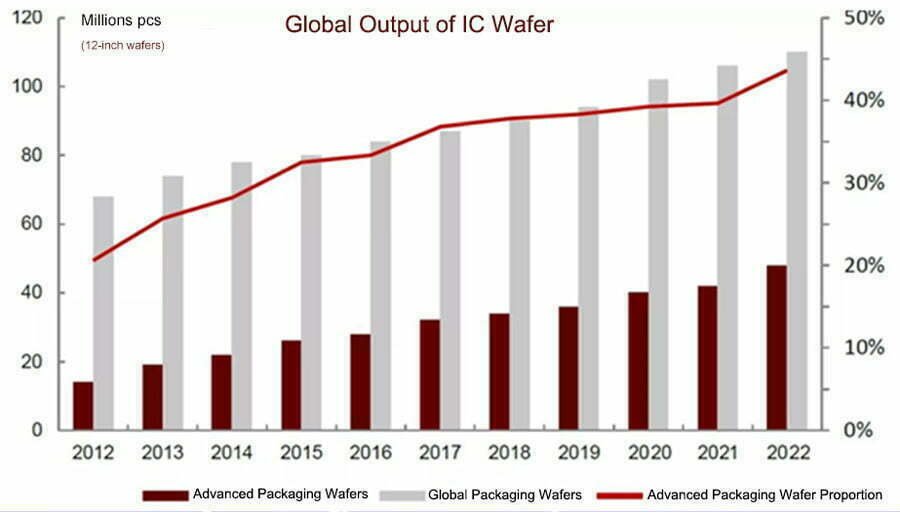

1.2 Weltweite Produktion von IC-Wafern (2012–2022)

Mit der Beschleunigung neuer Bereiche wie 5G, IoT und KI werden die erforderlichen Chipgrößen immer kleiner. Gleichzeitig gibt es immer mehr Chiptypen. Auch die Anzahl der I/O-Pins hat deutlich zugenommen, und die Nachfrage nach fortschrittlichen Verpackungslösungen ist allmählich gestiegen.

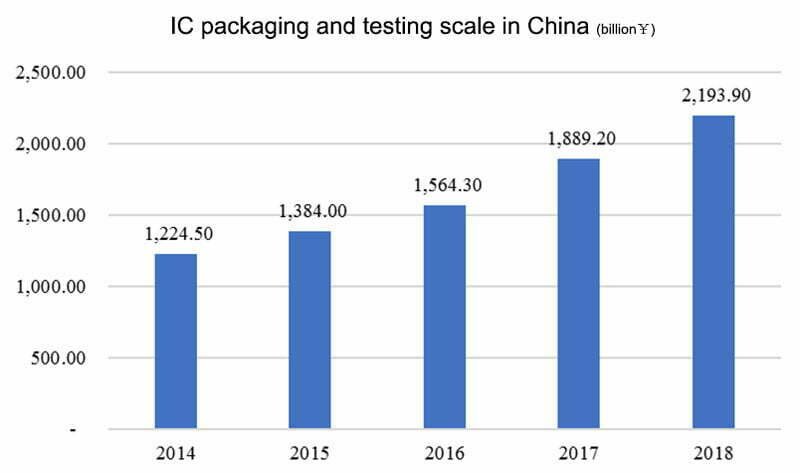

1.3 iC Verpackungs- und Prüfwaagen in China (2014–2018)

Im Jahr 2018 erreichte die Kapazität für die Verpackung und Prüfung von ICs auf dem chinesischen Festland 217,44 Milliarden Stück, und die Marktgröße der IC-Verpackungs- und Prüfindustrie erreichte 219,39 Milliarden Yuan, was einem Anstieg von 16,1 % gegenüber dem Vorjahr entspricht.

2. Das Wachstum des Umfangs fortschrittlicher Verpackungen

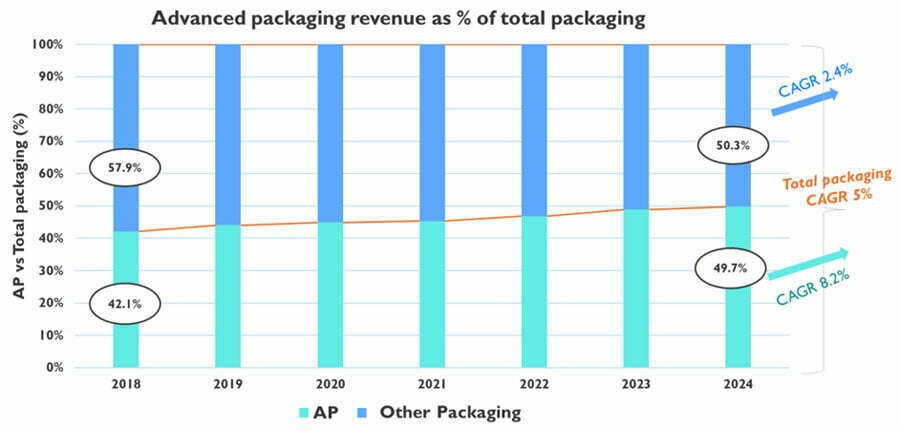

2.1 Anteil der fortschrittlichen IC-Verpackungen am Gesamtvolumen

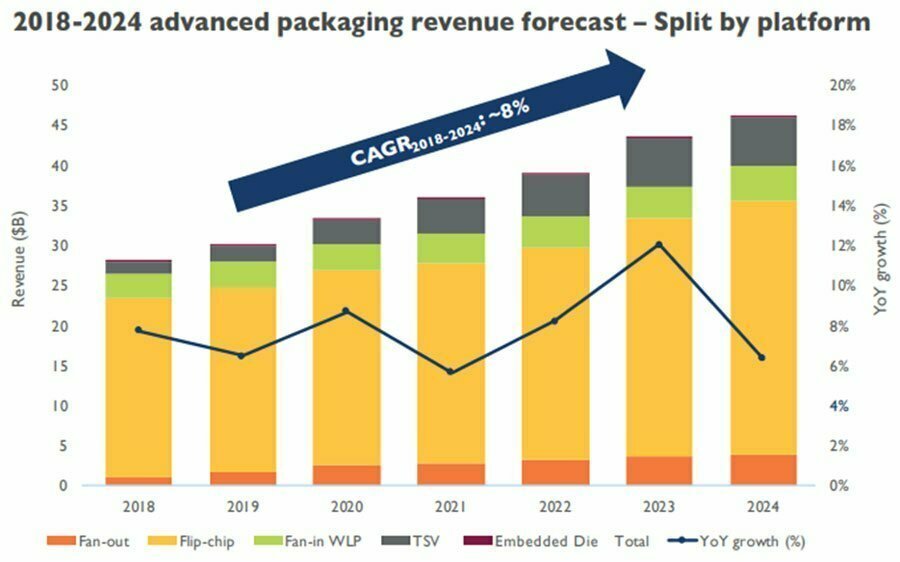

Laut Statistiken von Yole wird der Markt für fortschrittliche Verpackungen trotz der allgemeinen Konjunkturabschwächung und des negativen Wachstums der Halbleiterindustrie im Jahr 2019 seinen Wachstumstrend beibehalten. Im Jahr 2018 belief sich der Markt für fortschrittliche Verpackungen auf 27,6 Milliarden US-Dollar.

Mit einer durchschnittlichen jährlichen Wachstumsrate von 8 % wird er bis 2024 voraussichtlich ein Volumen von rund 44 Milliarden US-Dollar erreichen. Der traditionelle Verpackungsmarkt wird mit einer durchschnittlichen jährlichen Wachstumsrate von 2,4 % wachsen, während die CAGR der gesamten IC-Verpackungsindustrie 5 % erreichen wird.

2.2 Umsatzprognosen für Advanced Packaging (2018–2024)

Im Bereich der fortschrittlichen Verpackungstechnologien hat die Flip-Chip-Technologie den höchsten Anteil. Im Jahr 2018 machten die Einnahmen aus Flip-Chip-Verpackungen und -Tests etwa 81 % des Marktes für fortschrittliche Verpackungen aus. Bis 2024 wird dieser Anteil aufgrund der rasanten Entwicklung anderer Technologien auf 72 % sinken.

Von 2018 bis 2024 sind TVS, ED und Fan-Out die am schnellsten wachsenden Technologien. Die Umsatzwachstumsrate von 2,5D/3D-Verpackungen (TSV), ED- und Fan-Out-Verpackungen (Fan-Out) wird voraussichtlich 26 %, 49 % bzw. 26 % betragen.

Die CAGR von Fan-in WLP 2018-2024 ist mit nur 6,5 % relativ niedrig, und die Marktgröße von Embedded Die im Jahr 2018 beträgt weniger als 25 Millionen US-Dollar.

In den nächsten fünf Jahren wird die CAGR jedoch bis zu 49 % betragen, wobei die Haupttreiber die Nachfrage aus den Bereichen Kommunikationseinrichtungen, Automobilelektronik und Mobilfunkmärkte sein werden.

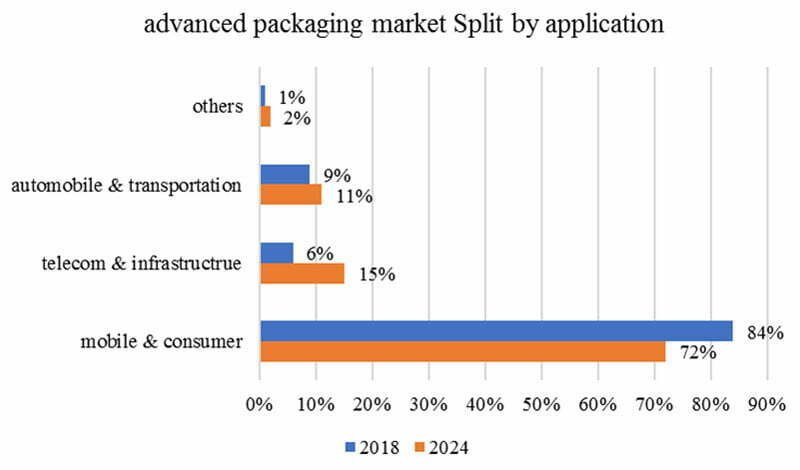

2.3 Fortgeschrittene Verpackungsanwendungen

Nach Anwendungsbereichen entfielen 2018 84 % des gesamten Marktes für fortschrittliche Verpackungen auf Mobil- und Verbraucheranwendungen. Von 2019 bis 2024 betrug die CAGR dieses Segments des Anwendungsmarktes 5 %, und 2024 entfielen 72 % des gesamten Marktes für fortschrittliche Verpackungen auf dieses Segment.

Das Segment Telekommunikation und Infrastruktur ist das am schnellsten wachsende Segment des Marktes für fortschrittliche Verpackungen (ca. 28 %), und sein Marktanteil wird von 6 % im Jahr 2018 auf 15 % im Jahr 2024 steigen.

Gleichzeitig stieg der Marktanteil des Automobil- und Transportsektors von 9 % im Jahr 2018 auf 11 % im Jahr 2024.

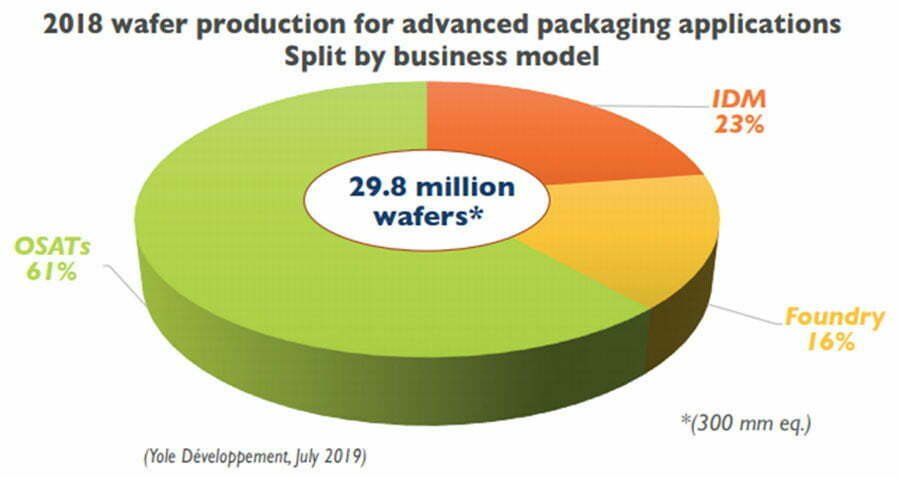

Im Jahr 2018 machten professionelle Chip-Verpackungs- und Test-Foundries 61 % des Marktes für fortschrittliche Verpackungs- und Testlösungen aus, während IDM-Unternehmen 23 % und Foundry-Hersteller 16 % ausmachten.

Wettbewerbsumfeld

1. Die 10 weltweit führenden Unternehmen (2018–2019)

Der Markt für Chipverpackung und -prüfung ist relativ konzentriert. Die zehn größten Hersteller kontrollieren etwa 80 % des Marktes. Hersteller aus Festlandchina und Taiwan dominieren den Markt. Seit vielen Jahren erzielt die taiwanesische Verpackungs- und Prüfindustrie fast die Hälfte des weltweiten Betriebsumsatzes und hat sich damit fest unter den Top Ten etabliert.

Unabhängig von den Einnahmen aus der Chipverpackung und -prüfung von IDMs (wie Intel und Samsung) liegen ASE und Amkor bei der professionellen Chipverpackung und -prüfung fest auf den ersten beiden Plätzen.

2. Chancen und Herausforderungen

Veränderungen in der Halbleiter-Lieferkette, Verschiebungen bei den Geschäftsmodellen und Unsicherheiten in den Handelsbeziehungen zwischen den USA und China haben für einige Hersteller Chancen und für andere Risiken mit sich gebracht.

2.1 Erweiterung der industriellen Wertschöpfungskette

In diesem sich ständig verändernden Geschäftsumfeld verändert sich die Halbleiter-Lieferkette auf allen Ebenen. Einige Anbieter haben erfolgreich neue Geschäftsmodelle eingeführt.

Dies hatte erhebliche Auswirkungen auf die IC-Fertigungskette, während andere Hersteller es versäumten, diese Dynamik zu nutzen. Verschiedene Anbieter haben unterschiedliche Triebkräfte, die sie dazu bewegen, in neue Geschäftsfelder zu expandieren.

Beispielsweise entwickeln Softwareunternehmen wie Google, Microsoft, Facebook und Alibaba ihre eigenen Prozessoren, um eine Integration/Anpassung auf Systemebene und die Kontrolle über die Lieferkette auf Montageebene zu erreichen.

Die größte Veränderung ist, dass Foundries beginnen, in das Geschäft mit fortschrittlichen Verpackungslösungen zu expandieren. Obwohl sie relativ „neu” sind, ist ihr Einfluss enorm.

2.2 Innovation in der Verpackungstechnik

TSMC ist führend bei Innovationen im Bereich Fan-Out-Packaging und fortschrittlichen 3D-Packaging-Plattformen. Das Unternehmen bietet eine Vielzahl von Produkten wie InFO (und dessen Varianten), CoWoS, WoW, 3D SoIC und mehr.

Fortschrittliche Verpackungen sind für TSMC zu einem ausgereiften Geschäftsfeld geworden. Das Unternehmen rechnet für 2019 mit einem Umsatz von 3 Milliarden US-Dollar, was ihm den vierten Platz im OSAT-Ranking einbringen würde.

UMC ist ein bedeutender Anbieter von Silizium-Interposern für 2,5D-Verpackungen. Das Unternehmen ist kürzlich eine Partnerschaft mit Xperi eingegangen, um ZiBond- und DBI-Technologien für verschiedene Halbleiterbauelemente zu optimieren und zu vermarkten.

Wuhan Xinxin (XMC) bietet 3D-IC-TSV-Gehäuse für Bildsensoren und Hochleistungsanwendungen an. Zusammen haben diese Akteure eine wichtige Rolle dabei gespielt, die Verpackung von Substraten auf Siliziumplattformen zu verlagern.

2.3 Verpackungen auf Systemebene sind tendenziell beliebt.

Es ist ein Trend, dass sich die Teilnehmer der SiP-Verpackungsindustriekette sowohl stromaufwärts als auch stromabwärts ausdehnen. In der traditionellen SiP-Verpackungsindustriekette gehören Changdian Technology und ASE zu den repräsentativen Unternehmen für IC-Verpackung und -Prüfung, die hauptsächlich funktionale Standardverpackungs- und Prüfprodukte anbieten. Das repräsentative Unternehmen für Verpackungen auf Systemebene ist USI, das hauptsächlich Systemverpackungen auf Modulebene anbietet. Diese beiden Unternehmen stehen in einer stromaufwärts- und stromabwärtsgerichteten Beziehung zueinander, und ihre Prozesse und die verwendeten Anlagen unterscheiden sich voneinander.

2.4 Eingebettete Chips

Auf der anderen Seite nutzen IC-Substrat- und PCB-Hersteller wie Samsung Electro-Mechanics (SEMCO), Unimicron, AT&S und Shinko Electric (Shinko) die Vorteile von eingebetteten Chips (und passiven Bauteilen) in Fan-Out-Gehäusen auf Panel-Ebene und organischen Substraten. Komponenten) im Bereich der fortschrittlichen Verpackung und greifen in den Marktanteil von OSAT ein (insbesondere im Geschäft mit fortschrittlichen Verpackungen).

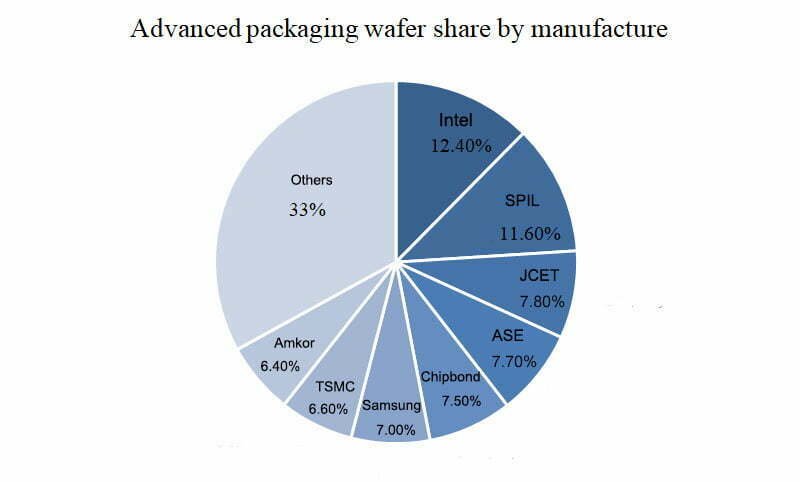

3. Marktanteil für fortschrittliche Verpackungswafer

Im Vergleich zur Gesamtmarktkonzentration im Bereich Verpackung und Prüfung ist die Marktkonzentration im Bereich fortschrittliche Verpackung und Prüfung relativ gering. Im Jahr 2017 entfielen 67 % des Marktanteils im Bereich fortschrittliche Verpackung auf die acht größten Hersteller.

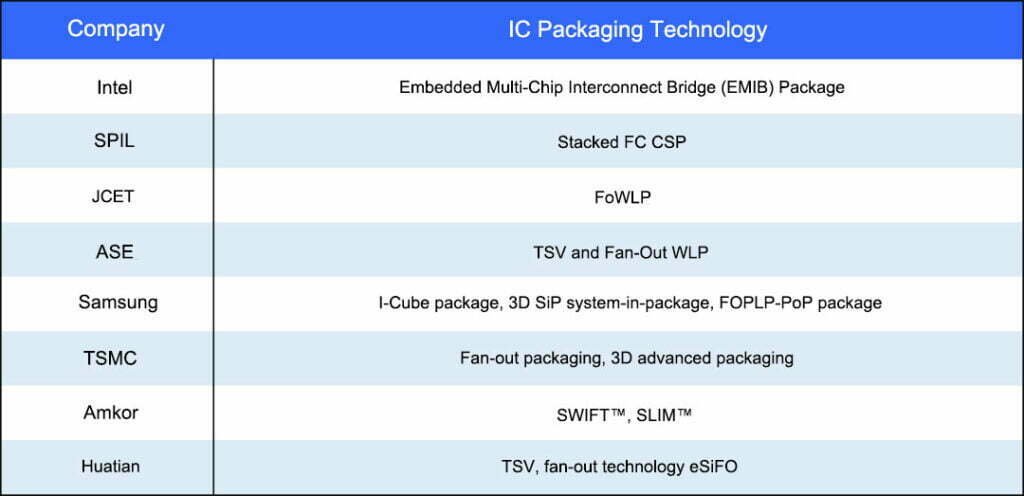

Anbieter auf dem Markt für fortschrittliche Verpackungen haben unterschiedliche Fachgebiete:

Situation der chinesischen IC-Verpackungsindustrie

Die chinesische IC-Verpackungsindustrie hat sehr früh begonnen und sich rasch entwickelt. Sie basiert hauptsächlich auf traditionellen Verpackungsprodukten. In den letzten Jahren haben inländische Hersteller Fusionen und Übernahmen durchgeführt. Derzeit ist die chinesische Technologieplattform im Wesentlichen mit der von ausländischen Herstellern synchronisiert. Darüber hinaus werden fortschrittliche Verpackungstechnologien wie BGA, TVS, WLCSP und SiP in Serie produziert.

Allerdings besteht nach wie vor eine gewisse Lücke zwischen den Gesamteinnahmen aus fortschrittlichen Verpackungen in Taiwan und den Vereinigten Staaten. Laut den Statistiken von TrendForce beliefen sich die Einnahmen aus fortschrittlichen Verpackungen in China im Jahr 2018 auf etwa 52,6 Milliarden Yuan. Dies entsprach 25 % der gesamten inländischen Einnahmen aus Verpackungen und Tests und lag damit unter dem weltweiten Anteil von 41 %. Es besteht also noch viel Raum für Wachstum in der Zukunft.

Chinas Markt für fortschrittliche IC-Verpackungen

Darüber hinaus besteht auch eine große Lücke zwischen Verpackungsunternehmen auf dem Festland und international führenden Herstellern. Besonders deutlich wird diese Lücke bei der Verpackungstechnologie für hochdichte integrierte Schaltkreise, wie beispielsweise der HPC-Chip-Verpackungstechnologie. Die von TSMC vorgeschlagene SoC-Multi-Chip-3D-Stapelungstechnologie. Sie verwendet eine Struktur ohne Bump-Bonding, wodurch die Gesamtberechnungsgeschwindigkeit von CPU/GPU und Speicher erheblich verbessert werden kann. Intel hat ebenfalls ein ähnliches 3D-Verpackungskonzept vorgeschlagen, bei dem Speicher auf CPU- und GPU-Chips gestapelt wird.

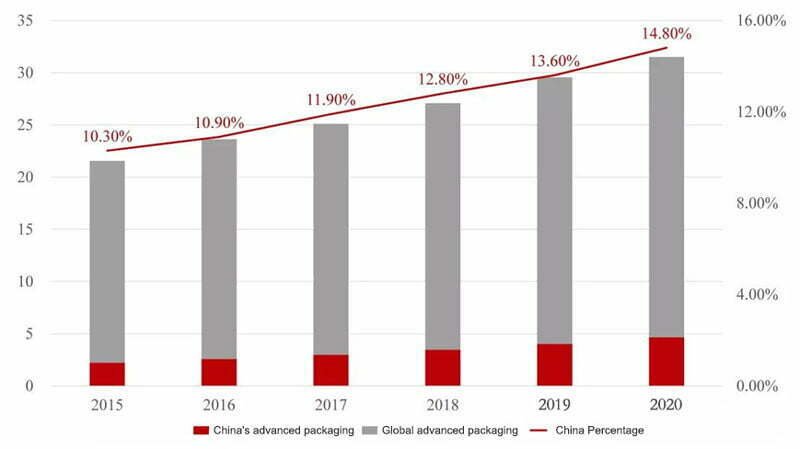

Der weltweite Produktionswert des chinesischen Marktes für fortschrittliche Verpackungen ist relativ gering, wächst jedoch rasant und sein Anteil nimmt zu. Daten von Yole zeigen: Im Jahr 2017 betrug der Produktionswert für fortschrittliche Verpackungen in China 2,9 Milliarden US-Dollar, was einem Anteil von 11,9 % am Weltmarkt entspricht, und bis 2020 wird er 4,6 Milliarden US-Dollar erreichen, was einem Anteil von 14,8 % am Weltmarkt entspricht. Den Daten zufolge haben chinesische Verpackungs- und Testunternehmen 2018 den Ausbau ihrer Produktionskapazitäten im Bereich der fortschrittlichen Verpackung beschleunigt, mit einer Wachstumsrate von 16 %, die doppelt so hoch ist wie die weltweite Wachstumsrate.

Markt-Treibkraft

Es gibt zwei Entwicklungswege für fortschrittliche Verpackungen:

Der eine besteht darin, die Größe zu reduzieren, um sie an die Chipgröße anzupassen. Ein wichtiger Indikator ist das Verhältnis von Chipfläche zu Verpackungsfläche. Je näher dieses Verhältnis an 1 liegt, desto besser, einschließlich WLCSP, FC, Bumping, Fanout usw.

Der zweite Weg ist die funktionale Entwicklung, die den Schwerpunkt auf heterogene Integration legt und Multifunktionalität bei der Systemminiaturisierung bietet, einschließlich TSV, SIP und so weiter.

1. SIP-Technologie

Der weltweite Halbleiterherstellungsprozess nähert sich der physikalischen Grenze von Dioden. Der fortschrittlichste Prozess ist 7 nm. Aufgrund der enormen Investitionen wird es immer teurer, die Chip-Leistung aus Sicht der Herstellung weiter zu verbessern. Ausgehend von der Chip-Verpackung kombiniert die System-in-Package-Technologie SIP Chips mit unterschiedlichen Funktionen wie Logik-Chips und Speicher.

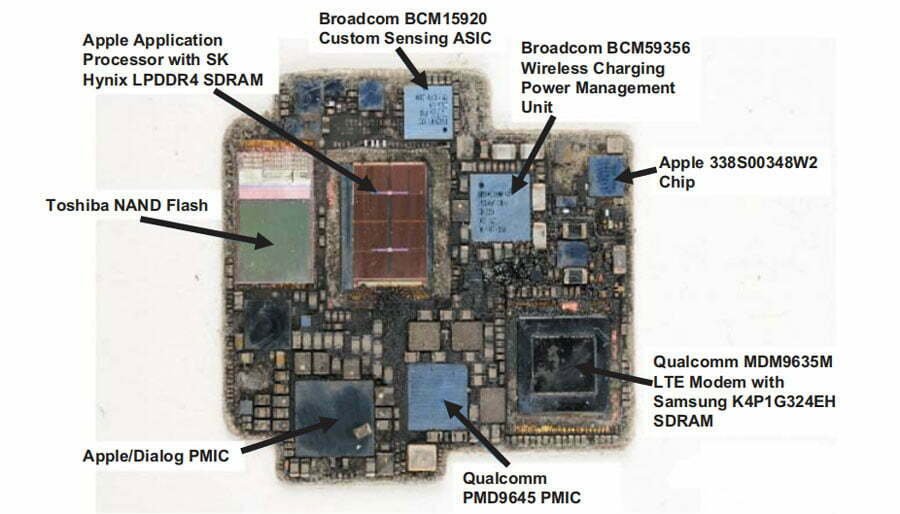

Passive Komponenten IPD, RF RF und Sensoren sowie andere Chips werden in einem Modul verpackt, wodurch die Chipgröße reduziert, die Chip-Leistung verbessert und der Stromverbrauch gesenkt werden kann. Das Internet der Dinge (IoT) ist ein wichtiges Anwendungsszenario, das die Entwicklung der SIP-Verpackungstechnologie fördert, und tragbare Geräte sind ein Bereich mit großem Anwendungspotenzial für die System-in-Package-Technologie in der Zukunft. Der Fingerabdruckerkennungssensor, der 3D-Gesichtserkennungssensor, das WiFi-Funknetzwerk und andere Funktionsmodule in der Apple Watch sind zusammen verpackt, was die Verwendung der System-in-Package (SiP)-Modultechnologie von ASE darstellt.

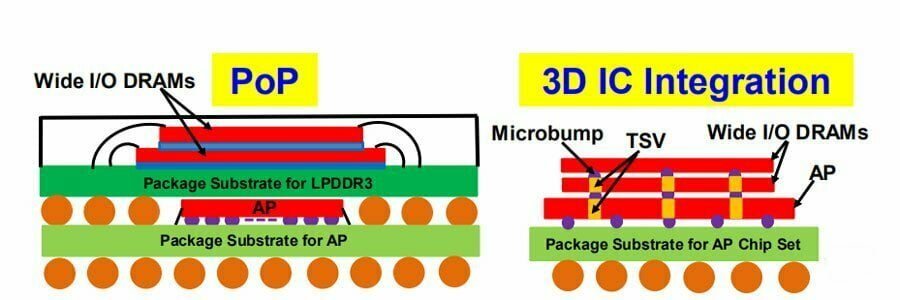

Die SIP-Technologie integriert erfolgreich integrierte Schaltkreise, diskrete Bauelemente, optische Bauelemente, Speicher, mehrschichtige Keramikkondensatoren und Chipwiderstände in dünne, schmale und kurze Substrate, ohne dass sich deren Informationen gegenseitig stören. Wir glauben, dass Apple bei der Anwendung von Systemverpackungen mindestens ein bis zwei Jahre Vorsprung vor seinen Mitbewerbern hat. Je nach Anwendungsanforderungen und Produktkomplexität lassen sich die Arten von System-in-Package (SiP) in 2D-Module mit mehreren aktiven und passiven Komponenten und komplexere 3D-Module unterteilen. Beispiele hierfür sind PiP (Package-in-Package) im System, PoP (Package-on-Package) und 2,5D/3D-Verpackungstechnologie auf dem System.

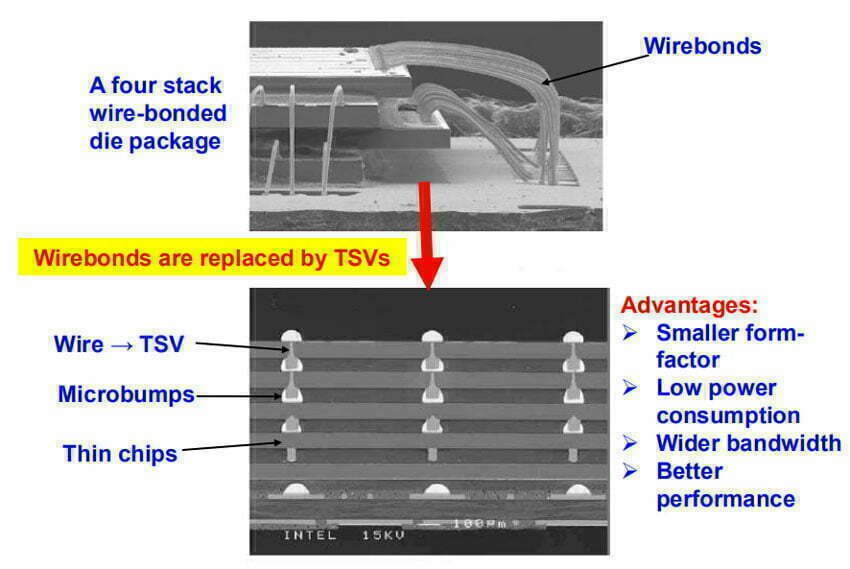

2. TSV-Technologie

Als Vertreter der 3D-Verpackungstechnologie wird die TSV-Technologie in Zukunft größere Anwendungen im Bereich der 3DNANDFLASH-Flash-Speicherverpackung und der DRAM-Speicherverpackung finden. Speicher ist zum Teilbereich mit dem größten Wachstumspotenzial im heimischen Halbleiterbereich geworden. Die beiden großen Speicherprojekte Yangtze Memory (NAND FLASH) und Hefei Changxin (DRAM) werden 2020 in Serie gehen, was für heimische Hersteller mit fortschrittlicher Verpackungstechnologie zweifellos enorme Wachstumschancen mit sich bringen wird.

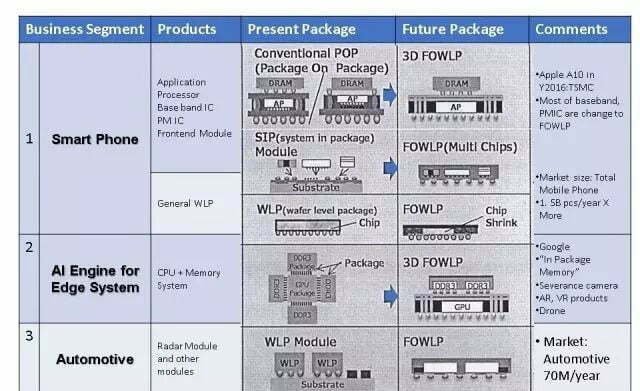

3. Fan-out

Mit dem Eintritt in das 5G-Zeitalter müssen zur Erzielung höherer Datenübertragungsraten und Bandbreitenkapazitäten elektromagnetische Wellen mit höheren Frequenzen als Übertragungsmedium verwendet werden, deren Wellenlängen kürzer sind und in den Millimeterwellenbereich reichen. Die beiden Hauptfrequenzen im 5G-Zeitalter, das Sub-6GHz-Frequenzband und das 28GHz-Millimeterwellenfrequenzband, führen aufgrund der höheren Frequenz zu einer kürzeren Wellenlänge, sodass die Antenne kürzer ist. Daher wird erwartet, dass die Antenne im 5G-Chip-Zeitalter in den Chip integriert wird, um das Design zu vereinfachen und die Kosten zu senken.

Für 5G-Chips der nächsten Generation gibt es zwei mögliche Verpackungstechnologien: AiP (Antenna in Package) mit einem Substrat und ein Fan-Out-Gehäuse ohne Trägerplatine. Da das zweite Fan-Out-Verpackungsschema kein Substrat erfordert, können die Kosten weiter gesenkt und die Chipgröße auf der Grundlage der Integration mehrerer Chips reduziert werden, sodass die Fan-Out-Verpackungstechnologie möglicherweise zur Mainstream-Technologie für die Verpackung von 5G-Chips wird.

Jedes elektronische Modul im Auto verwendet unterschiedliche Verpackungstechnologien, und auch für die Verpackung des Millimeterwellen-Radarchips in der Automobilelektronik wird in großem Umfang die Fan-out-Verpackungstechnologie zum Einsatz kommen.

Das inländische Verpackungs- und Testwerk Changdian Technology erwarb nach der Übernahme von Xingke Jinpeng die eWLB-Verpackungstechnologie und wurde damit zu einem der ersten Verpackungs- und Testhersteller im Bereich Millimeterwellenradar. Es wird erwartet, dass Huatian Technology nach den jüngsten technologischen Durchbrüchen Anstrengungen in diesem Bereich unternehmen wird.

Technologieentwicklungsrichtung

Es gibt zwei Arten von Halbleiterverpackungen: traditionelle Verpackungen und fortschrittliche Verpackungen. Mit der kontinuierlichen Ausweitung des Umfangs fortschrittlicher Verpackungen hat sich deren Anteil allmählich dem Trend traditioneller Verpackungen angenähert und diesen sogar übertroffen. Für die Halbleiterindustrie sind Verpackung und Prüfung nicht mehr nur ein separater Fertigungsschritt wie in der Vergangenheit, sondern eine integrierte Lösung, die Design, Material und Ausrüstung miteinander verbindet.

Daher gewinnt die fortschrittliche Verpackung im Bereich der Halbleiterverpackung und -prüfung zunehmend an Bedeutung. Laut Prognose von Yole wird der weltweite Markt für fortschrittliche Verpackungen bis 2020 einen Anteil von 44 % an den gesamten Verpackungsdienstleistungen für integrierte Schaltkreise erreichen, mit einem jährlichen Betriebsergebnis von etwa 31,5 Milliarden US-Dollar; Chinas Markt für fortschrittliche Verpackungen wird 2020 einen Wert von 4,6 Milliarden US-Dollar erreichen, mit einer durchschnittlichen jährlichen Wachstumsrate von 16 %. Aus technischer Sicht sind FOWLP, SiP und 3DTSV die drei wichtigsten fortschrittlichen Verpackungs- und Testtechnologien.

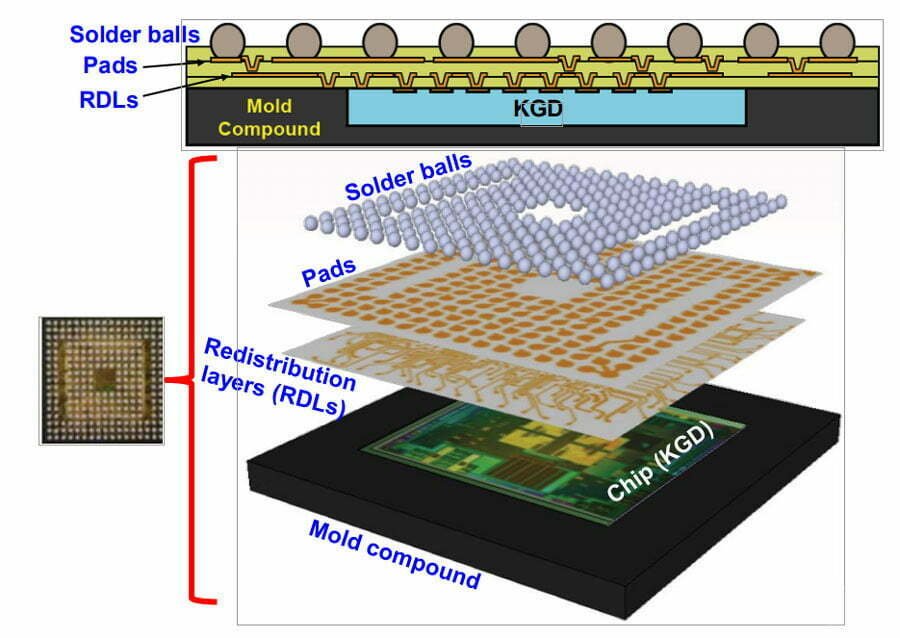

1. FOWLP-Verpackung

Das FOWLP-Paket bezeichnet eine neue Methode, bei der mehrere Chips aus heterogenen Prozessen zu einem kompakten Paket zusammengefasst werden. Es wurde erstmals von Intel vorgeschlagen. Die Vorteile von FOWLP gegenüber der Fan-In-Verpackungstechnologie sind: geringere Paketsdicke, Skalierbarkeit (zur Erhöhung der Anzahl der I/Os), verbesserte elektrische Leistung, gute thermische Leistung und ein substratloser Prozess.

2. SiP-Verpackung

System-in-Package (SiP) ist eine neue Art von Verpackungstechnologie auf höchstem Niveau im Bereich der IC-Verpackung, bei der ein oder mehrere IC-Chips und passive Komponenten in einem Gehäuse integriert werden. SiP ist eine ideale Lösung, die die Vorteile bestehender Kernressourcen und Halbleiterfertigungsprozesse kombiniert, um Kosten zu senken und die Markteinführungszeit zu verkürzen. Gleichzeitig überwindet es Schwierigkeiten wie Prozesskompatibilität, Signalvermischung, Rauschstörungen und elektromagnetische Interferenzen in SOC. Darüber hinaus ist die Anwendung von SiP sehr umfangreich. Derzeit hat der Output-Wert von Smartphones mit etwa 70 % den höchsten Anteil.

Die steigende Nachfrage nach SiP-Verpackungen wurde durch die kommerzielle Nutzung der 5G-Technologie ausgelöst. Erstens ist aufgrund des Wertanstiegs von eigenständigen HF-Komponenten der Gesamtmarkt für HF-Frontends rapide gewachsen. Es gibt einen allgemeinen Trend zur Modularisierung von RF-Frontends, 5G-Millimeterwellenantennen und RF-Integrationskomponenten, die in der Regel auf GaAs basieren. Die 5G-Antenne besteht hauptsächlich aus LCP (Liquid Crystal Polymer), und SiP-Verpackungen eignen sich gut für heterogene Integrationen. Es wird erwartet, dass SiP-Verpackungen im RF-Sektor an Popularität gewinnen werden.

3. 3D-Verpackung – TSV

3D-Verpackungen verbessern die Kernleistung wie Größe, Gewicht, Geschwindigkeit, Ausbeute und Energieverbrauch und werden von den meisten Halbleiterherstellern als die vielversprechendste Verpackungsmethode angesehen. Da sich die Tentakel der fortschrittlichen Verpackungstechnologie immer weiter auf fortschrittliche Technologien mit hoher Leistung und hoher Integrationsdichte ausdehnen, wird erwartet, dass TSV, bekannt als die 3D-Verpackungstechnologie der vierten Generation, zu einer nachhaltigen Triebkraft für die zukünftige Entwicklung fortschrittlicher Verpackungstechnologien wird.