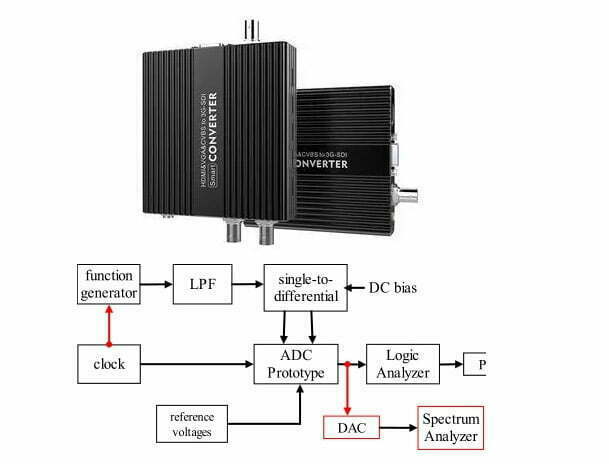

Akıllı cihazlar arasında ADC ve DAC dönüştürücüler hayati bir rol oynar. Günümüzde yaygın olarak kullanılan mikroişlemcilerin yalnızca ayrık dijital sinyalleri işleyebildiğini biliyoruz. ADC olmadan fiziksel dünyadan gelen sürekli bir analog sinyali mikroişlemciye aktarmak mümkün değildir. Ayrıca, DAC olmadan mikroişlemciden analog sinyal çıkışı elde etmek de mümkün değildir. (dijital sinyal ve analog sinyal hakkında daha fazla bilgi için buraya tıklayın)

Analog-dijital dönüştürücü (ADC)

ADC'nin tanımı

Enstrümantasyon sistemlerinde, sıcaklık, basınç, akış hızı, hız, ışık şiddeti vb. gibi algılanan ve sürekli değişen analog büyüklüklerin, işlenmek üzere bilgisayara girilmeden önce ayrık dijital büyüklüklere dönüştürülmesi sıklıkla gereklidir. Bu analog büyüklükler, sensörler tarafından elektrik sinyallerine (genellikle voltaj sinyallerine) dönüştürülür ve amplifikatörler tarafından güçlendirildikten sonra dijital büyüklükler haline gelmek üzere belirli bir işleme tabi tutulmaları gerekir. Analog sinyalleri dijital sinyallere dönüştüren bir cihaza genellikle analog-dijital dönüştürücü (ADC) veya kısaca A/D denir.

ADC'nin çalışma prensibi

Normal şartlar altında, A/D dönüştürme genellikle örnekleme, tutma, niceleme ve kodlama olmak üzere dört aşamadan geçer.

Örnekleme ve tutma

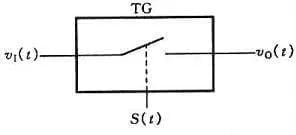

Örnekleme, zamanla sürekli olarak değişen bir analog büyüklüğü, zaman açısından ayrık bir analog büyüklüğe dönüştürme işlemidir. Örnekleme sürecinin şematik diyagramı Şekil 1’de gösterilmiştir. Şekil (a), örnekleme devresinin yapısını göstermektedir. Bu devrede, iletim kapısı örnekleme sinyali S(t) tarafından kontrol edilir; S(t) sinyalinin darbe genişliği τ süresince iletim kapısı açılır ve çıkış sinyali vO(t) giriş sinyali v1 olur; (Ts-τ) süresince ise iletim kapısı kapanır ve çıkış sinyali vO(t)=0 olur. Devredeki sinyal dalga formları Şekil (b)'de gösterilmiştir.

Analizden anlaşıldığı üzere, örnekleme sinyali S(t)’nin frekansı ne kadar yüksek olursa, elde edilen sinyal düşük geçiren filtreden geçtikten sonra giriş sinyalini o kadar aslına sadık bir şekilde yeniden üretebilir. Ancak sorun, veri miktarının artmasıdır. Uygun bir örnekleme frekansı sağlamak için, örnekleme teoremini karşılaması gerekir.

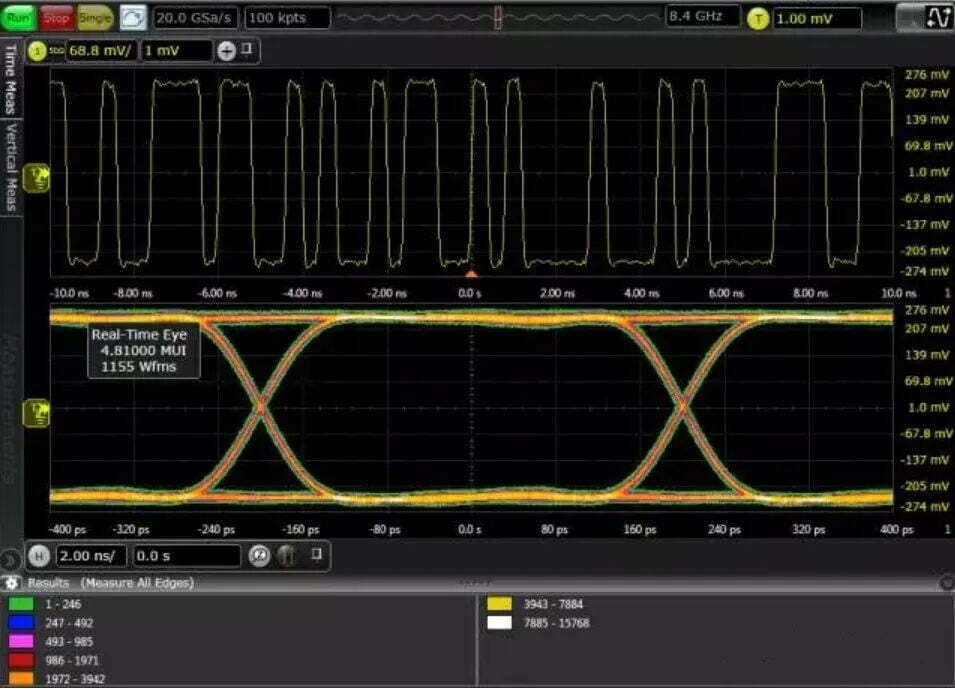

Örnekleme teoremi: Örnekleme sinyali S(t) 'nin frekansı fs ve giriş analog sinyali v1(t) 'nin en yüksek frekans bileşeninin frekansı fimax olduğunu varsayalım, o zaman fs ve fimax aşağıdaki ilişkiyi karşılamalıdır: fs≥2fimax ve mühendislikte genellikle fs> (3~5) fimax alınır.

Örnekleme devresi tarafından elde edilen analog sinyali her seferinde dijital sinyale dönüştürmek belirli bir süre alır. Sonraki niceleme ve kodlama işlemi için kararlı bir değer sağlamak amacıyla, her seferinde elde edilen analog sinyal, tutma devresi tarafından bir süre tutulmalıdır.

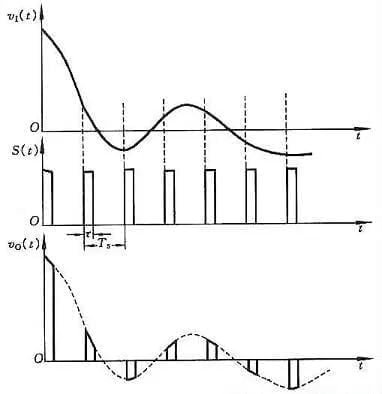

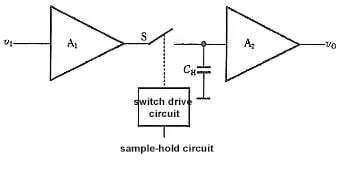

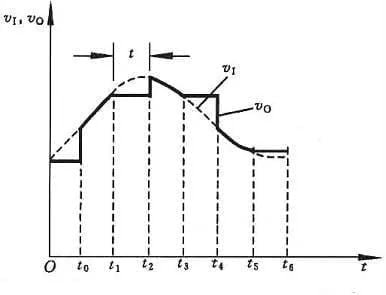

Örnekleme ve tutma işlemi genellikle örnekleme-tutma devresi aracılığıyla eşzamanlı olarak tamamlanır. Örnekleme-tutma devresinin şematik diyagramı ve çıkış dalga formu Şekil 2'de gösterilmiştir.

Devre, giriş amplifikatörü A1, çıkış amplifikatörü A2, tutma kondansatörü CH ve anahtar sürücü devresinden oluşur. Giriş sinyali kaynağı üzerindeki etkiyi azaltmak için A1’in devrede yüksek bir giriş empedansına sahip olması gerekir. Tutma aşamasında CH üzerinde depolanan yükün boşalmasını zorlaştırmak amacıyla A2’nin de yüksek bir giriş empedansına sahip olması gerekir; ayrıca A2’nin düşük bir çıkış empedansına sahip olması, devrenin yük taşıma kapasitesini artırabilir. Genel olarak, devrede AV1·AV2=1 olması da gereklidir.

Şimdi Şekil 2 ile birlikte devrenin örnekleme-tutma çalışma prensibini analiz edelim. t=t0'da anahtar S kapalıdır ve kondansatör hızla şarj olur. AV1 · AV2=1 olduğundan, v0=vI'dir ve örnekleme periyodu t0~t1 zaman aralığıdır. t=t1 zamanında S açılır. A2'nin giriş empedansı sonsuz ve S ideal bir anahtar ise, CH kondansatörünün deşarj devresi olmadığı ve uçlarındaki gerilimin v0'da sabit kaldığı kabul edilebilir. Şekil 11.8.2(b)'deki t1'den t2'ye kadar olan düz bölüm, tutma aşamasıdır.

Örnekleme-tutma devresi, çeşitli tiplerdeki monolitik entegre devrelerle üretilebilir. Örneğin, bipolar teknoloji için AD585 ve AD684; karışık teknoloji için AD1154 ve SHC76 vardır.

Sayısallaştırma ve kodlama

Dijital sinyaller sadece zaman açısından ayrık olmakla kalmaz, aynı zamanda genlik açısından da süreksizdir. Herhangi bir dijital büyüklüğün değeri, yalnızca belirli bir minimum birim büyüklüğünün tam sayı katı olabilir. Analog sinyali dijital bir büyüklüğe dönüştürmek için, A/D dönüştürme sürecinde örnekleme-tutma devresinin çıkış gerilimi de belirli bir yaklaşımla karşılık gelen ayrık seviyeye normalleştirilmelidir. Bu dönüştürme sürecine sayısallaştırma denir. Sayısallaştırma, sayısallaştırma olarak adlandırılır. Sayısallaştırılmış değerin sonunda kodlama süreciyle bir kodla temsil edilmesi gerekir. Kodlamadan sonra elde edilen kod, A/D dönüştürücü tarafından verilen dijital niceliktir.

Kuantizasyon sürecinde alınan en küçük miktar birimine kuantizasyon birimi denir ve △ ile gösterilir. Bu, dijital sinyalin en düşük bitinin 1 olduğu, yani 1LSB olduğu zamana karşılık gelen analog miktardır.

Sayısallaştırma sürecinde, örnekleme voltajı △ ile bölünebilir olmayabileceğinden, sayısallaştırma öncesinde ve sonrasında kaçınılmaz olarak bir hata oluşur. Bu hataya sayısallaştırma hatası denir ve ε ile gösterilir. Sayısallaştırma hatası, ortadan kaldırılamayan temel bir hatadır. A/D dönüştürücünün bit sayısı ne kadar fazla olursa, ayrık seviyeler arasındaki fark o kadar azalır ve sayısallaştırma hatası o kadar azalır.

Kuantizasyon sürecinde genellikle iki yaklaşık kuantizasyon yöntemi kullanılır: sadece yuvarlama kuantizasyonu ve yuvarlama kuantizasyonu.

sadece yukarı yuvarlama niceleme yöntemi

3 bitlik A/D dönüştürücüyü örnek olarak ele alalım; giriş sinyali v1'in 0 ile 8 V arasında değiştiğini varsayalım. Yukarı yuvarlama niceleme yöntemi kullanıldığında, △=1 V alınır ve niceleme biriminde yer almayan kısım atılır. Değer 0 ile 8V arasındaysa, 1V arasındaki analog voltaj 0△ olarak kabul edilir ve ikili sayı 000 ile temsil edilir; 1V ile 2V arasındaki analog voltaj ise 1△ olarak kabul edilir ve ikili sayı 001 ile temsil edilir… Bu niceleme yönteminin maksimum hatası △'dir.

yuvarlama kuantizasyon yöntemi

Yuvarlama niceleme yöntemi benimsenirse, △=8V/15 niceleme birimi kullanılır; niceleme işlemi sırasında niceleme biriminin yarısından küçük olan kısım atılır, niceleme biriminin yarısına eşit veya daha büyük olan kısım ise bir niceleme birimi olarak kabul edilir. 0 ~ 8V/15 arasındaki analog voltajı, ikili 000 ile temsil edilen 0△ olarak ele alır ve 8V/15 ~ 24V/15 arasındaki analog voltajı, ikili sayı 001 ile temsil edilen 1△ olarak kabul eder.

Karşılaştırma

Sadece yuvarlama içeren ilk niceleme yönteminde maksimum niceleme hatası│εmax│=1LSB iken, yuvarlama ve kesme içeren ikinci niceleme yönteminde│εmax│=1LSB/2'dir; ikinci yöntemin niceleme hatası ilkinden daha küçüktür, bu nedenle çoğunlukla A/D dönüştürücülerde bu yöntem kullanılmaktadır.

Entegre devrelerin hızlı gelişimi ile birlikte, A/D dönüştürücüler için yeni tasarım fikirleri ve üretim teknikleri durmaksızın ortaya çıkmaktadır. Çeşitli algılama ve kontrol ihtiyaçlarını karşılamak üzere farklı yapı ve performanslara sahip A/D dönüştürücüler tasarlanmaktadır.

ADC Türleri

ADC'nin entegrasyonu

dönüşüm ilkesi

ADC entegrasyonunun çalışma prensibi, voltajın entegre edilmesine ve entegre edilen voltajın sayımı kontrol etmek amacıyla başka bir voltajla karşılaştırılmasına dayanır; sayım çıkışı ise ADC çıkışıdır. Entegrasyon işlemi ya referans voltajı temel alır ya da referans voltajı ile giriş voltajını temel alır.

Artıları ve Eksileri

Avantajları:

- Entegre ADC yüksek çözünürlüğe sahiptir ve basamak sayısı 12 veya daha fazla olabilir.

- Doğrusallık çok iyidir. Esasen, çıkışın belirlenmesi için giriş entegre bir referans voltajıyla karşılaştırılır, bu nedenle doğrusallık karşılaştırıcının doğruluğuna bağlı olacaktır.

- Devre gerçekleştirme topolojisi basittir ve bu cihazları gerçekleştirmek için kullanılan bileşen sayısı nispeten azdır, bu nedenle devre nispeten basittir ve üretim maliyeti düşüktür.

Dezavantaj:

- Ana dezavantajı, dönüşüm hızının yavaş olmasıdır. N-bit ADC'de, çıkışın tek bir örnekleme noktasını dönüştürmesi 2 N saat döngüsü kadar sürebilir.

Uygulamalar

Öncelikle, hızdan çok doğruluğun önemli olduğu sensör uygulamalarında ve voltmetreler ile ampermetreler gibi cihazlarda kullanılır. Başka bir deyişle, entegre ADC’nin örnekleme hızı nispeten düşüktür, ancak doğruluğu çok yüksektir.

sınıflandırma

Çeşitli türlerde integral ADC'ler mevcuttur; bunlardan yaygın olanları tek ve çift eğimli integral ADC'lerdir. Bir "eğim" eklenmesi, dönüştürme süresinden ödün verilerek hassasiyeti artırır.

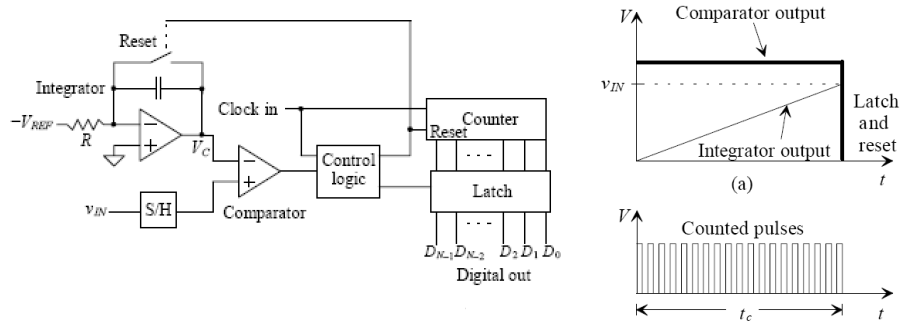

tek eğimli entegre ADC

Karşılaştırıcı, giriş gerilimini entegre referans geriliminin değeriyle karşılaştırır (op-amp’ın ters çeviren girişine bağlı olduğu için bu değeri negatif yapacağımızı unutmayın). Aynı anda saat döngülerinin sayısını da sayar. Entegratörün çıkışı eşit olduğunda, karşılaştırıcı bir mantıksal "0" çıkarır; bu da sayacın ve entegratörün sıfırlanmasını tetikler ve kilit, dijital çıkışı sabitler.

VINVREFVrefVrefVin

Bu, dönüştürme süresidir. Bu integral ADC'nin neden yavaş olduğunu biliyorum. En kötü durumu ele alalım: giriş voltajının , olduğunu ve bunun 20 bitlik bir ADC olduğunu varsayalım, o zaman!

VIN=VREFTCLK=1ustc=220us=1048576us

tek eğimli entegre ADC

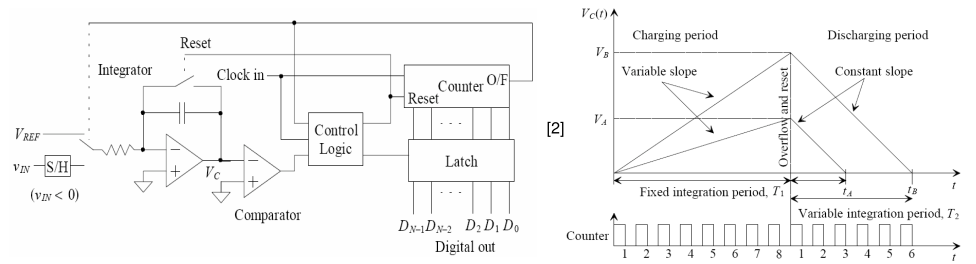

Çift eğimli bir ADC, tek eğimli bir ADC’den, artık toprağa karşı karşılaştırma yapıldığı ve iki voltaj toplamının entegre edildiği yönünden farklılık gösterir. Başlangıçta, negatif giriş entegratöre bağlanır ve bu, sayıcı taşana kadar artar. Ters çeviren girişte entegrasyon negatif bir değere geçtiğinden, entegratör çıkışı her zaman pozitif ve sıfırdan büyük olacaktır, bu nedenle sayaç taşana kadar çalışmaya devam eder ve bu işlem 2N saat döngüsü (=T1) sürer.

VCVREFVINVC

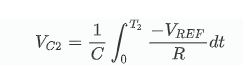

T2 anında, bu değer ile 'nin toplamına eşit olacak ve

VC=VC1+VC2=0

Ancak:

VIN/VREF=T2/T1

Bu nedenle, ADC dönüşüm prensibine göre, çift eğimli ADC tek eğimli ADC'den daha yavaştır; entegrasyon iki kez gerçekleştirildiği için entegratörün eğimiyle ilgili hata ortadan kalkar ve böylece prensipte doğruluk artar.

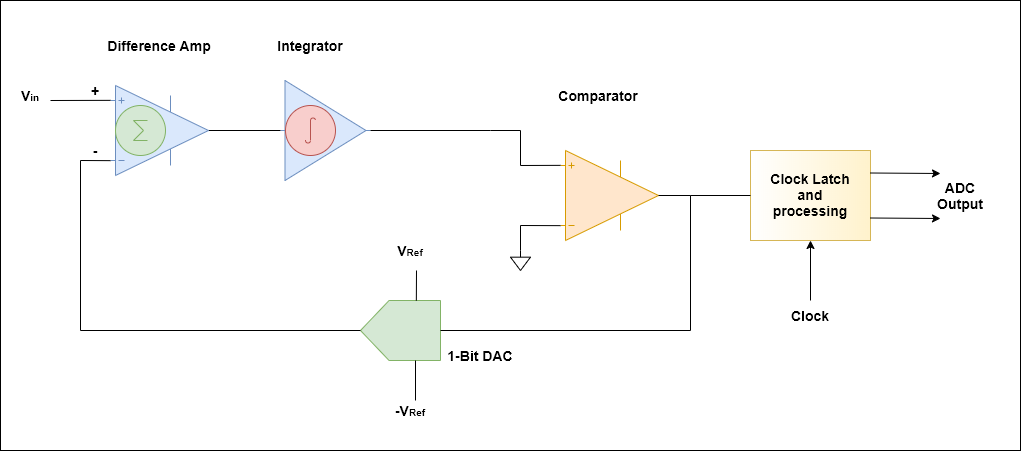

Sigma-Delta Σ-Δ ADC

Girişten başlayarak, fark amplifikatörü Vin ile 1 bitlik DAC çıkışının farkını veren bir çıkış üretir. 1 bitlik bir DAC’nin çıkışı iki değerden biri olabilir: OR . Bu topolojide, bir entegratörün önceki değer ile mevcut giriş değerinin hareketli ortalamasını aldığı düşünülebilir.

–Vref+Vref

Bu nedenle, karşılaştırıcının pozitif segmentinin başlangıçta 0V'nin biraz üzerinde sabit bir değere ayarlandığını varsayarsak, karşılaştırıcı tersine döner. Değeri yüksek veya 1 olacaktır. Ardından, DAC çıkışı olacaktır. Bir sonraki yinelemede, bu değer mevcut değerinden çıkarılacaktır. Önceki değer 0V olduğu için, entegratör çıkışı artık – Vref olacaktır. Bu noktada, karşılaştırıcı çıkışı 0 ve DAC çıkışı olacaktır.

+VrefVin-Vref

Bir sonraki örneklemede, önceki değer nedeniyle entegratör çıkışı 0 olacak ve fark amplifikatörü aslında –Vref'i çıkaracak, böylece –Vref'e eklenecektir. Karşılaştırıcı çıkışı 1 olacaktır.

-Vref-Vref+VrefVin

Bu süreç yinelemeli olarak devam eder, bu nedenle 0V girişi için karşılaştırıcı çıkışı 101010… şeklinde sabit bir akış olacaktır. Mantık 1'in anlamına geldiğini, mantık 0'ın anlamına geldiğini unutmayın; bu nedenle, N örnek örneklenip ortalaması alınırsa, ortalama değerin 0V olduğu kolayca görülebilir. Karşılaştırıcıdan sonraki işleme bloğu, ( ~ ) veya 2 x referans değeri varsayımıyla bunu tek bir değer olan 0000… olarak çıkaracaktır.

+Vref-Vref-Vref+VrefVref

Şimdi, 1V varsayarsak, bu bir 5V ADC'dir. ±2,5V'dir. Daha önce olduğu gibi aynı adımları tekrar tekrar uyguladığımızda, çıkış şöyledir: 1011101… Çıkış 1,07V'dir.

Vin±Vref

Özetle:

Bir sigma-delta ADC, işlenmekte olan sinyali aşırı örnekler (bu kavram için bkz. Analog-Dijital Örnekleme) ve işlenecek sinyali alçak geçiren filtreden geçirir. Genellikle, filtreden sonra Flash ADC kullanılarak dönüştürülen bit sayısı, gerekli bit sayısından daha azdır. Ortaya çıkan sinyal, FLASH’ın ayrık seviyelerinden kaynaklanan hatalarla birlikte geri beslenir, girişten çıkarılır ve filtreye gönderilir. Bu negatif geri besleme, gürültüyü sönümler, böylece istenen sinyal frekansında ortaya çıkmaz. ADC'den sonraki bir dijital filtre (decimation filtresi kullanılarak), örnekleme hızını azaltır, istenmeyen gürültü sinyallerini filtreler ve çıkış çözünürlüğünü artırır (bu nedenle sigma-delta modülasyonu olarak adlandırılır; delta-sigma modülasyonu olarak da bilinir).

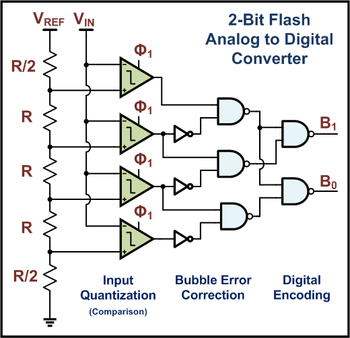

Flash ADC (doğrudan karşılaştırma tipi)

FLASH ADC'nin çalışma prensibi, anlaşılması en kolay olanı olabilir. Aşağıdaki şekil, iki bitlik bir ADC'nin şematik diyagramını göstermektedir. Bu devre, her biri bir önceki referans değerinden bir bit daha yüksek bir referans gerilime sahip olan çok sayıda karşılaştırıcıdan oluşur. Dolayısıyla, 8 bitlik bir ADC için 256 adet bu tür karşılaştırıcıya ihtiyaç duyulur. 10 bitlik bir ADC için ise 1024 adet gereklidir.

LASH ADC (doğrudan karşılaştırma tipi) hızlıdır. Giriş sinyalini herhangi bir örnekleme veya yoğun son işlemden geçirmeden doğrudan dönüştürür. Sorun şu ki, çok sayıda karşılaştırıcı gerektirir ve bu kadar çok karşılaştırıcı, çip üzerinde oldukça fazla silikon alanı kaplar. Bu nedenle, LASH ADC’leri yalnızca diğer ADC uygulamalarıyla elde edilemeyen son derece yüksek hızlara ihtiyaç duyduğunuzda kullanın.

Donanımda somutlaşan ikilem

Pratik uygulamalarda, daha yaygın olarak kullanılan başka bir varyant daha vardır: yarı-FLASH ADC. Bu yöntem, gerçek dönüştürme zincirinde gereken dönüştürücü sayısını azaltmak için iki aşamalı bir süreç kullanır:

İlk olarak, giriş sinyali tam olarak ortada bulunan seviye grubuyla karşılaştırılır. Eğer daha düşükse, en önemli bit (MSB) 0 olarak ayarlanır ve giriş, geri kalan bitleri dönüştürmek üzere referans voltajı ayarlanmış bir karşılaştırıcı zincirine beslenir.

Giriş sinyali bu seviyenin üzerindeyse, MSB 1'e ayarlanır ve giriş sinyalinden çıkarılır. Kalan bitleri elde etmek için karşılaştırıcı zinciri tekrar kullanılır. Yani, özünde, yarı adımlı FLASH ADC, karşılaştırıcının yarısını tasarruf etmek için fazladan bir karşılaştırmadan vazgeçer. Bu tür bir düşünce, 4 noktalı FLASH ADC gibi örneklerle de devam ettirilebilir ve genişletilebilir.

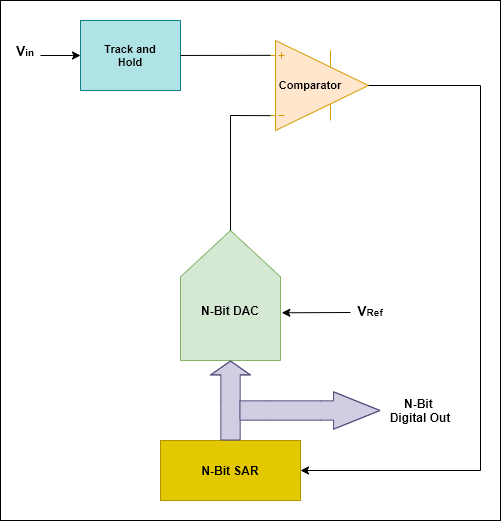

Art arda yaklaşma kaydı (SAR)

Sıralı Yaklaşım Kaydı (SAR), sıralı yaklaşımlı ADC'nin ayrılmaz bir parçasıdır. Bu sistem, bir karşılaştırıcı kullanarak giriş voltajının bulunduğu aralığı kademeli olarak daraltır. Bunu gerçekleştirmek için dönüştürücü, giriş voltajını genellikle seçilen voltaj aralığının ortasını gösteren bir dijital-analog dönüştürücünün çıkış değeriyle karşılaştırır. Sürecin her adımında, tahmin SAR'da saklanır.

Örneğin, giriş voltajının 6,3 V ve başlangıç aralığının 0 ila 16 V olduğunu varsayalım.

- İlk adımda, 8 V (0-16 V aralığının orta noktası) ile karşılaştırmak üzere 6,3 V giriş yapılır. Karşılaştırıcı, 8 V'tan daha düşük bir giriş voltajı bildirir, bu nedenle SAR, aralığı 0 – 8 V'a düşürmek üzere güncellenir.

- İkinci adımda, giriş voltajı 4 V (0 – 8 V aralığının orta noktası) ile karşılaştırılır; karşılaştırıcı, giriş voltajının 4 V'nin üzerinde olduğunu bildirir, bu nedenle SAR, giriş voltajının 4 – 8 V aralığında olduğunu yansıtacak şekilde güncellenir.

- Üçüncü adımda, giriş voltajı 6 V (4 V ile 8 V'nin ortası) ile karşılaştırılır; karşılaştırıcı, giriş voltajının 6 V'den büyük olduğunu bildirir ve arama aralığı 6 – 8 V olur.

İstenen çözüme ulaşana kadar bu adımları tekrarlayın. Topolojisi aşağıdaki gibidir:

Bir fikir edinmek için aşağıdaki animasyona bakın:

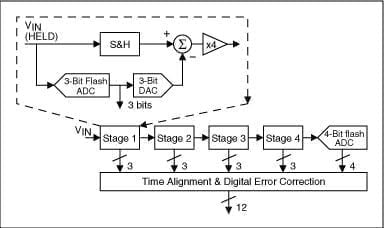

Kademeli ADC

Bir ardışık işlemli ADC (alt yordam niceleyici olarak da bilinir), iki veya daha fazla ardışık işlem hattı kullanır. İlk olarak, kaba bir dönüştürme yapılır. İkinci adımda, giriş sinyalindeki farkı belirlemek için bir dijital-analog dönüştürücü (DAC) kullanılır. Bu fark daha sonra daha hassas değerlere dönüştürülür ve sonuçlar son adımda birleştirilir. Bu, geri besleme referans sinyalinin sadece bir sonraki en önemli bitten ziyade tüm bit aralığı (örneğin, 4 bit) üzerindeki ara geçişlerden oluştuğu ardışık yaklaşım ADC'lerine göre bir gelişme olarak kabul edilebilir. Ardışık yaklaşım yöntemi ile flash ADC'nin avantajlarını birleştiren bu tip, yüksek hız, yüksek çözünürlük ve küçük kalıp boyutu gibi avantajlara sahiptir.

Bu şemada, analog giriş VIN önce bir örnekleme ve tutma (S&H) devresi tarafından örneklenip sabit tutulurken, birinci kademedeki flash ADC bu değeri üç bitlik bir sayıya dönüştürür. 3 bitlik çıkış daha sonra 3 bitlik bir DAC'ye (12 bitlik hassasiyet) beslenir ve analog çıkış, girişten çıkarılır. Bu "kalan" değer 4 kat büyütülür ve bir sonraki aşamaya (aşama 2) gönderilir. Bu eklenen kalıntı, boru hattının alt aşamalarında devam eder ve her aşamada 3 bit sağlar, ta ki son 4LSB bitini çözecek olan 4 bitlik flash ADC'ye ulaşana kadar. Her aşamadaki bitler farklı zaman noktalarında belirlendiğinden, aynı örneğe karşılık gelen tüm bitler, dijital hata düzeltme mantığına beslenmeden önce kaydırma kaydıyla zaman uyumlu hale getirilir. Bir boru hattı, giriş örneklerini işlemeyi, bu boru hattı için toplama bitini belirlemeyi ve kalıntıyı bir sonraki boru hattına aktarmayı tamamladığında, her boru hattına gömülü örnek tutucudan alınan bir sonraki örneği işlemeye başlayabilir. Bu boru hattı işleme, yüksek verimin nedenidir ve aynı zamanda boru hattı işleme kavramının da temelini oluşturur.

Diğerleri

Yukarıda sayılan yaygın ADC türlerinin yanı sıra, yük dengesi prensibine dayalı ADC'ler, zaman paylaşımlı ADC'ler, FM ADC'ler, zaman uzatmalı ADC'ler, artımlı kodlamalı ADC'ler, Wilkinson ADC'ler vb. de bulunmaktadır.

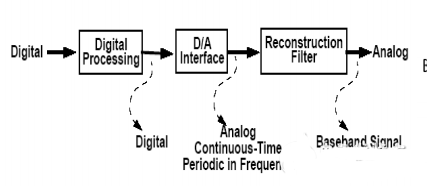

Dijital-Analog Dönüştürücü (DAC)

DAC'nin tanımı

Dijital sistem tarafından işlenen dijital değerin, pratik kullanım amacıyla bazen analog bir değere dönüştürülmesi gerekir. Bu dönüşüme "dijital-analog dönüşümü" denir. Dijital-analog dönüşümünü gerçekleştiren devreye dijital-analog dönüştürücü veya kısaca DAC (Digital to Analog Converter) denir.

DAC parametreleri

Karar

DAC'deki çözünürlük, farklı giriş dijital kod değerleri altında elde edilebilen tüm olası analog çıkış seviyelerinin sayısı olarak tanımlanır. N-bitlik çözünürlük, DAC'nin 2^(N−1) farklı analog seviye üretebileceği anlamına gelir. Genel olarak, bu değer giriş dijital kodunun basamak sayısını ifade eder.

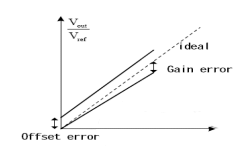

Ofset ve kazanç hataları

Ofset, 0 kod değeri girdiğinde elde edilen gerçek analog çıkış sinyalinin değeri olarak tanımlanır; kazanç hatası ise, şekilde gösterildiği gibi, ideal tam ölçek çıkış değeri ile ofset düşüldükten sonraki gerçek çıkış değeri arasındaki fark olarak tanımlanır.

Doğruluk

DAC'deki doğruluk, mutlak doğruluk ve göreceli doğruluk olarak ikiye ayrılır. Mutlak doğruluk, çeşitli ofset ve doğrusal olmayan hatalar da dahil olmak üzere ideal çıkış ile gerçek çıkış arasındaki fark olarak tanımlanır. Göreceli doğruluk ise maksimum integral doğrusal olmayan hata olarak tanımlanır. Doğruluk, tam ölçeğin bir oranı olarak ifade edilir ve etkin basamak sayısı cinsinden belirtilir. Örneğin, 8 bitlik doğruluk, DAC'nin hatasının DAC'nin tam ölçekli çıkışının 1/8'inden az olduğu anlamına gelir. Doğruluk kavramının çözünürlükle ilgili olmadığına dikkat edin. 12 bitlik çözünürlüğe sahip bir DAC, yalnızca 10 bitlik doğruluğa sahip olabilir; 10 bitlik çözünürlüğe sahip bir DAC ise 12 bitlik doğruluğa sahip olabilir. Çözünürlük üzerindeki doğruluk, DAC'nin iletim tepkisinin daha hassas bir şekilde kontrol edilebileceği anlamına gelir.

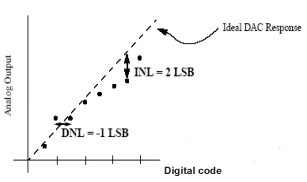

INL - Tam Doğrusal Olmama

Ofset ve kazanç hataları ortadan kaldırıldığında, integral doğrusallık hatası, gerçek çıkış aktarım karakteristiğinin ideal aktarım karakteristiğinden (düz bir çizgi) sapması olarak tanımlanır. Resimde görüldüğü gibi.

DNL - Diferansiyel Doğrusal Olmama

Analog çıkıştaki her bir değişiklik için en az 1 LSB değerine sahip ideal bir DAC'de, diferansiyel doğrusallık hatası, minimum analog çıkış değişikliği başına 1 LSB değerinden sapma olarak tanımlanır (kazanç hatası ve ofset hariç). Tanımladığımız DNL, her bir dijital giriş kod değeri içindir ve bazen en büyük DNL, tüm DAC'nin DNL'sini tanımlamak için kullanılır. İdeal bir DAC, her dijital giriş için sıfır diferansiyel doğrusallık hatasına sahipken, maksimum DNL değeri 0,5 LSB olan bir DAC, çıkış başına 0,5 LSB ile 1,5 LSB arasında minimum çıkış değişikliğine sahip olacaktır. DAC'nin integral ve diferansiyel doğrusallık hataları şekilde gösterilmiştir.

Titreşim enerjisi (Glitch Darbe Alanı)

Giriş sinyalinin değişmesinden sonra çıkışta ortaya çıkan titreşimin kapladığı maksimum alan.

Yerleşim Süresi

Yerleşim süresi, son değerin belirli bir hata aralığı içinde yer alır ve çıkışın tam ölçek dönüşümüne ulaşması için gereken süredir.

Monotonluk Monoton bir DAC, giriş dijital kod değeri arttıkça çıkış analog seviyesinin her zaman arttığı bir DAC'dir. Maksimum DNL 0,5 LSB içinde kontrol edilirse, DAC'nin monotonluğu doğal olarak garanti edilebilir.

Sahte Dinamik Aralık (SFDR) SFDR, Sahte İçermeyen Dinamik Aralık, yani gürültü ve harmonik içermeyen dinamik aralıktır. Hem gürültü hem de harmonikler sahte sinyaller olarak adlandırılır.

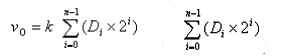

DAC İlkesi

Her bir giriş ikili kodunu ağırlığına göre karşılık gelen bir analog değere dönüştürün ve ardından her bir biti temsil eden analog değerleri toplayın; elde edilen toplam analog değer, dijital değerle orantılıdır; böylece dijital değerden analog değere dönüştürme işlemi gerçekleştirilir.

Bu, bit ağırlığı genişletme yoluyla ikili sayıya dönüştürülmüş ondalık değerdir.

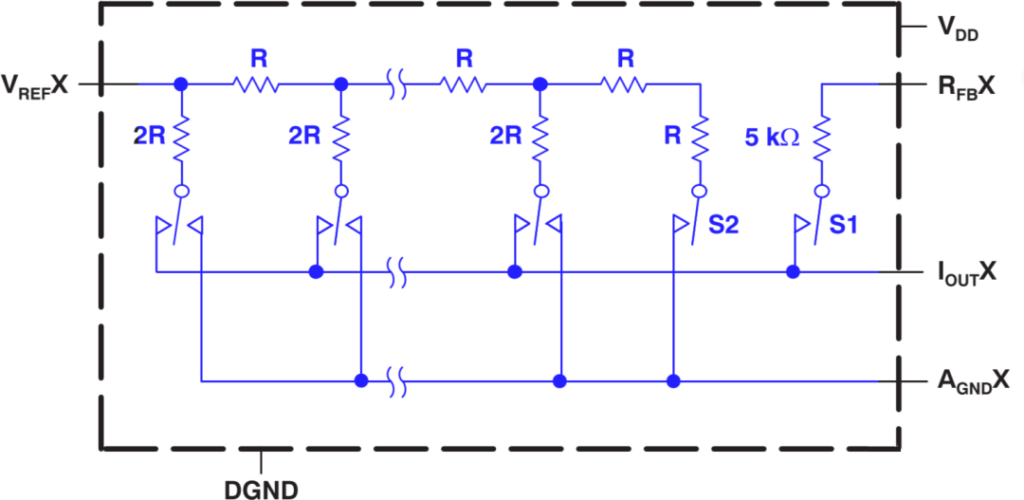

DAC'nin yapısı ve özellikleri

DAC temel olarak dijital kayıtlar, analog elektronik anahtarlar, bit ağırlık ağı, toplama işlemsel amplifikatörü ve referans gerilim kaynağından (veya sabit akım kaynağından) oluşur. Dijital kayıtta depolanan dijital miktarların basamaklarını, karşılık gelen basamakların analog elektronik anahtarlarını sırasıyla kontrol etmek için kullanın, böylece 1 basamaklı basamak, basamak ağırlık ağında basamak ağırlığına orantılı bir akım değeri üretir ve ardından işlemsel amplifikatör, toplanan ve bir voltaj değerine dönüştürülen her akım değerini kontrol eder.

Değişken bit ağırlık ağları, ağırlık direnç ağı DAC, R-2R ters T şekilli direnç ağı DAC ve tek değerli akım tipi ağ DAC gibi birçok DAC türünün montajını mümkün kılar. Ağırlıklı direnç ağı DAC tarafından üretilen dönüşümün hassasiyeti, referans voltajı VREF'in doğruluğuna, analog elektronik anahtarların, işlemsel amplifikatörlerin ve ağırlıklı direnç değerlerinin kalitesine bağlıdır. Dezavantajı, her bir ağırlık direncinin direnç değerlerinin farklı olması ve çok sayıda basamak olduğunda direnç değerlerinin büyük ölçüde değişmesidir; bu da, özellikle entegre devrelerin üretimi için doğruluğu sağlamayı oldukça zorlaştırır. Bu nedenle, entegre DAC'lerde bu devre nadiren tek başına kullanılır.

DAC'nin başlıca teknik göstergeleri

DAC'nin dönüştürme doğruluğu ve dönüştürme hızı: DAC'de dönüştürme doğruluğu genellikle çözünürlük ve dönüştürme hatası ile ifade edilir.

Karar

Genel olarak, çözünürlüğü ölçmek için DAC'nin bit sayısı kullanılır; çünkü bit sayısı ne kadar fazla olursa, çıkış gerilimi vO'nun değer sayısı (2n) o kadar artar ve çıkış gerilimindeki ince değişiklikleri o kadar iyi yansıtabilir.

Ayrıca, çözünürlük, DAC'nin ayırt edebileceği minimum çıkış voltajı 1 LSB ile maksimum çıkış voltajı FSR arasındaki oranla da tanımlanabilir. Bu oran şöyledir:

çözünürlük=1LSB/FSR=k/k(2n-1)=1/(2n-1)

Değer ne kadar küçükse, çözünürlük o kadar yüksek olur.

Dönüştürme hatası

Dönüştürme hatası, gerçek çıkış analog voltajı ile ideal değer arasındaki maksimum sapmadır. Genellikle bu maksimum sapmanın FSR’ye oranının yüzde olarak veya birkaç LSB cinsinden ifade edilir. Aslında, bu üç hatanın kapsamlı bir göstergesidir.

Dönüşüm hızı

Dönüşüm hızı genellikle yerleşme süresi ile belirlenir. Giriş sinyalinin tamamı 0'dan tamamı 1'e dönüştüğü andan itibaren, çıkış voltajının FSR±½ LSB aralığı (veya FSR±x%FSR ile belirtilen aralık) içinde sabitlenmesine kadar geçen süreye yerleşme süresi denir. Bu süre, DAC'nin maksimum tepki süresidir; dolayısıyla dönüşüm hızını ölçmek için bu süre kullanılır.

DAC Türleri

Direnç tipi

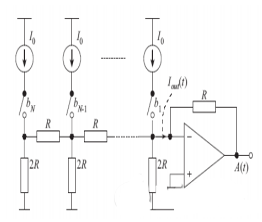

Yapı Şekil 1'de gösterilmiştir. Şekil 1'de gösterilen, bir R-2R merdiven ağı tipi dönüştürücüdür. Bunun avantajı, çok iyi bir doğrusallık sağlayabilmesidir. Tüm akım kaynakları eşdeğer olduğundan, aralarındaki hatayı azaltmak için özel ek teknolojiler kullanabiliriz ve yapısı direnç bölücüsünkinden çok daha basittir. Dezavantajı ise direncin her zaman doğrusal olmaması ve sinyalle ilgili parazitik kapasitans içermesidir, bu nedenle tam eşleşmeyi sağlamak zordur. Aynı zamanda, hız çıkış tamponuyla sınırlıdır ve çok yüksek olamaz.

Kapasitif tip

Yapı Şekil 2'de gösterilmiştir. En yüksek mertebeden kapasitans CN, en düşük mertebeden kapasitans C1'in 1 2N− katıdır. Avantajı, güç tüketiminin az olması ve eşleştirme doğruluğunun dirençinkinden daha yüksek olmasıdır. Başlıca sınırlayıcı faktörler, kapasitörlerin uyumsuzluğu, anahtarların açık direnci, büyük RC gecikmeleri ve amplifikatörün sınırlı bant genişliğinin DAC'nin hızı üzerindeki etkisidir. Yük dağıtıcı DAC'lerin en büyük dezavantajı, CMOS işlemlerinde kapasitörlerin uygulanması için çok fazla yonga alanı kaplamasıdır. Son olarak, CMOS işlemindeki kapasitans doğası gereği doğrusal olmadığından, genel DAC'nin doğrusallığı bastırılacaktır. Orta ve geniş bant yüksek hassasiyet için uygundur.

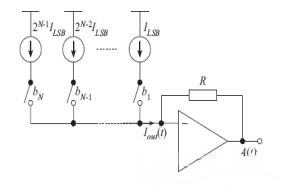

Akım türü

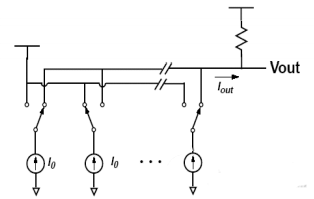

Yapı Şekil 3'te gösterilmiştir. Bunun avantajı, doğruluk 10 bitten az olduğunda alanın çok küçük tutulabilmesi ve hızın amplifikatörün bant genişliği ve büyük RC gecikmesi tarafından sınırlanmamasıdır. Çok yüksek bir hıza ulaşabilir. Tüm akım doğrudan çıkış terminaline aktığı için enerji tüketimi oldukça verimlidir ve uygulaması kolaydır. Dezavantajları, cihaz uyumsuzluğuna duyarlılık ve sınırlı akım kaynağı çıkış empedansıdır. Yüksek hızlı geniş bant gereksinimleri için uygundur.

Şekil 4'te gösterildiği gibi, çıkış için bir işlemsel amplifikatör kullanmamak ve akımı voltaj çıkışına dönüştürmek için doğrudan yük direncini kullanmak da mümkündür. Bu form, DAC'nin hızının op amp'ın bant genişliği ile sınırlanmamasını sağlar.

Tipik çarpma

Bazı DA dönüştürücüler sabit bir referans gerilimi kullanırken, bazıları ise referans gerilimi girişine bir AC sinyali ekler. İkincisi, dijital giriş ile referans gerilimi girişinin çarpımının sonucunu elde edebildiği için çarpma tipi DA dönüştürücü olarak adlandırılır. Genel olarak, çarpma tipi bir DA dönüştürücü sadece çarpma işlemi gerçekleştirmekle kalmaz, aynı zamanda bir giriş sinyalini dijital olarak zayıflatmak için zayıflatıcı ve bir giriş sinyalini modüle etmek için modülatör olarak da kullanılabilir.

Bir DA dönüştürücü

Az önce bahsedilen dönüştürme sisteminin aksine, bir DA dönüştürücü, dijital değerleri darbe genişlik modülasyonuna veya frekans modülasyonuna dönüştürmek için özel bir yöntem kullanır; bu sinyal daha sonra bir dijital filtre ile düzeltilerek ses vb. uygulamalar için yaygın olarak kullanılan bir voltaj çıkışı (bit akışı modu olarak da bilinir) elde edilir.

Sonuç

ADC ve DAC dönüştürücüler, her türlü dijital sistemin iki temel bileşenidir. Bu bileşenler, analog sinyalleri dijital sinyallere ve tersi yönde dönüştürmeye yardımcı olur. ADC (Analog-Dijital Dönüştürücü) analog bir sinyali alarak onu dijital sinyale dönüştürürken, DAC (Dijital-Analog Dönüştürücü) dijital bir sinyali alarak onu analog sinyale dönüştürür. Bu iki bileşen de ses ve görüntü işlemeden veri aktarımına kadar çok çeşitli uygulamalar için önemlidir. Bu makalede, bu dönüştürücülerin nasıl çalıştığını ve farklı uygulamalardaki önemini ele aldık. Ayrıca, farklı dönüştürücü türlerini, dönüştürebildikleri farklı sinyal türlerini ve her türün avantaj ve dezavantajlarını da inceledik.