SWD ve JTAG, Cortex-M tabanlı MCU'lar için yaygın olarak kullanılan hata ayıklama arayüzleridir. Ancak bu iki arayüz, hem yapısı hem de kullanım alanları açısından birbirinden farklıdır. Bu makalede, bu arayüzlerin pinlerini, çalışma prensiplerini, avantajlarını ve dezavantajlarını ele alacağız.

SWD Arayüzü

SWD (Serial Wire Debug), ARM tarafından mikrodenetleyicilerinin programlanması ve hata ayıklaması için tasarlanmış bir protokoldür. ARM CoreSight hata ayıklama mimarisine dayanır ve veri paketleri aracılığıyla yonga kayıtlarının okunmasını ve yazılmasını sağlar. SWD, ARM hata ayıklama arayüzlerine erişim için kullanılan iki telli bir protokoldür. ARM Hata Ayıklama Arayüzü Mimari Spesifikasyonu'nun bir parçasıdır ve JTAG'a alternatif olarak kullanılır. PCB düzeninin sınırlı olduğu ve pin kaynaklarının kısıtlı olduğu durumlarda SWD iyi bir seçimdir. Piyasadaki birçok hata ayıklayıcı, ST-Link, J-Link, e-Link, GD-Link ve diğerleri gibi SWD hata ayıklama arayüzlerini destekler.

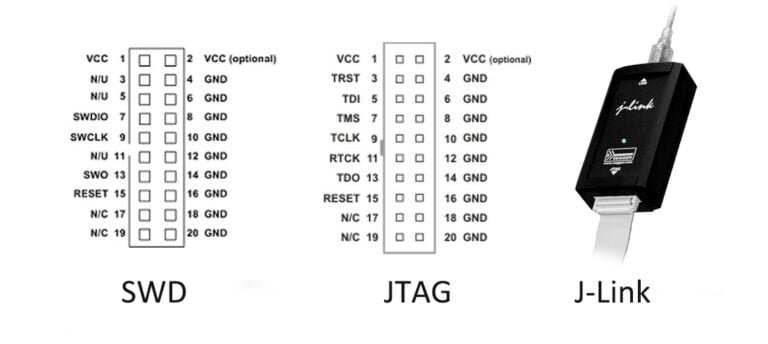

SWD Pimleri

SWDIO: Seri Veri Giriş Çıkışı, seri veri giriş ve çıkış pini

SWCLK: Seri Veri Saati, seri hat saat pini

SWDIO, çift yönlü (giriş ve çıkış) bir veri pini olup, devre kartında hattın çekilmesi gerekir (ARM 100 K önerir).

SWD nasıl çalışır?

Hata ayıklama probları gibi harici aygıtlar, Seri Hata Ayıklama Bağlantı Noktasına (SW-DP) doğrudan erişmek için SWDIO/SWCLK'ye bağlanır. SW-DP, bir veya birden fazla Erişim Bağlantı Noktasına (AP) erişebilir ve AP'ler aracılığıyla sistemin geri kalan kayıtlarına erişilebilir. Cortex M serisi CPU'lar için önemli bir AP, dahili AHB veriyolunda ana bilgisayar görevi gören AHB-AP'dir. Diğer bir deyişle, AHB-AP dahili çekirdeğin bellek haritasına erişebilir. Dahili flash, SRAM, hata ayıklama bileşenleri ve çevresel aygıtların tümü bellek haritasına alındığından, AHB-AP programlama dahil olmak üzere tüm aygıtı kontrol edebilir. Tüm SWD işlem süreci hiyerarşiktir; saat sinyalleri SWCLK pininden, veri sinyalleri ise SWDIO pininden girilir. Başlangıçta, hata ayıklayıcı AP kayıtlarının parametrelerini belirlemek için SW-DP üzerinde çalışır ve Cortex Bellek Haritasının değiştirilmesine olanak tanır.

SWD'nin Avantajları

- Azaltılmış Sinyal Sayısı

- Yüksek Hızlarda Güvenilirlik

- Arıza Olasılığı Azalır

- JTAG Simülasyonlarıyla Uyumluluk

- Çalışma için daha az pin gerektirir

JTAG Arayüzü

JTAG (Joint Test Action Group), başlangıçta yongaları test etmek için kullanılıyordu. Bu grup, 1980’lerin sonlarında görüşmelere başladı ve 1990 yılında IEEE standartlarını yorumlayan belgeleri resmi olarak yayınladı. (IEEE, WiFi ve Bluetooth gibi standartları yayınlamaktan sorumlu uluslararası bir kuruluş olan Elektrik ve Elektronik Mühendisleri Enstitüsü’nün kısaltmasıdır.) Önerdikleri protokol, 1990 yılında IEEE 1149.1'de belgelendi. Bu belge o zamandan beri revizyonlara ve iyileştirmelere tabi tutuldu; bu yazının yazıldığı tarihteki en son standart IEEE 1149.7'dir.

JTAG Pimleri

- TDI: Test Verisi Girişi, bir seri giriş pini.

- TDO: Test Verisi Çıkışı, bir seri çıkış pini.

- TCK: Test Saati, bir saat pini.

- TMS: Test Modu Seçimi, bir mod seçimi (kontrol sinyali) pini.

- TRST: Test Sıfırlama, bir sıfırlama pini.

JTAG Nasıl Çalışır?

JTAG prensibi, cihaz içinde bir Test Erişim Noktası (TAP) tanımlanmasını içerir. Bu, özel JTAG test araçları kullanılarak dahili düğümlerin test edilmesini sağlar. JTAG testi, birden fazla cihazın bir JTAG arabirimi üzerinden seri olarak bağlanmasına olanak tanıyarak, tek tek cihazların test edilmesi için bir JTAG zinciri oluşturur. Günümüzde JTAG arabirimleri, FLASH cihazlarının programlanması gibi Sistem İçi Programlanabilir (ISP) işlemler için de yaygın olarak kullanılmaktadır. Donanım yapısı açısından JTAG arabirimi iki bölümden oluşur: JTAG portu ve denetleyici. JTAG arabirimiyle uyumlu cihazlar, mikroişlemciler (MPU'lar), mikrodenetleyiciler (MCU'lar), PLD'ler, CPLD'ler, FPGA'lar, DSP'ler, ASIC'ler veya IEEE 1149.1 spesifikasyonlarına uygun diğer yongalar olabilir. IEEE 1149.1, dijital entegre devre yongasının her pini için Sınır Tarama Birimi (BSU) adı verilen bir kaydırma kayıt biriminin bulunmasını zorunlu kılar. Bu birim, JTAG devresini çekirdek mantık devresine bağlarken, çekirdek mantık devresini yonganın pinlerinden izole eder. Yonganın tüm Sınır Tarama Birimleri, Sınır Tarama Kaydını (BSR) oluşturur. Sınır Tarama Kaydı devresi yalnızca JTAG testi sırasında aktiftir ve normal çalışma sırasında yonganın işlevselliğini etkilemez.

JTAG protokolü, TMS sinyali aracılığıyla TAP durum makinesinin geçişini kontrol eder. Sistem açıldıktan sonra, TAP denetleyicisi önce Test-Logic Reset durumuna girer, ardından sırasıyla Run-Test/Idle, Select-DR-Scan, Select-IR-Scan, Capture-IR, Shift-IR, Exit1-IR ve Update-IR durumlarından geçer ve ardından Run-Test/Idle durumuna geri döner. Bu süreçte, durum geçişleri TCK sinyali (yükselen kenar) tarafından yönlendirilir ve TAP durumunu seçmek için TMS sinyalleri kullanılır. Capture-IR durumunda, komut kayıtçısına belirli bir mantık dizisi yüklenir; Shift-IR durumunda, belirli bir komut komut kayıtçısına kaydırılabilir; ve Update-IR durumunda, komut kayıtçısına yeni girilen komut, komut kayıtçısını güncellemek için kullanılır. Son olarak, sistem Run-Test/Idle durumuna geri döner; burada komut yürürlüğe girer ve komut ile kayıtlara erişim tamamlanır. Run-Test/Idle durumuna geri döndükten sonra, komut kayıtçısının içeriğine göre gerekli veri kayıtçısı seçilir ve veri kayıtçıları üzerinde çalışmaya başlanır.

JTAG'ın Avantajları

- JTAG, ARM yongalarıyla sınırlı değildir; tanınmış MSP430 gibi ARM dışındaki yongalarda da desteklenmektedir.

- JTAG, programlama, hata ayıklama ve üretim testleri için geniş bir uygulama yelpazesine sahiptir.

- JTAG, protokolün gelişmesiyle birlikte gelişen bağımsız bir gruptur.

Sonuç

JTAG ve SWD, her ikisi de gömülü sistem hata ayıklama açısından önemli arayüzlerdir ve her birinin kendine özgü güçlü ve zayıf yönleri vardır. Hangi arayüzün seçileceği, proje gereksinimlerine, donanım desteğine ve performans ihtiyaçlarına bağlıdır. Karmaşık sistemlerde daha fazla kontrol ve işlevsellik elde etmek için JTAG gerekli olabilirken, kaynak kısıtlamaları olan sistemler için SWD daha uygun bir seçenek olabilir. Bu faktörleri bir bütün olarak değerlendirmek, daha etkili bir gömülü sistem geliştirme ve hata ayıklama süreci için bilinçli kararlar almanıza yardımcı olabilir.