En la era de los servidores con IA, los teléfonos inteligentes 5G y los vehículos autónomos, el rendimiento de un chip depende en gran medida del «sistema nervioso» que lo sustenta: el sustrato del circuito integrado. A medida que la densidad de los circuitos alcanza sus límites físicos, la elección del proceso de fabricación determina la integridad de la señal y la fiabilidad del producto final.

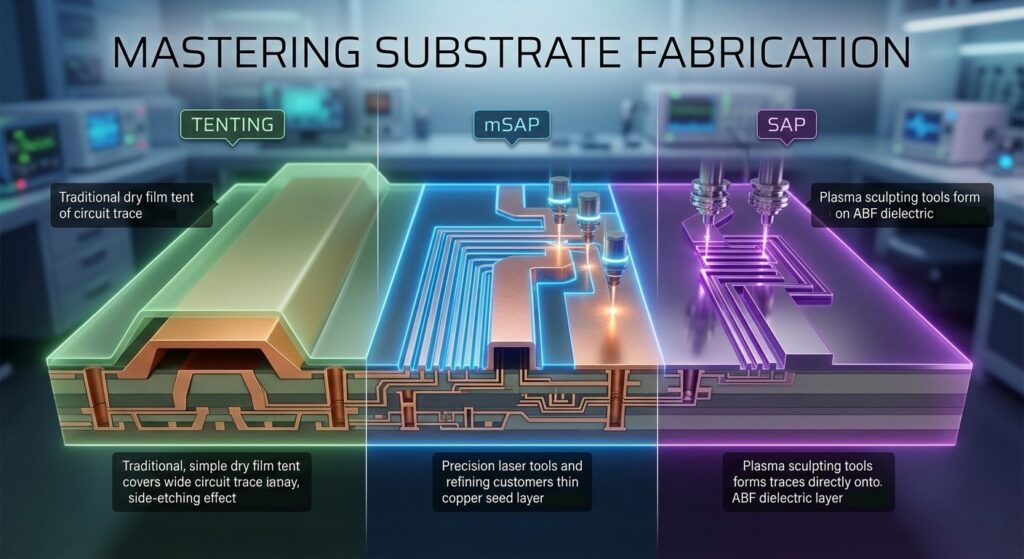

Hoy en día, tres «herramientas de modelado» principales dominan el sector: Tenting (sustractivo), mSAP (proceso semi-aditivo modificado) y SAP (proceso semi-aditivo). Esta guía desglosa sus mecanismos técnicos, sus ventajas e inconvenientes, y dónde encajan en el ecosistema electrónico moderno.

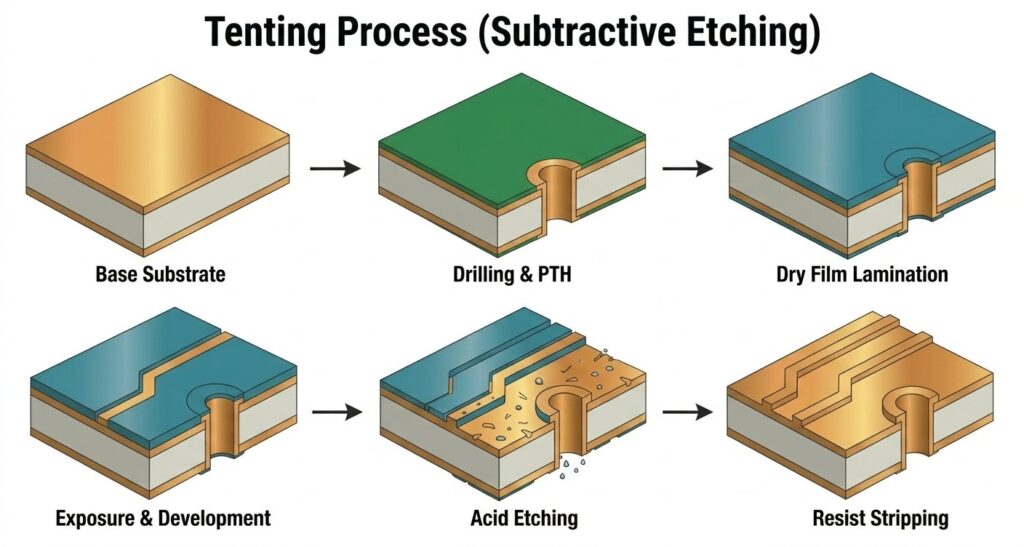

1. Proceso de entintado (método sustractivo)

El proceso de «tenting» es la tecnología de formación de líneas más tradicional y ampliamente utilizada en la industria de los PCB y los sustratos de baja densidad. Su principio básico es «cubrir y eliminar», de forma muy similar a como se talla un sello a partir de un bloque de piedra.

Cómo funciona: Se parte de un laminado revestido de cobre (CCL) con una lámina de cobre gruesa (normalmente > 12 µm). Una película seca (fotoresina) cubre las áreas del circuito deseadas como una «tienda» sobre los orificios (de ahí el nombre). A continuación, el cobre desprotegido se elimina mediante grabado químico.

El problema (grabado lateral): Dado que el grabado elimina el cobre vertical y horizontalmente al mismo tiempo, crea una sección transversal «trapezoidal». Este «grabado lateral» limita la precisión del ancho de línea y el espacio ($L/S$) a aproximadamente $30\mu m/30\mu m$.

Ideal para: Electrónica de consumo estándar, PCB para automoción y sustratos BGA de unión por hilo (WB BGA) tradicionales.

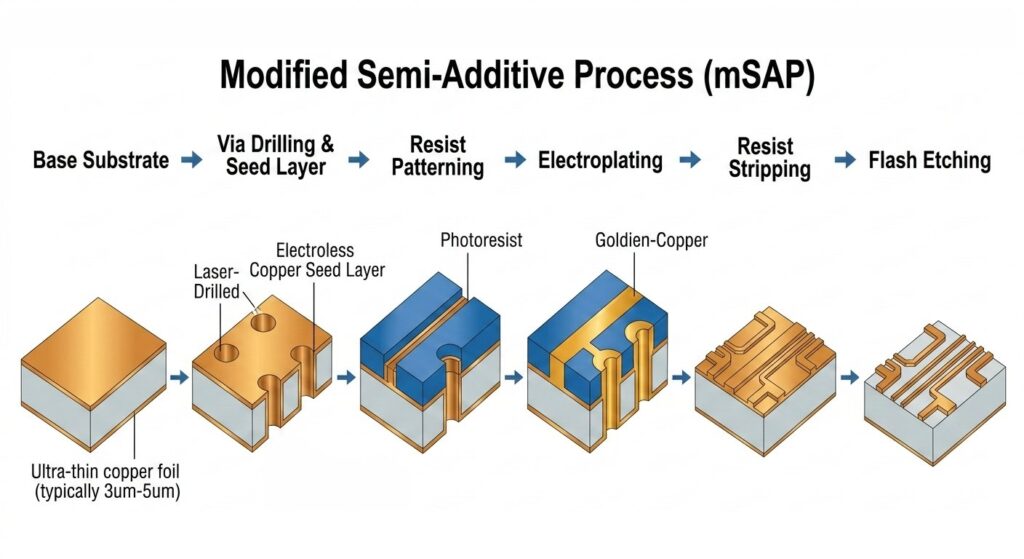

2. mSAP (proceso semi-aditivo modificado)

A medida que aumentaba el número de pines y se aceleraban las señales, el mSAP se impuso como el puente entre las placas de circuito impreso tradicionales y los sustratos de circuitos integrados de alta gama. Actualmente es la opción predominante para los sustratos FCBGA utilizados en chips de red y procesadores de gama alta para teléfonos inteligentes.

Cómo funciona: En lugar de cobre grueso, el mSAP parte de una base de cobre ultrafina (normalmente de 3 a 5 µm) o de una «capa semilla» depositada químicamente. El circuito se «añade» mediante galvanoplastia selectiva hasta alcanzar el grosor deseado.

La ventaja: tras la galvanoplastia, un rápido «grabado flash» elimina la capa base ultrafina. Dado que la base es tan fina, el tiempo de grabado es mínimo, lo que da como resultado paredes de circuito rectangulares casi verticales con capacidades $L/S$ de hasta $10\mu m/10\mu m$.

Ideal para: procesadores de aplicaciones (AP) de smartphones de gama alta (serie A de Apple, Snapdragon), encapsulado a escala de chip (FCCSP) y PCB tipo sustrato (SLP).

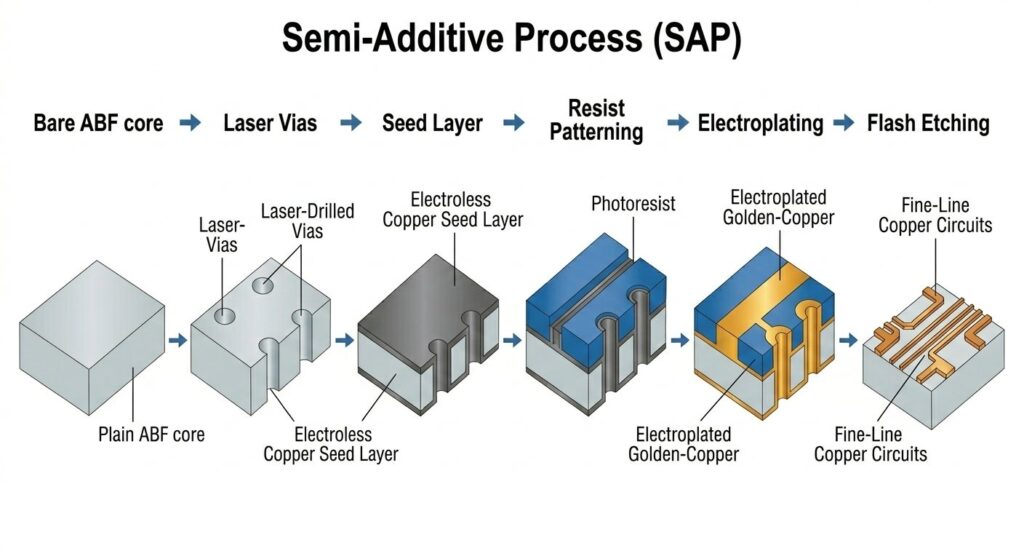

3. SAP (proceso semi-aditivo)

El SAP representa la máxima expresión de la precisión en los circuitos y a menudo se le denomina una versión «purificada» del mSAP. Prescinde por completo de la lámina de cobre en favor de la «adición pura».

Cómo funciona: utiliza un material dieléctrico sin cobre, sobre todo ABF (Ajinomoto Build-up Film). Se deposita químicamente una «capa semilla» microscópica ($< 1\mu m$) sobre la superficie lisa, seguida de un recubrimiento selectivo para construir los circuitos.

Ventaja: dado que la capa de semillas es prácticamente inexistente, el grabado no tiene ningún impacto en la morfología del circuito. Esto permite una precisión extrema ($L/S < 10\mu m$) y un control de impedancia superior para señales de alta velocidad.

Ideal para: Computación de alto rendimiento (HPC), aceleradores de IA (Nvidia H100) y encapsulados avanzados como CoWoS y HBM.

4. Tabla comparativa: Tenting, mSAP y SAP

| Feature | Tenting | mSAP | SAP |

|---|---|---|---|

| Core Principle | Subtractive: Etch away thick copper foil | Additive: Plate over ultra-thin copper base | Pure Additive: Seed layer on copper-free dielectric |

| Line Precision (L/S) | > 30μm | 10μm - 30μm | < 10μm |

| Cross-section Shape | Trapezoidal (Side-etching) | Near-Rectangular | Perfectly Rectangular |

| Base Material | Standard CCL | Ultra-thin copper foil | ABF (Ajinomoto Build-up Film) |

| Primary Application | Consumer PCBs / Motherboards | Smartphone AP / High-end HDI | AI Accelerators / CPU / GPU Substrates |

| Cost & Maturity | Low Cost / Highly Mature | Medium-High / Mainstream High-end | Very High / Cutting-edge |

Mirando hacia el futuro: el futuro de la fabricación

El sector está avanzando hacia un enfoque «híbrido» para equilibrar el coste y el rendimiento, utilizando la técnica «tenting» para las capas centrales y mSAP/SAP para las capas externas de alta densidad. A medida que la demanda de IA amplía los límites de la Ley de Moore, las tecnologías emergentes, como los sustratos de vidrio y los chips integrados, seguirán evolucionando junto con estos tres procesos fundamentales.

Comprender los matices de estos métodos de fabricación es el primer paso para dominar el complejo panorama del encapsulado moderno de chips y la seguridad del hardware.