Las pruebas de circuitos integrados (IC) sirven para detectar si el chip presenta defectos de diseño o defectos físicos causados por el proceso de fabricación. El proceso puede llevarse a cabo utilizando diversos métodos de prueba.

El encapsulado de circuitos integrados es el proceso de encerrar un circuito integrado (IC) en un encapsulado protector. Este proceso protege el IC de daños y garantiza su correcto funcionamiento. También permite la conexión del IC a otros dispositivos y circuitos.

¿Cómo se prueba un circuito integrado con un comprobador de circuitos integrados?

kit de pruebas ic

Hay varios tipos de kits de prueba de circuitos integrados disponibles en el mercado, cada uno diseñado para un propósito específico. Por ejemplo, algunos kits de prueba de circuitos integrados están diseñados para pruebas de uso general. Otros están diseñados para aplicaciones específicas, como circuitos integrados para automóviles o circuitos integrados de potencia.

La mayoría de los kits de pruebas de circuitos integrados incluyen una variedad de accesorios básicos, como un multímetro, sondas, un comprobador digital de circuitos integrados y cables de prueba. Algunos kits también pueden incluir equipos más especializados, como un osciloscopio o un analizador lógico.

Método de prueba

Hay varias formas de probar los circuitos integrados, pero el método más común se llama prueba en circuito (ICT). Este tipo de prueba se hace conectando un dispositivo de prueba al dispositivo que se está probando (DUT). Luego, hacemos una serie de pruebas para ver si funciona bien.

La ICT se puede utilizar para probar tanto circuitos integrados digitales como analógicos. En el caso de los circuitos integrados digitales, el probador envía una serie de señales de entrada al DUT. A continuación, comprueba las salidas para ver si coinciden con los resultados esperados. Los circuitos integrados analógicos se prueban normalmente mediante una técnica denominada prueba dinámica. Durante este proceso, el probador aplica una serie de señales al DUT y, a continuación, mide la respuesta.

Existen diferentes empresas que fabrican probadores ICT, por lo que debe elegir uno que sea compatible con sus circuitos integrados concretos. Una vez que tenga un probador, deberá crear un dispositivo de prueba que se conecte al DUT. El dispositivo de prueba puede aplicar las señales necesarias al DUT y también medir la respuesta.

Una vez que tenga ambos, deberá escribir un programa de prueba para comprobar los resultados. Este proceso puede llevar mucho tiempo, pero es importante para garantizar que sus circuitos integrados funcionan correctamente.

Tipos de pruebas

Prueba de continuidad IC

La prueba de continuidad del IC es sencilla y permite determinar si los IC funcionan correctamente.

Esta prueba se realiza conectando un multímetro al IC y midiendo la resistencia entre los distintos pines.

Si el IC funciona correctamente, la resistencia debe ser baja (normalmente inferior a 10 ohmios). De lo contrario, la resistencia será alta (normalmente superior a 10 ohmios).

prueba de nivel

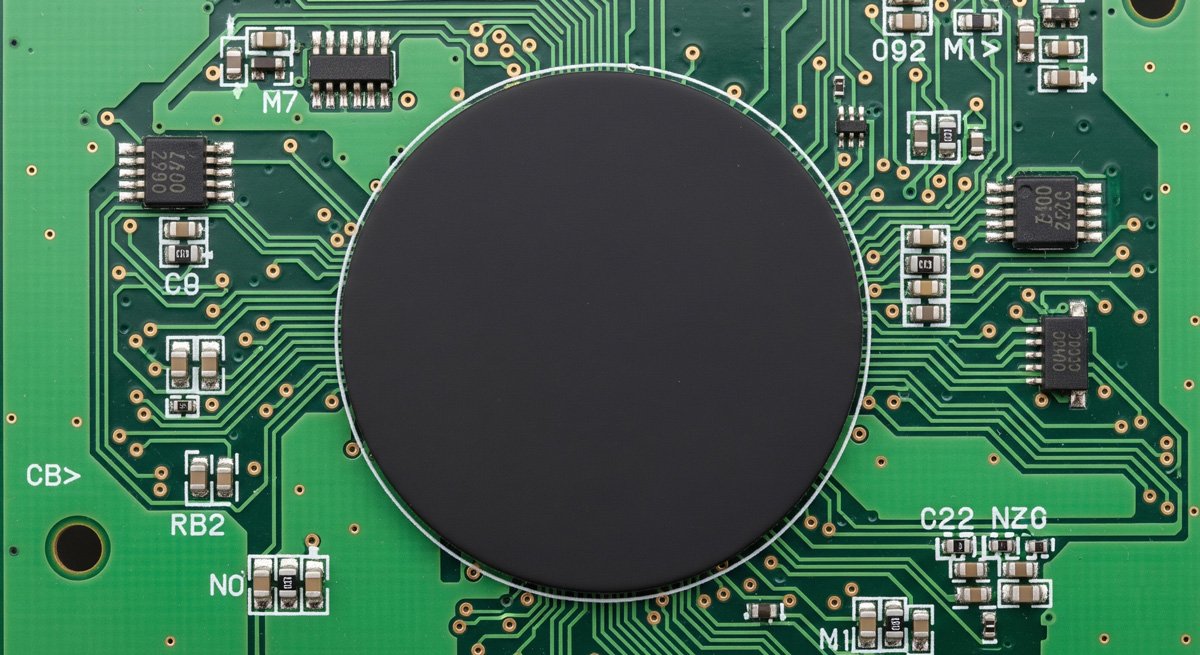

Las pruebas a nivel de circuitos integrados son un tipo de pruebas eléctricas que se realizan para determinar el funcionamiento y el rendimiento de los circuitos integrados (IC).

Estas pruebas se suelen realizar en circuitos integrados que ya están instalados en una placa de circuito.

El objetivo de la prueba es verificar que el IC funciona correctamente y cumple con las especificaciones para el uso previsto.

Existen diversos métodos de prueba para las pruebas a nivel de circuito integrado, entre los que se incluyen las pruebas lógicas, las pruebas funcionales y las pruebas paramétricas.

Vía de desarrollo del encapsulado de circuitos integrados

El embalaje ha pasado aproximadamente por el siguiente proceso de desarrollo:

1. En términos de estructura:

TO → DIP → PLCC → QFP → BGA → CSP → WLP y SiP, etc.

2. Materiales:

Metal, cerámica -> cerámica, plástico -> plástico;

3. Forma de los pines:

Conductores largos en línea -> conductores cortos o sin conductores -> protuberancias esféricas

4. Método de montaje:

Inserción a través de orificio -> Montaje en superficie -> Montaje directo

5. La fuerza motriz de la mejora continua del embalaje:

Tamaño más pequeño, más tipos de chips, más E/S

6. Dificultades:

El proceso es cada vez más complejo y es necesario tener en cuenta la disipación del calor y la conductividad eléctrica, al tiempo que se reduce el volumen.

Características y competitividad básica

1. Sólidos atributos de fabricación

La capacidad de producción depende totalmente de la adquisición de equipos (inversión de capital) y, al igual que la fabricación tradicional, también pasará por un proceso de aumento de la capacidad y optimización de los procesos. La escala conlleva la acumulación de experiencia y las ventajas de una tecnología puntera.

2. La escala del embalaje y las pruebas determina la estructura de la clientela.

Los grandes fabricantes de diseño solo cooperarán con fabricantes de pruebas que tengan una cierta escala. Si la escala no aumenta, es difícil aceptar pedidos grandes y optimizar la estructura de clientes. Por lo tanto, las empresas con tecnología y escala líderes entrarán en un círculo virtuoso: tecnología líder → desarrollo de clientes → expansión de la financiación → aumento de la capacidad de producción → optimización de procesos → tecnología líder, y ampliarán gradualmente la brecha con sus competidores.

3. Competitividad básica

Las dos características anteriores del sector determinan la competitividad básica de las empresas de pruebas profesionales de circuitos integrados:

Capacidad de I+D: centrarse en el desarrollo de procedimientos y soluciones de pruebas.

Grado de comercialización: las capacidades de desarrollo de programas de pruebas y optimización de procesos provienen de la experiencia en pruebas de diferentes tipos de chips aportada por un gran número de clientes.

Proceso de prueba perfecto: a través de la estrecha integración del diseño inicial y el procesamiento de obleas, el proceso y el procedimiento de prueba se optimizan continuamente.

Capacidad de operación de capital: la etapa actual de desarrollo nacional determina que la escala es la premisa del desarrollo. Por lo tanto, la capacidad de financiación que se ajusta a la tecnología y la fortaleza del mercado es el soporte para el desarrollo y el crecimiento de la empresa.

Mercado de paquetes y pruebas de circuitos integrados

1. Escala de empaquetado y pruebas de circuitos integrados

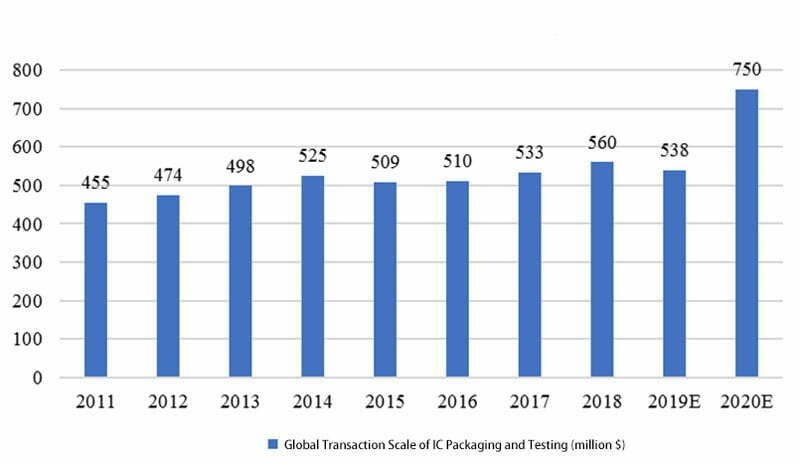

1.1 Transacciones globales de embalaje y pruebas de circuitos integrados (2011-2020)

En 2019, la industria de los semiconductores en general se ralentizó y registró un crecimiento negativo, al igual que el mercado del embalaje y las pruebas de chips. Sin embargo, este último mercado se recuperó gracias a la demanda de 5G, IA, IoT, computación en la nube y big data. Los expertos predijeron que el mercado global del embalaje y las pruebas de chips podría alcanzar los 75 000 millones de dólares en 2024.

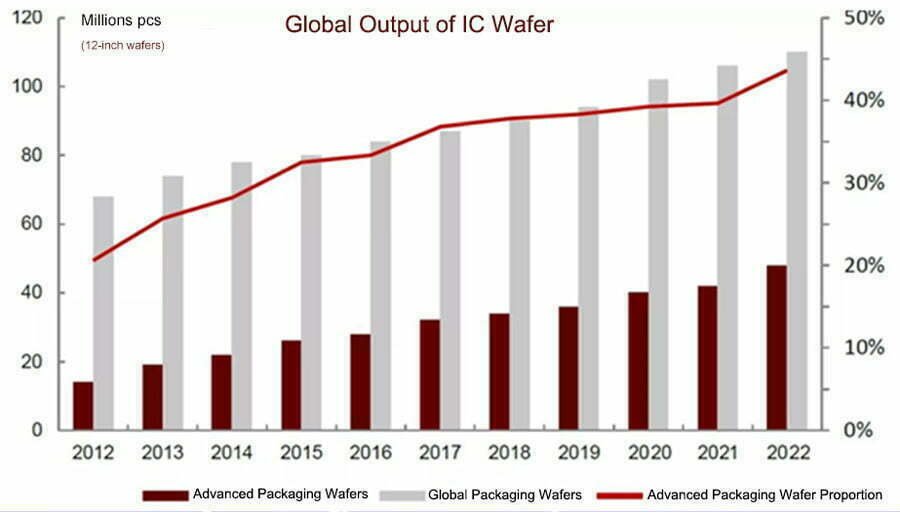

1.2 Producción mundial de obleas de circuitos integrados (2012-2022)

Con la aceleración de campos emergentes como 5G, IoT e IA, el tamaño requerido de los chips es cada vez más pequeño. Al mismo tiempo, hay cada vez más tipos de chips. El número de pines de E/S también ha aumentado significativamente y la demanda de embalajes avanzados ha aumentado gradualmente.

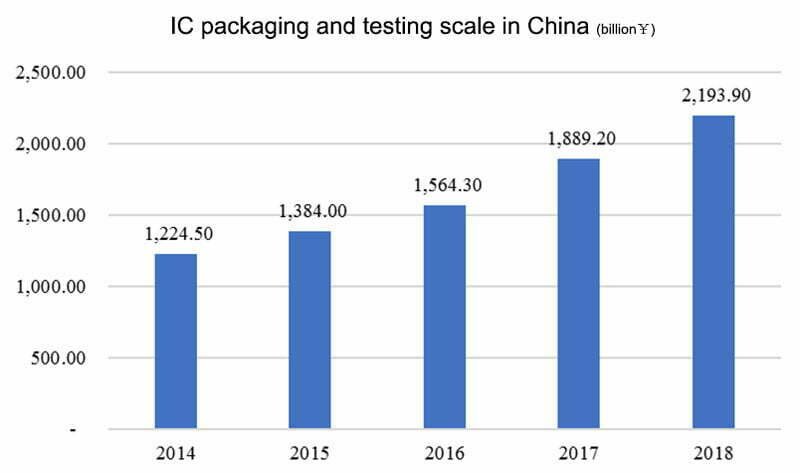

1.3 Escala de embalaje y pruebas de iC en China (2014-2018)

En 2018, la capacidad de empaquetado y prueba de circuitos integrados en China continental alcanzó los 217 440 millones de unidades, y el tamaño del mercado de la industria de empaquetado y prueba de circuitos integrados alcanzó los 219 390 millones de yuanes, lo que supone un aumento interanual del 16,1 %.

2. El crecimiento de la escala de embalaje avanzado

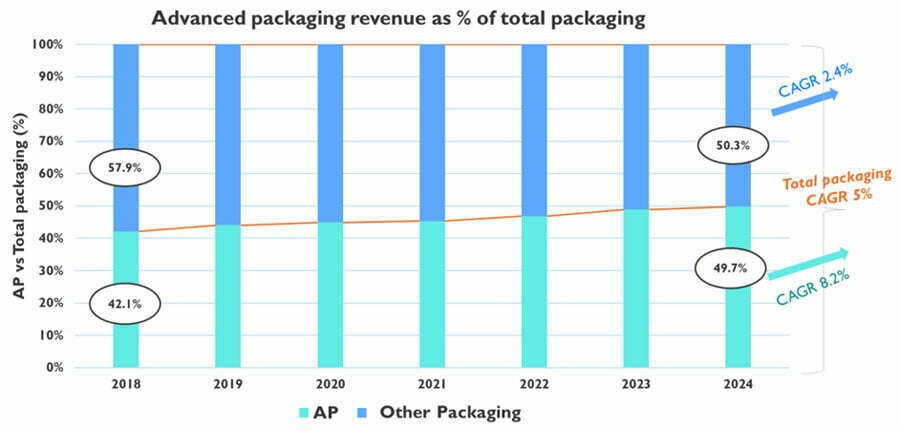

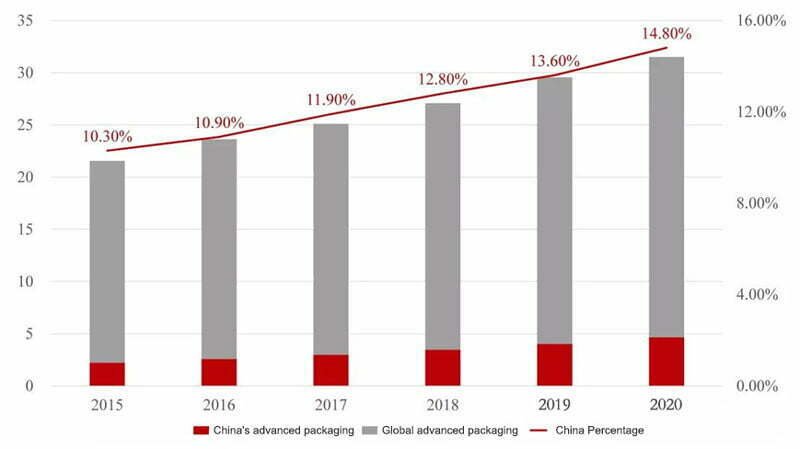

2.1 Proporción de encapsulados IC avanzados en el total

Según las estadísticas de Yole, aunque la industria de los semiconductores en general se ralentizó y experimentó un crecimiento negativo en 2019, el tamaño del mercado de los envases avanzados mantendrá una tendencia de crecimiento. En 2018, el tamaño del mercado de los envases avanzados era de 27 600 millones de dólares estadounidenses.

Con una tasa de crecimiento anual compuesta del 8 %, alcanzará aproximadamente los 44 000 millones de dólares en 2024. El mercado del embalaje tradicional crecerá a una tasa de crecimiento anual compuesta del 2,4 %, mientras que la tasa de crecimiento anual compuesta de toda la industria del embalaje de circuitos integrados alcanzará el 5 %.

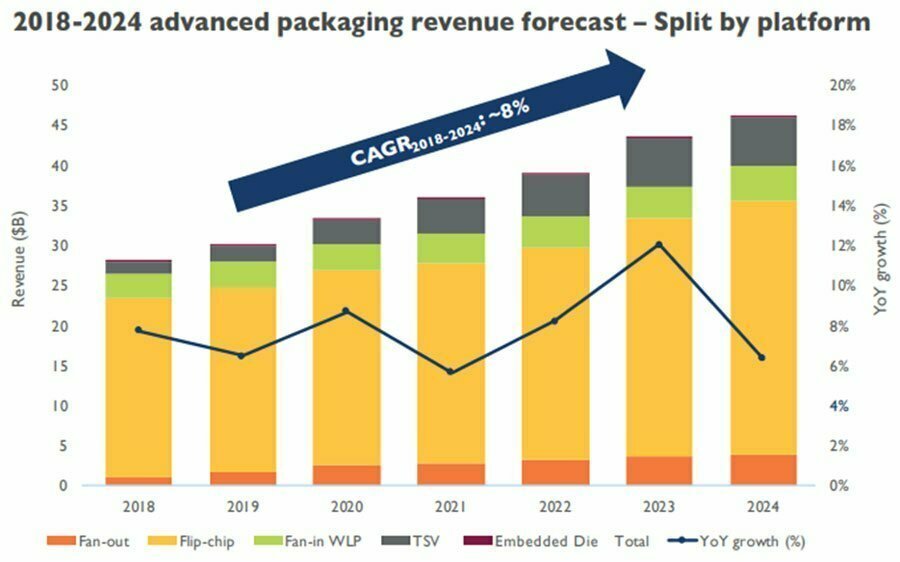

2.2 Tendencias previstas en los ingresos del sector del embalaje avanzado (2018-2024)

En el negocio del embalaje avanzado, la tecnología flip-chip representa la mayor proporción. En 2018, los ingresos por embalaje y pruebas flip-chip representaron alrededor del 81 % del mercado del embalaje avanzado. Para 2024, debido al rápido desarrollo de otras tecnologías, descenderá al 72 %.

De 2018 a 2024, TVS, ED y fan-out son las tecnologías de más rápido crecimiento. Se prevé que la tasa de crecimiento de los ingresos del embalaje 2.5D/3D (TSV), ED y fan-out (Fan-out) sea del 26 %, 49 % y 26 %, respectivamente.

La tasa compuesta de crecimiento anual (CAGR) de Fan-in WLP 2018-2024 es relativamente baja, solo del 6,5 %, y el tamaño del mercado de los chips integrados en 2018 es inferior a 25 millones de dólares estadounidenses.

Sin embargo, la tasa compuesta de crecimiento anual (CAGR) alcanzará el 49 % en los próximos cinco años, y los principales factores impulsores provendrán de la demanda de instalaciones de comunicaciones, electrónica automotriz y mercados móviles.

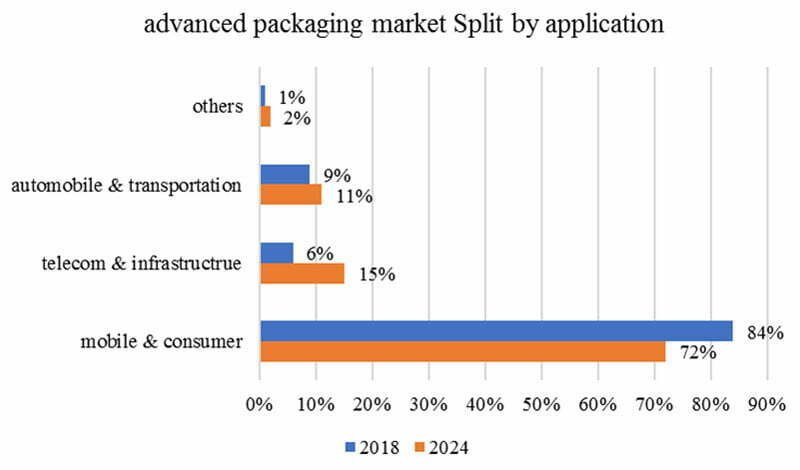

2.3 Aplicaciones avanzadas de embalaje

Por campo de aplicación, en 2018, las aplicaciones móviles y de consumo representaron el 84 % del mercado total de embalajes avanzados. Entre 2019 y 2024, la tasa compuesta de crecimiento anual (CAGR) de este segmento del mercado de aplicaciones fue del 5 %, y en 2024 representó el 72 % del mercado total de embalajes avanzados.

El segmento de las telecomunicaciones y las infraestructuras es el de más rápido crecimiento del mercado de los envases avanzados (alrededor del 28 %), y su cuota de mercado pasará del 6 % en 2018 al 15 % en 2024.

Al mismo tiempo, la cuota de mercado del segmento de la automoción y el transporte creció del 9 % en 2018 al 11 % en 2024.

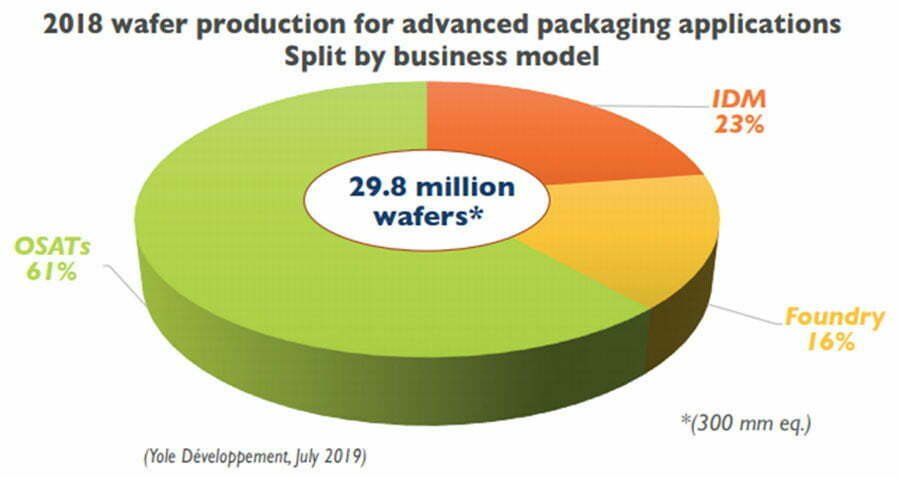

En 2018, las fundiciones profesionales de encapsulado y pruebas de chips representaron el 61 % del mercado de encapsulado y pruebas avanzadas, mientras que las empresas de tipo IDM representaron el 23 % y los fabricantes de tipo fundición representaron el 16 %.

Panorama competitivo

1. Las 10 principales empresas mundiales (2018-2019)

El mercado del embalaje y las pruebas de chips está relativamente concentrado. Los diez principales fabricantes controlan alrededor del 80 % del mercado. Los fabricantes de China continental y Taiwán dominan el mercado. Durante muchos años, la industria taiwanesa de embalaje y pruebas ha capturado casi la mitad de los ingresos operativos mundiales, consolidándose firmemente entre los diez primeros.

Independientemente de los ingresos por encapsulado y pruebas de chips de los IDM (como Intel y Samsung), ASE y Amkor se mantienen firmemente en los dos primeros puestos en el ámbito del encapsulado y las pruebas de chips profesionales.

2. Oportunidades y retos

Los cambios en la cadena de suministro de semiconductores, los cambios en los modelos de negocio y la incertidumbre en las relaciones comerciales entre Estados Unidos y China han creado oportunidades para algunos fabricantes y amenazas para otros.

2.1 Ampliación de la cadena industrial

En este entorno empresarial en constante cambio, la cadena de suministro de semiconductores está cambiando a todos los niveles. Algunos proveedores han logrado ampliar con éxito nuevos modelos de negocio.

Esto ha afectado significativamente a la cadena de fabricación de circuitos integrados, mientras que otros fabricantes no han sabido aprovechar el impulso. Los diferentes proveedores tienen diferentes motivos que les impulsan a expandirse a nuevos negocios.

Por ejemplo, empresas de software como Google, Microsoft, Facebook y Alibaba están diseñando sus propios procesadores para lograr la integración/personalización a nivel de sistema y el control de la cadena de suministro a nivel de montaje.

El mayor cambio se encuentra en las fundiciones, que están empezando a expandirse al negocio del embalaje avanzado. Aunque son relativamente «recién llegadas», su impacto es enorme.

2.2 Innovación en tecnología de envasado

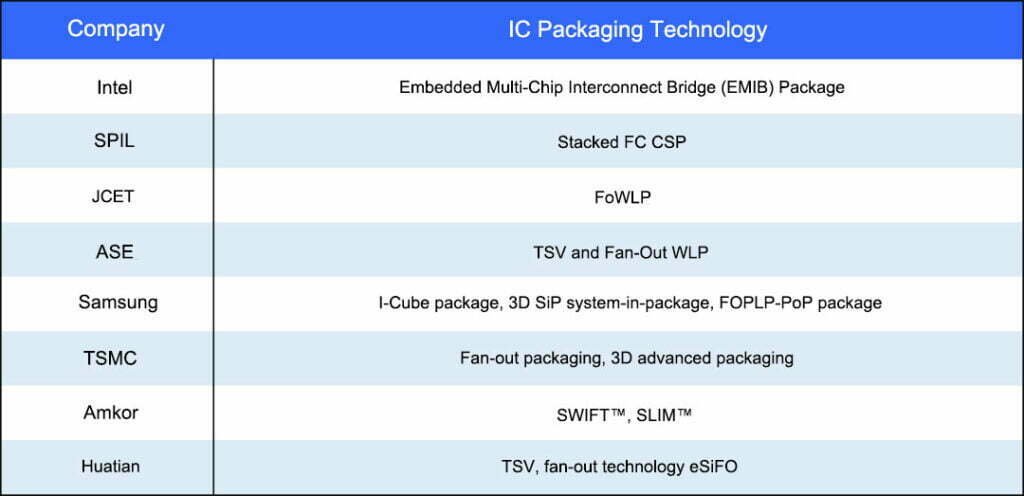

TSMC lidera la innovación en plataformas de encapsulado fan-out y encapsulado 3D avanzado. Ofrece una amplia variedad de productos, como InFO (y sus variantes), CoWoS, WoW, 3D SoIC y muchos más.

El encapsulado avanzado se ha convertido en un negocio maduro para TSMC. Se espera que genere unos ingresos de 3000 millones de dólares en 2019, lo que lo situaría en cuarto lugar en la clasificación OSAT.

UMC es un importante proveedor de interpositores de silicio para encapsulados 2.5D. Recientemente se ha asociado con Xperi para optimizar y comercializar las tecnologías ZiBond y DBI para diversos dispositivos semiconductores.

Por su parte, Wuhan Xinxin (XMC) proporciona paquetes TSV de circuitos integrados 3D para sensores de imagen y aplicaciones de alto rendimiento. En conjunto, estos actores han desempeñado un papel importante en el paso del encapsulado de sustratos a plataformas de silicio.

2.3 El empaquetado a nivel de sistema tiende a ser popular.

Es una tendencia que los participantes en la cadena industrial del embalaje SiP se expandan hacia arriba y hacia abajo. En la cadena industrial tradicional del embalaje SiP, las empresas representativas del embalaje y las pruebas de circuitos integrados incluyen Changdian Technology y ASE, que proporcionan principalmente productos de embalaje y pruebas estándar a nivel funcional. La empresa representativa del embalaje a nivel de sistema es USI, que se dedica principalmente al embalaje de sistemas a nivel de módulo. Estas dos empresas pertenecen a la relación ascendente y descendente, y sus procesos y equipos involucrados son diferentes.

2.4 Chips integrados

Por otro lado, los fabricantes de sustratos IC y PCB, como Samsung Electro-Mechanics (SEMCO), Unimicron, AT&S y Shinko Electric (Shinko), están aprovechando los chips integrados (y pasivos) en paquetes fan-out a nivel de panel y sustratos orgánicos. componentes) en el espacio de embalaje avanzado y están ganando cuota de mercado a OSAT (especialmente en el negocio relacionado con el embalaje avanzado).

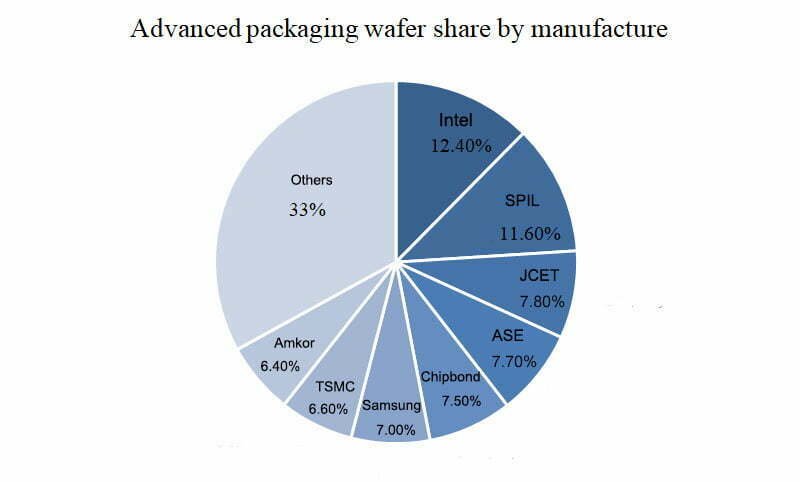

3. Cuota de mercado de los encapsulados avanzados para obleas

En comparación con la concentración general del mercado de embalaje y pruebas, la concentración del mercado de embalaje y pruebas avanzados es relativamente baja. En 2017, los ocho principales fabricantes representaban el 67 % de la cuota de mercado del embalaje avanzado.

Los proveedores del mercado del embalaje avanzado tienen diferentes áreas de especialización:

Situación de la industria china de encapsulado de circuitos integrados

La industria china de encapsulado de circuitos integrados comenzó muy temprano y se desarrolló rápidamente, basándose principalmente en productos de encapsulado tradicionales. En los últimos años, los fabricantes nacionales han pasado por fusiones y adquisiciones. En la actualidad, la plataforma tecnológica china se ha sincronizado básicamente con los fabricantes extranjeros. Además, se han producido en masa tecnologías de encapsulado avanzadas como BGA, TVS, WLCSP y SiP.

Sin embargo, todavía existe una cierta diferencia entre los ingresos totales del embalaje avanzado en Taiwán y Estados Unidos. Según las estadísticas de TrendForce, los ingresos por embalaje avanzado de China en 2018 fueron de unos 52 600 millones de yuanes. Esto supuso el 25 % de los ingresos totales por embalaje y pruebas a nivel nacional, por debajo de la proporción global del 41 %. Por lo tanto, todavía hay mucho margen de crecimiento en el futuro.

Mercado avanzado de encapsulado de circuitos integrados en China

Además, también existe una gran brecha entre las empresas de embalaje del continente y los principales fabricantes internacionales. En particular, la brecha es evidente en la tecnología de embalaje de circuitos integrados de alta densidad, como la tecnología de embalaje de chips HPC. La tecnología de apilamiento 3D multichip SoC propuesta por TSMC. Adopta una estructura de unión sin protuberancias, lo que puede mejorar en gran medida la velocidad de cálculo general de la CPU/GPU y la memoria. Intel también propuso un concepto de embalaje 3D similar, apilando memoria en chips de CPU y GPU.

El valor global de la producción del mercado chino de envases avanzados es relativamente bajo, pero está creciendo rápidamente y su proporción se está ampliando. Datos de Yole. En 2017, el valor de la producción de envases avanzados de China fue de 2900 millones de dólares, lo que representa el 11,9 % del total mundial, y alcanzará los 4600 millones de dólares en 2020, lo que representa el 14,8 % del total mundial. Según los datos, las empresas chinas de embalaje y pruebas aceleraron el aumento de la capacidad de producción en el campo del embalaje avanzado en 2018, con una tasa de crecimiento del 16 %, el doble de la tasa mundial.

fuerza impulsora del mercado

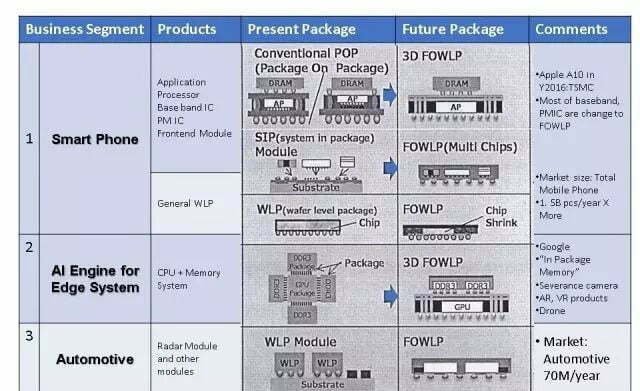

Hay dos vías de desarrollo para los encapsulados avanzados:

una consiste en reducir el tamaño para acercarlo al del chip. Un indicador importante es la relación entre el área del chip y el área del encapsulado. Cuanto más se acerque esta relación a 1, mejor, incluyendo WLCSP, FC, Bumping, Fanout, etc.

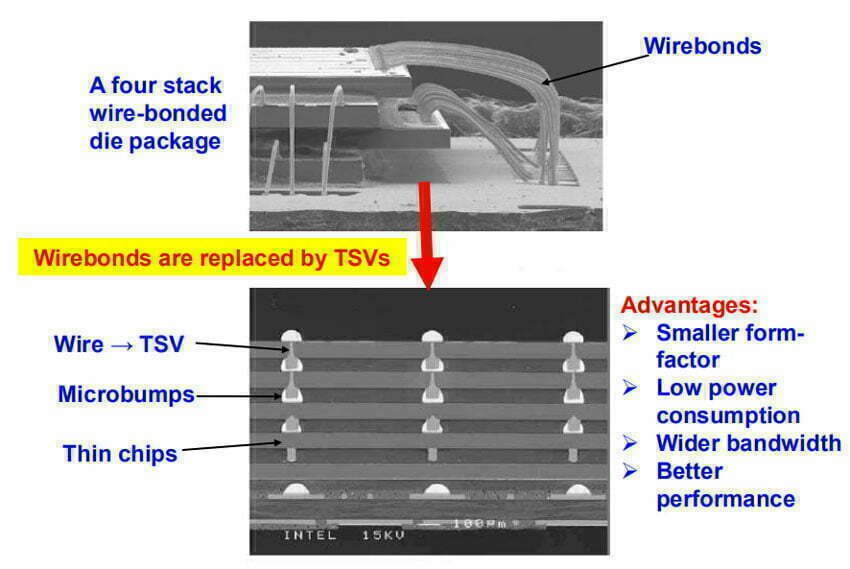

La segunda es el desarrollo funcional, que hace hincapié en la integración heterogénea y proporciona multifuncionalidad en la miniaturización de sistemas, incluyendo TSV, SIP, etc.

1. Tecnología SIP

El proceso global de fabricación de semiconductores se está acercando al límite físico de los diodos. El proceso más avanzado es el de 7 nm. Debido a la enorme inversión que requiere, cada vez resulta más caro mejorar el rendimiento de los chips desde el punto de vista de la fabricación. Partiendo del encapsulado de los chips, la tecnología SIP (sistema en paquete) combina chips con diferentes funciones, como chips lógicos y memoria.

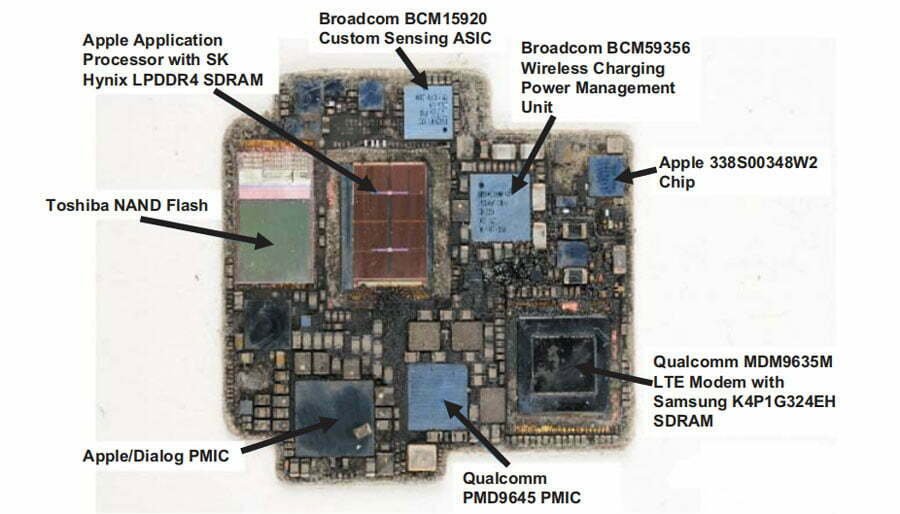

Los componentes pasivos IPD, RF RF y sensores y otros chips se empaquetan en un solo módulo, lo que puede reducir el tamaño del chip, mejorar su rendimiento y reducir el consumo de energía. El Internet de las cosas (IoT) es un importante escenario de aplicación que promueve el desarrollo de la tecnología de empaquetado SIP, y los dispositivos portátiles son un campo con un gran potencial de aplicación para la tecnología de sistema en paquete en el futuro. El sensor de reconocimiento de huellas dactilares, el sensor de reconocimiento facial 3D, la red inalámbrica WiFi y otros módulos funcionales del Apple Watch están empaquetados juntos, lo que supone el uso de la tecnología de módulos de sistema en paquete (SiP) de ASE.

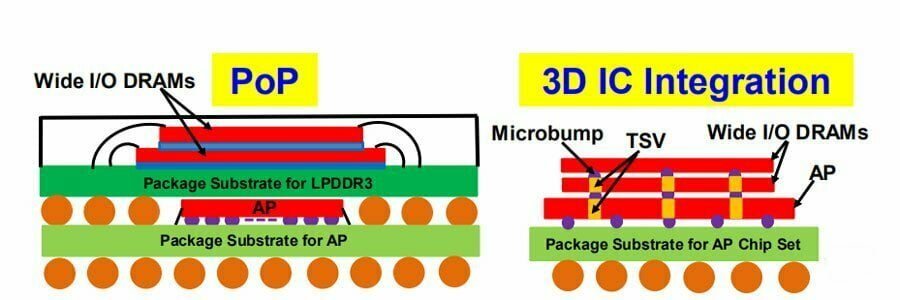

La tecnología SIP integra con éxito circuitos integrados, dispositivos discretos, dispositivos ópticos, memorias, condensadores cerámicos multicapa y resistencias de chip en sustratos delgados, finos y cortos sin que su información interfiera entre sí. Creemos que Apple lleva al menos uno o dos años de ventaja a sus competidores en la aplicación del empaquetado de sistemas. Según los diferentes requisitos de aplicación y la complejidad del producto, los tipos de SiP (sistema en paquete) se pueden dividir en módulos 2D que contienen múltiples componentes activos y pasivos y módulos 3D más complejos. Por ejemplo, PiP (paquete en paquete) en el sistema, PoP (paquete sobre paquete) y tecnología de encapsulado 2.5D/3D en el sistema.

2. Tecnología TSV

Como representante de la tecnología de encapsulado 3D, la tecnología TSV tendrá mayores aplicaciones en el campo del encapsulado de memorias flash 3DNANDFLASH y del encapsulado de memorias DRAM en el futuro. La memoria se ha convertido en la subsección con mayor potencial de crecimiento en el campo de los semiconductores nacionales. Los dos principales proyectos de memoria, Yangtze Memory (NAND FLASH) y Hefei Changxin (DRAM), se producirán en masa en 2020, lo que sin duda supondrá enormes oportunidades de crecimiento para los fabricantes nacionales con tecnología de encapsulado avanzada.

3. Fan-out

Al entrar en la era 5G, para obtener una mayor velocidad de transmisión de datos y capacidad de ancho de banda, es necesario utilizar ondas electromagnéticas de mayor frecuencia como medio de transmisión, y las longitudes de onda son más cortas y entran en el nivel de ondas milimétricas. Las dos frecuencias principales en la era 5G, la banda de frecuencia Sub-6GHz y la banda de frecuencia de ondas milimétricas de 28GHz, debido al aumento de la frecuencia, el resultado de la caída de la longitud de onda es que la antena es más corta, por lo que se espera que la antena se integre en el chip en la era de los chips 5G para simplificar el diseño y reducir los costes.

Hay dos tecnologías de encapsulado posibles para los chips 5G de próxima generación: AiP (Antenna in Package) con un sustrato y un encapsulado fan-out sin placa portadora. Dado que el segundo esquema de encapsulado fan-out no requiere un sustrato, puede reducir aún más los costes y reducir el tamaño del chip sobre la base de la integración de múltiples chips, por lo que la tecnología de encapsulado fan-out puede convertirse en la tecnología principal del encapsulado de chips 5G.

Cada módulo electrónico del automóvil adopta diferentes tecnologías de encapsulado, y el encapsulado del chip de radar de ondas milimétricas en la electrónica automotriz también utilizará una gran cantidad de tecnología de encapsulado Fan-out.

La fábrica nacional de encapsulado y pruebas Changdian Technology adquirió la tecnología de encapsulado eWLB tras adquirir Xingke Jinpeng, convirtiéndose en uno de los primeros fabricantes de encapsulado y pruebas en el campo de los radares de ondas milimétricas. Se espera que Huatian Technology realice esfuerzos en este campo tras los recientes avances tecnológicos.

Dirección del desarrollo tecnológico

Existen dos tipos de encapsulado de semiconductores: el encapsulado tradicional y el encapsulado avanzado. Con la continua expansión de la escala del encapsulado avanzado, su proporción se ha ido acercando y superando gradualmente a la tendencia del encapsulado tradicional. Para la industria de los semiconductores, el encapsulado y las pruebas ya no son solo un eslabón independiente de la fundición como en el pasado, sino una solución integrada que combina diseño, materiales y equipos.

Por lo tanto, el empaquetado avanzado es cada vez más importante en el campo del empaquetado y las pruebas de semiconductores. Según las previsiones de Yole, el mercado mundial del empaquetado avanzado alcanzará el 44 % del total de los servicios de empaquetado de circuitos integrados en 2020, con unos ingresos operativos anuales de aproximadamente 31 500 millones de dólares estadounidenses; el mercado chino del empaquetado avanzado alcanzará los 4600 millones de dólares estadounidenses en 2020, con una tasa de crecimiento anual compuesta del 16 %. Desde un punto de vista técnico, FOWLP, SiP y 3DTSV son las tres tecnologías de encapsulado y pruebas avanzadas que más interés suscitan.

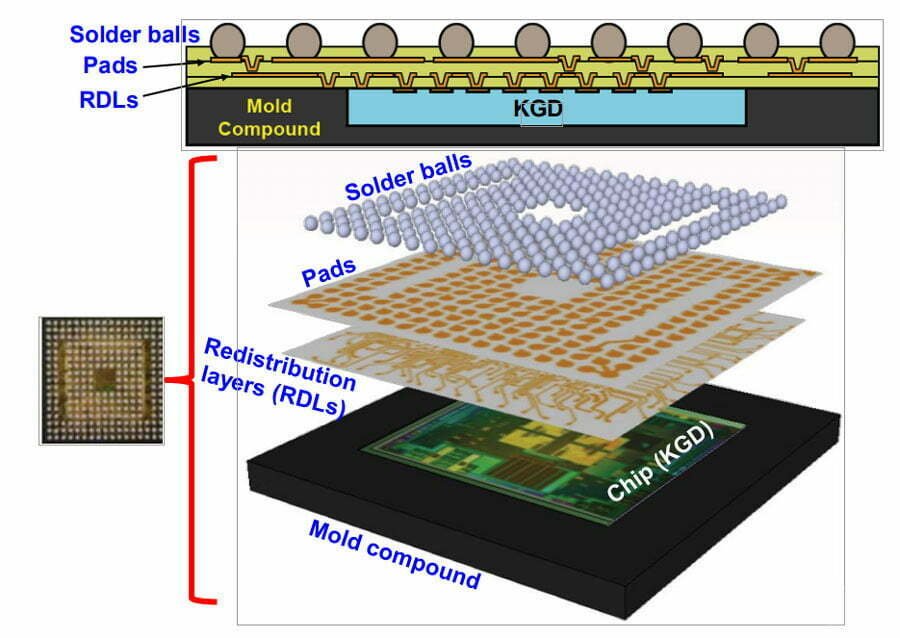

1. Embalaje FOWLP

El paquete FOWLP hace referencia a un nuevo método para combinar múltiples matrices de procesos heterogéneos en un paquete compacto. Fue propuesto por primera vez por Intel. Las ventajas del FOWLP con respecto a la tecnología de encapsulado fan-in son: menor grosor del paquete, escalabilidad (para aumentar el número de E/S), mejor rendimiento eléctrico, buen rendimiento térmico y un proceso sin sustrato.

2. Empaquetado SiP

El sistema en paquete (SiP) es un nuevo tipo de tecnología de encapsulado de gama alta en el campo del encapsulado de circuitos integrados, que integra uno o más chips de circuitos integrados y componentes pasivos en un solo paquete. El SiP es una solución ideal que combina las ventajas de los recursos básicos existentes y los procesos de producción de semiconductores para reducir los costes y acortar el tiempo de comercialización. Al mismo tiempo, supera dificultades como la compatibilidad de procesos, la mezcla de señales, la interferencia de ruido y la interferencia electromagnética en SOC. Además, la aplicación del SiP es muy amplia. En la actualidad, el valor de producción de los teléfonos inteligentes representa la proporción más alta, alrededor del 70 %.

La creciente demanda de encapsulados SiP provocada por el uso comercial de la tecnología 5G. En primer lugar, debido al aumento del valor de la RF autónoma, el tamaño total del mercado de los frontales de RF ha crecido rápidamente. Existe una tendencia general hacia la modularización de los componentes de integración de RF, las antenas de ondas milimétricas 5G y los componentes de integración de RF, que suelen basarse en GaAs. La antena 5G se compone principalmente de LCP (polímero de cristal líquido), y el encapsulado SiP es muy adecuado para la integración heterogénea. Se espera que el encapsulado SiP se popularice en el sector de la RF.

3. Empaquetado 3D - TSV

El embalaje 3D mejora el rendimiento básico, como el tamaño, el peso, la velocidad, el rendimiento y el consumo de energía, y la mayoría de los fabricantes de semiconductores lo consideran el método de embalaje más prometedor. A medida que los tentáculos del embalaje avanzado continúan extendiéndose a tecnologías avanzadas con alto rendimiento e integración de alta densidad, se espera que TSV, conocida como la tecnología de embalaje 3D de cuarta generación, se convierta en una fuerza impulsora sostenible para el desarrollo futuro del embalaje avanzado.