Descripción general del MSP430F169

El microcontrolador MSP430F169 pertenece a la familia MSP430 de Texas Instruments. Comprende múltiples dispositivos que cuentan con distintos conjuntos de periféricos diseñados para diversas aplicaciones. La arquitectura de estos microcontroladores, junto con cinco modos de bajo consumo, se ha ajustado para optimizar la duración de la batería en aplicaciones de medición portátiles. Además, el oscilador controlado digitalmente (DCO) permite tiempos de activación rápidos, de menos de 6 µs, desde los modos de bajo consumo al modo activo.

Estos microcontroladores encuentran aplicaciones típicas en sistemas de sensores, aplicaciones de control industrial, medidores portátiles y otros ámbitos similares.

Características

- Bajo consumo de energía;

- Cinco modos de ahorro de energía;

- DMA interno de tres canales;

- Programación en serie integrada;

- Protección de código programable mediante fusible de seguridad;

- Con detector de caídas de tensión y cargador de arranque;

- Monitor de tensión de alimentación con detección de nivel programable.

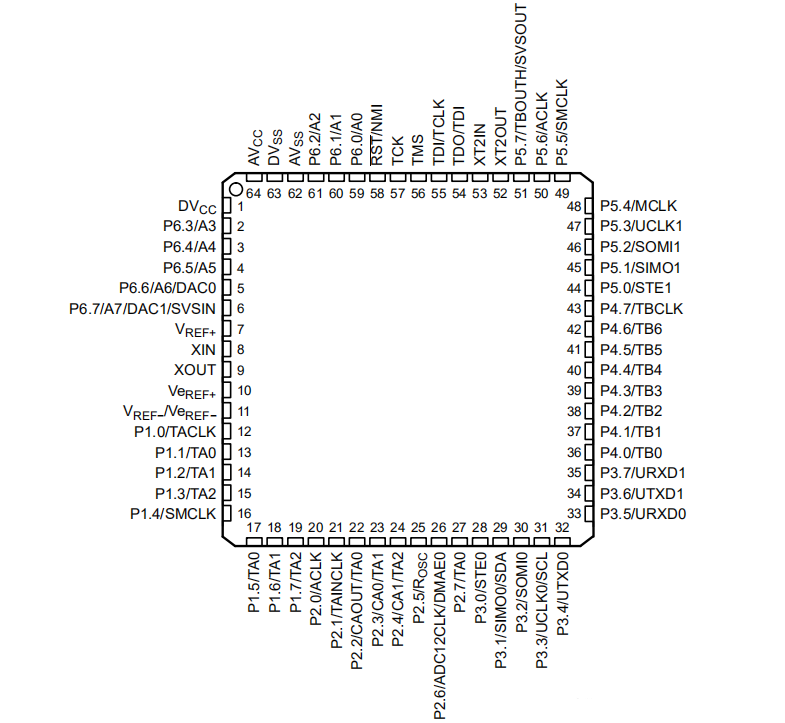

Configuración de pines

El MSP430F169 está disponible en versiones de 64 y 100 pines, con diferentes configuraciones de pines para cada una.

En la versión de 64 pines, algunos pines clave son:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Especificación

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

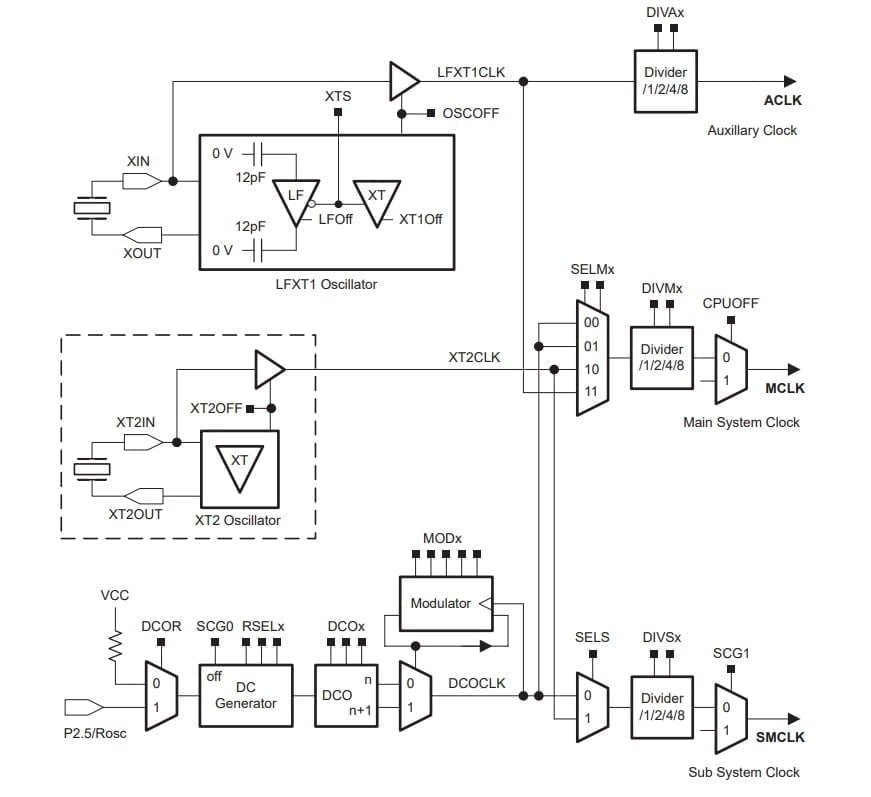

Sistema de reloj del MSP430F169

El sistema de reloj es muy importante para los microordenadores de un solo chip. La razón por la que el microordenador de un solo chip MSP430F169 tiene un consumo energético tan bajo es porque cuenta con un potente sistema de reloj.

Tres fuentes de señal de reloj

1. Baja frecuencia LFXT1CLK (32,768 kHz)

Se puede utilizar un oscilador de cristal estándar, un oscilador o una fuente de reloj externa para introducir entre 4 MHz y 32 MHz. XT1CLK se puede utilizar como reloj de referencia para el módulo FLL interno.

El oscilador de cristal de baja frecuencia (32,768 KHz) se conecta directamente al microordenador de un solo chip a través de los pines XIN y XOUT, y no se requieren otros dispositivos externos (hay una capacitancia de carga de 12 pF en el interior). En este momento, el oscilador LFXT1 funciona en modo de baja frecuencia (XTS=0).

Si la MCU está conectada a un oscilador o resonador de alta velocidad, 0SCOFF=0 puede hacer que el oscilador LFXT1 funcione en modo de alta frecuencia (XTS=1). En ese momento, el oscilador de cristal o resonador de alta velocidad se conecta a través de los pines XIN y XOUT, y se requiere un condensador externo. El tamaño del condensador se selecciona de acuerdo con las características del oscilador de cristal o resonador.

Si la señal LFXT1CLK no se utiliza como señal SMCLK o MCIK, el software puede establecer OSCOFF=1 para desactivar el funcionamiento del LFXT1, reduciendo así el consumo de energía del microcontrolador.

BCSCTL1:

XTS(BIT6)——Selección del modo de alta/baja velocidad LFXT1. 0: LFXT1 funciona en modo oscilador de cristal de baja velocidad (predeterminado); 1: LFXT1 funciona en modo oscilador de cristal de alta velocidad.

2. XT2CLK de alta frecuencia (8 MHz)

Se puede utilizar un oscilador de cristal estándar, un oscilador o una fuente de reloj externa para introducir entre 4 MHz y 32 MHz.

El oscilador XT2 genera la señal de reloj XT2CLK y sus características de funcionamiento son similares a las del oscilador LFXT1 cuando funciona en modo de alta frecuencia. Si XT2CLK no se utiliza como señal de reloj MCLK y SMCLK, el oscilador XT2 se puede desactivar con el bit de control XT2OFF.

BCSCTL1:

XT2OFF (BIT7): control del oscilador de cristal de alta velocidad XT2. 0: oscilador de cristal de alta velocidad XT2 activado; 1: oscilador de cristal de alta velocidad XT2 desactivado.

3. Oscilador interno DCOCLK (1 MHz)

Estabilizado por el módulo FLL.

Cuando el oscilador falla, el DCO se selecciona automáticamente como fuente de reloj para MCLK.

La frecuencia del oscilador DCO se puede ajustar mediante la configuración del software de los bits DCOx. MODx y RSEL.x. Cuando la señal DCOCLK no se utiliza como señal de reloj SMCLK y MCLK, el generador de CC se puede desactivar con el bit de control SCGO.

Después de la señal PUC, DCOCLK se selecciona automáticamente como señal de reloj MCLK, y la fuente de reloj de MCLK se puede configurar adicionalmente en LFXT1 o XT2 según sea necesario. La secuencia de configuración es la siguiente:

- Deja OSCOFF=1;

- Deja que OFIFG=0;

- Retrasa y espera al menos 50 ps;

- Comprueba OFIFG de nuevo, si OFIFG=1, repite los pasos (3) y (4) hasta que OFIFG=0.

DCOCTL:

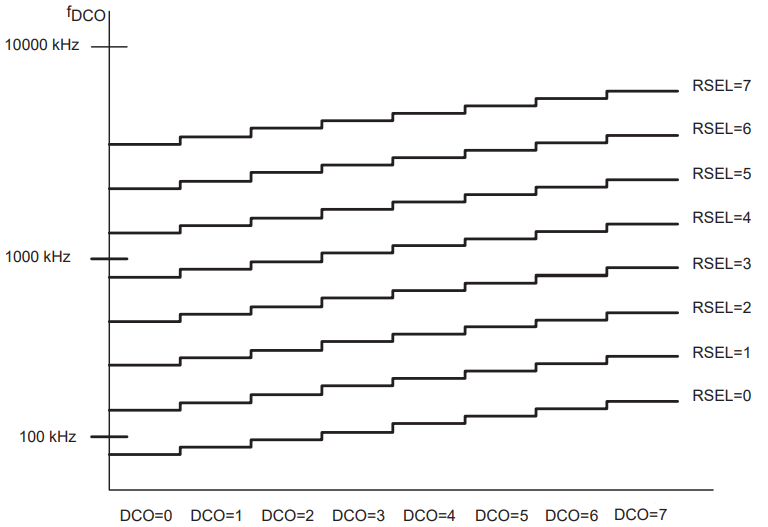

DCOx (BIT7, BIT6, BIT5): selección de frecuencia DCO, se pueden seleccionar 8 tipos de frecuencias y la frecuencia DCOCLK se puede ajustar por secciones. La selección de frecuencia se basa en la banda de frecuencia seleccionada por RSELx. La relación entre DCOx, RSELx y el reloj interno es la siguiente:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0): ajuste del modulador DAC. El control cambia las dos frecuencias seleccionadas por DCOx y DCOx+1 para ajustar con precisión la frecuencia de salida del DCO. Si la constante DCOx es 7, significa que se ha seleccionado la frecuencia más alta. En ese momento, MODx no es válido y no se puede utilizar para ajustar la frecuencia.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0): selección de la banda de frecuencia del oscilador DCO. Estos 3 bits controlan una resistencia interna para determinar la frecuencia nominal. 0: selecciona la frecuencia nominal más baja… 7: selecciona la frecuencia nominal más alta.

BCSCTL2:

DCOR(BIT0): selecciona la resistencia del oscilador DCO. 0: resistencia interna; 1: resistencia externa.

Tres fuentes de reloj

1. Reloj auxiliar ACLK

ACLK se obtiene después de dividir LFXT1CLK por 1, 2, 4 y 8. Se puede utilizar como señal de reloj de cada módulo periférico y, por lo general, se utiliza para periféricos de baja velocidad.

BCSCTL1:

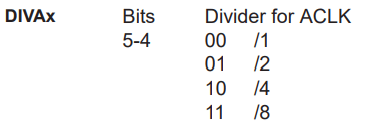

DIVAx (BIT5, BIT4): selección de división de frecuencia ACLK. La relación de selección de división de frecuencia es la siguiente:

Definición de macro: DIVA_0 (1 división de frecuencia/sin división de frecuencia), DIVA_1 (2 divisiones de frecuencia), DIVA_2 (4 divisiones de frecuencia), DIVA_3 (8 divisiones de frecuencia)

2. Reloj principal del sistema MCLK

MCLK se puede obtener a partir de LFXT1CLK, XT2CLK y DCOCLK tras una división de frecuencia por 1, 2, 4 y 8. Se utiliza a menudo para el funcionamiento de la CPU, la ejecución de programas y otros módulos que utilizan relojes de alta velocidad.

BCSCTL2:

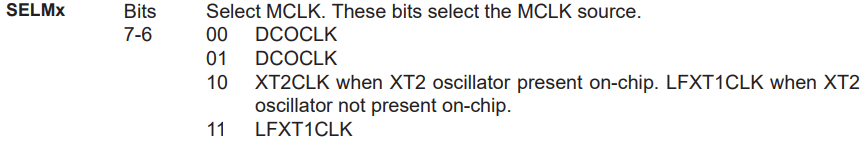

SELMx (BIT7, BIT6): selecciona la fuente de reloj MCLK. La relación de selección de reloj es la siguiente:

Definición de macro: SELM_0 (DCOCLK predeterminado), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

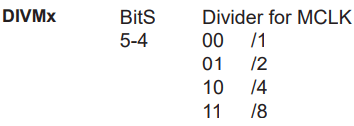

DIVMx (BIT5, BIT4): selección de división de frecuencia MCLK. La relación de selección de división de frecuencia es la siguiente:

Definición de macro: DIVM_0 (1 división de frecuencia/sin división de frecuencia), DIVM_1 (2 divisiones de frecuencia), DIVM_2 (4 divisiones de frecuencia), DIVM_3 (8 divisiones de frecuencia)

3. Reloj del subsistema SMCLK

SMCLK se puede obtener mediante la división de frecuencia de XT2CLK y DCOCLK por 1, 2, 4 y 8, y se utiliza a menudo en módulos periféricos de alta velocidad.

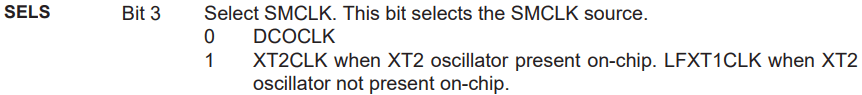

BCSCTL2:

SELSx (BIT3): selecciona la fuente de reloj MCLK. La relación de selección de reloj es la siguiente:

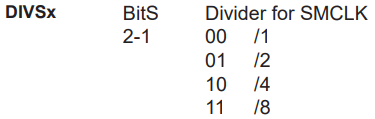

DIVSx (BIT2, BIT1): selección de división de frecuencia SMCLK. La relación de selección de división de frecuencia es la siguiente:

Definición de macro: DIVS_0 (1 división de frecuencia/sin división de frecuencia), DIVS_1 (2 divisiones de frecuencia), DIVS_2 (4 divisiones de frecuencia), DIVS_3 (8 divisiones de frecuencia)