MSP430F169 Genel Bakış

MSP430F169 Mikrodenetleyici, Texas Instruments MSP430 ailesinin bir üyesidir. Bu aile, çeşitli uygulamalar için tasarlanmış farklı çevre birimi setlerine sahip çok sayıda cihazdan oluşur. Bu mikrodenetleyicilerin mimarisi, beş düşük güç modu ile birleştirilerek, taşınabilir ölçüm uygulamaları için pil ömrünü uzatmak üzere ince ayarlanmıştır. Ayrıca, dijital kontrollü osilatör (DCO), düşük güç modlarından aktif moda 6 µs'den daha kısa sürede hızlı uyanma süreleri sağlar.

Bu mikrodenetleyiciler, sensör sistemleri, endüstriyel kontrol uygulamaları, el tipi ölçüm cihazları ve diğer benzer alanlarda yaygın olarak kullanılmaktadır.

Özellikler

- Düşük güç tüketimi;

- Beş güç tasarrufu modu;

- Üç kanallı dahili DMA;

- Seri yerleşik programlama;

- Güvenlik sigortası ile programlanabilir kod koruması;

- Gerilim düşüşü dedektörü ve önyükleyici ile;

- Programlanabilir seviye algılama özelliğine sahip besleme gerilimi monitörü.

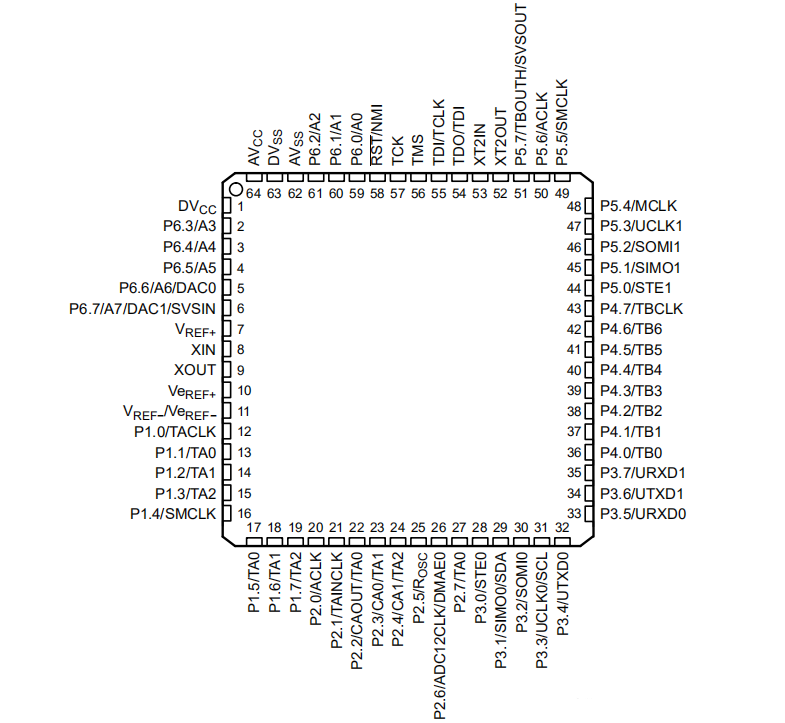

Pin Dizilişi Yapılandırması

MSP430F169, aslında hem 64 pimli hem de 100 pimli versiyonlarda mevcuttur ve her birinin farklı pin konfigürasyonları vardır.

64 pimli versiyonda bazı önemli pimler şunlardır:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Teknik Özellikler

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

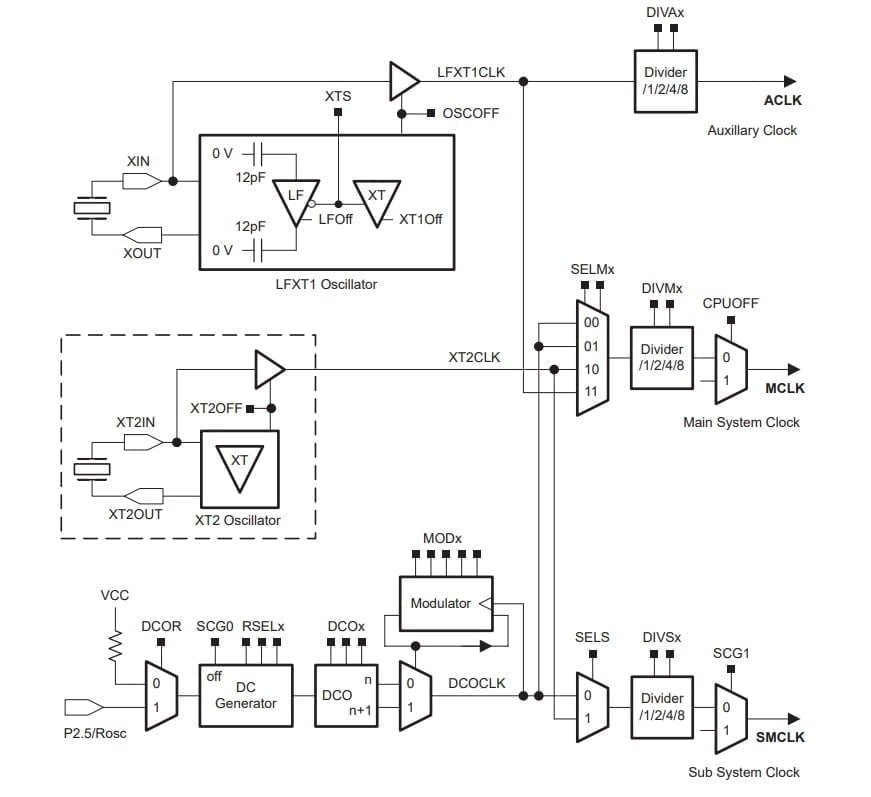

MSP430F169 Saat Sistemi

Saat sistemi, tek çipli mikrobilgisayarlar için çok önemlidir. MSP430F169 tek çipli mikrobilgisayarın güç tüketiminin bu kadar düşük olmasının nedeni, güçlü bir saat sistemine sahip olmasıdır!

Üç saat sinyali kaynağı

1. Düşük frekanslı LFXT1CLK (32,768 kHz)

4 MHz ile 32 MHz arası giriş için standart kristal osilatör, osilatör veya harici saat kaynağı kullanılabilir. XT1CLK, dahili FLL modülü için referans saat olarak kullanılabilir.

Düşük frekanslı kristal osilatör (32,768KHz), XIN ve XOUT pinleri aracılığıyla tek çipli mikrobilgisayara doğrudan bağlanır ve başka hiçbir harici cihaz gerekmez (içinde 12pF yük kapasitansı vardır). Bu durumda, LFXT1 osilatörü düşük frekans modunda çalışır (XTS=0).

MCU, yüksek hızlı bir toplu osilatör veya rezonatöre bağlıysa, 0SCOFF=0, LFXT1 osilatörünün yüksek frekans modunda (XTS=1) çalışmasını sağlayabilir. Bu durumda, yüksek hızlı kristal osilatör veya rezonatör, XIN ve XOUT pinleri aracılığıyla bağlanır ve harici bir kondansatör gereklidir. Kondansatörün boyutu, kristal osilatörün veya rezonatörün özelliklerine göre seçilir.

LFXT1CLK sinyali SMCLK veya MCIK sinyali olarak kullanılmıyorsa, yazılım OSCOFF=1 ayarını yaparak LFXT1'in çalışmasını devre dışı bırakabilir ve böylece mikrodenetleyicinin güç tüketimini azaltabilir.

BCSCTL1:

XTS(BIT6)——LFXT1 yüksek/düşük hız modu seçimi. 0: LFXT1 düşük hızlı kristal osilatör modunda çalışır (varsayılan); 1: LFXT1 yüksek hızlı kristal osilatör modunda çalışır.

2. Yüksek frekanslı XT2CLK (8 MHz)

4 MHz ile 32 MHz arası giriş için standart kristal osilatör, osilatör veya harici saat kaynağı kullanılabilir.

XT2 osilatörü, XT2CLK saat sinyalini üretir ve çalışma özellikleri, yüksek frekans modunda çalıştığında LFXT1 osilatörüninkine benzerdir. XT2CLK, MCLK ve SMCLK saat sinyali olarak kullanılmıyorsa, XT2 osilatörü XT2OFF kontrol biti ile devre dışı bırakılabilir.

BCSCTL1:

XT2OFF (BIT7) – XT2 yüksek hızlı kristal osilatör kontrolü. 0: XT2 yüksek hızlı kristal osilatör açık; 1: XT2 yüksek hızlı kristal osilatör kapalı.

3. Dahili osilatör DCOCLK (1 MHz)

FLL modülü tarafından stabilize edilir.

Osilatör arızalandığında, MCLK için saat kaynağı olarak DCO otomatik olarak seçilir.

DCO osilatörünün frekansı, DCOx. MODx ve RSEL.x bitleri yazılımla ayarlanarak değiştirilebilir. DCOCLK sinyali SMCLK ve MCLK saat sinyali olarak kullanılmadığında, DC üreteci SCGO kontrol biti ile devre dışı bırakılabilir.

PUC sinyalinden sonra, DCOCLK otomatik olarak MCLK saat sinyali olarak seçilir ve MCLK'nin saat kaynağı, gerektiğinde ek olarak LFXT1 veya XT2 olarak ayarlanabilir. Kurulum sırası aşağıdaki gibidir:

- OSCOFF=1 olsun;

- OFIFG=0 olsun;

- En az 50 ps bekleyin;

- OFIFG'yi tekrar kontrol edin, eğer OFIFG=1 ise, OFIFG=0 olana kadar (3) ve (4) numaralı adımları tekrarlayın.

DCOCTL:

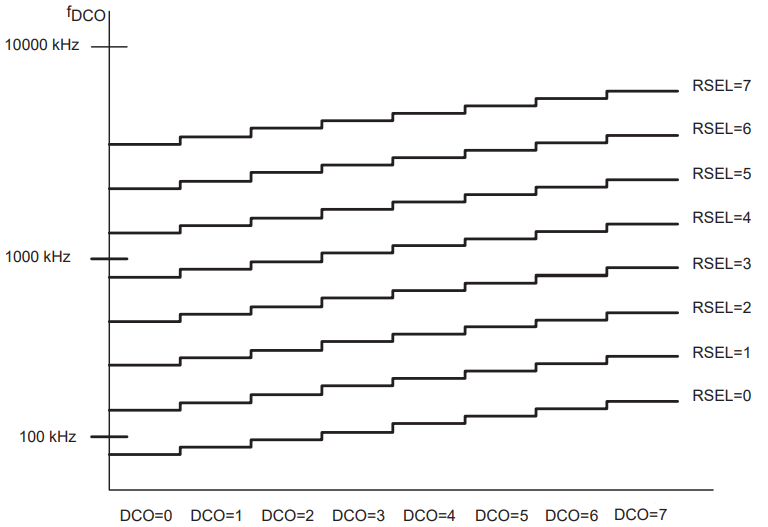

DCOx (BIT7, BIT6, BIT5)——DCO frekans seçimi, 8 çeşit frekans seçilebilir ve DCOCLK frekansı bölümler halinde ayarlanabilir. Frekans seçimi, RSELx tarafından seçilen frekans bandına dayanır. DCOx, RSELx ve dahili saat arasındaki ilişki aşağıdaki gibidir:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) – DAC modülatör ayarı. Bu kontrol, DCOx ve DCOx+1 tarafından seçilen iki frekansı değiştirerek DCO'nun çıkış frekansını hassas bir şekilde ayarlar. DCOx sabiti 7 ise, bu en yüksek frekansın seçildiğini gösterir. Bu durumda MODx geçersizdir ve frekans ayarı için kullanılamaz.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0) – DCO osilatörünün frekans bandı seçimi; bu 3 bit, nominal frekansı belirlemek için bir iç direnci kontrol eder. 0: En düşük nominal frekansı seçin… 7: En yüksek nominal frekansı seçin.

BCSCTL2:

DCOR(BIT0)——DCO osilatör direncini seçin. 0: dahili direnç; 1: harici direnç.

Üç saat kaynağı

1. ACLK yardımcı saat

ACLK, LFXT1CLK'nin 1, 2, 4 ve 8'e bölünmesiyle elde edilir. Her bir çevre birimi modülünün saat sinyali olarak kullanılabilir ve genellikle düşük hızlı çevre birimleri için kullanılır.

BCSCTL1:

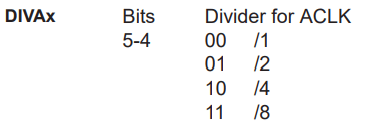

DIVAx (BIT5, BIT4)——ACLK frekans bölme seçimi, frekans bölme seçimi ilişkisi aşağıdaki gibidir:

Makro tanımı: DIVA_0 (1 frekans bölümü/frekans bölümü yok), DIVA_1 (2 frekans bölümü), DIVA_2 (4 frekans bölümü), DIVA_3 (8 frekans bölümü)

2. MCLK sistemi ana saati

MCLK, LFXT1CLK, XT2CLK ve DCOCLK sinyallerinden sırasıyla 1, 2, 4 ve 8 ile frekans bölünmesi yoluyla elde edilebilir. Genellikle CPU çalışması, program yürütme ve yüksek hızlı saat sinyalleri kullanan diğer modüller için kullanılır.

BCSCTL2:

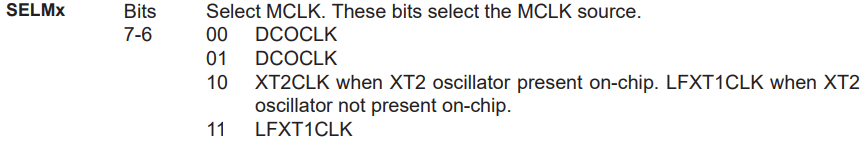

SELMx (BIT7, BIT6) – MCLK saat kaynağını seçer; saat seçimi ilişkisi aşağıdaki gibidir:

Makro tanımı: SELM_0 (DCOCLK varsayılan), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

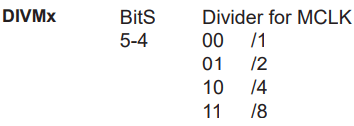

DIVMx (BIT5, BIT4) – MCLK frekans bölme seçimi, frekans bölme seçimi ilişkisi aşağıdaki gibidir:

Makro tanımı: DIVM_0 (1 frekans bölünmesi/frekans bölünmesi yok), DIVM_1 (2 frekans bölünmesi), DIVM_2 (4 frekans bölünmesi), DIVM_3 (8 frekans bölünmesi)

3. SMCLK alt sistemi saati

SMCLK, XT2CLK ve DCOCLK sinyallerinin 1, 2, 4 ve 8'e bölünmesiyle elde edilebilir ve genellikle yüksek hızlı çevre birimi modüllerinde kullanılır.

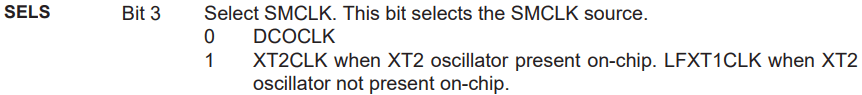

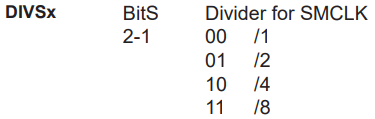

BCSCTL2:

SELSx (BIT3) – MCLK saat kaynağını seçin; saat seçimi ilişkisi aşağıdaki gibidir:

DIVSx (BIT2, BIT1) – SMCLK frekans bölme seçimi; frekans bölme seçimi ilişkisi şu şekildedir:

Makro tanımı: DIVS_0 (1 frekans bölümü/frekans bölümü yok), DIVS_1 (2 frekans bölümü), DIVS_2 (4 frekans bölümü), DIVS_3 (8 frekans bölümü)