Visão geral do MSP430F169

O microcontrolador MSP430F169 faz parte da família MSP430 da Texas Instruments. Ele compreende vários dispositivos que apresentam conjuntos distintos de periféricos projetados para diversas aplicações. A arquitetura desses microcontroladores, combinada com cinco modos de baixo consumo de energia, foi ajustada para otimizar a vida útil da bateria para aplicações de medição portáteis. Além disso, o oscilador controlado digitalmente (DCO) permite tempos de ativação rápidos, inferiores a 6 µs, dos modos de baixo consumo de energia para o modo ativo.

Esses microcontroladores encontram aplicações típicas em sistemas de sensores, aplicações de controle industrial, medidores portáteis e outros domínios semelhantes.

Características

- Baixo consumo de energia;

- Cinco modos de economia de energia;

- DMA interno de três canais;

- Programação serial integrada;

- Proteção de código programável por fusível de segurança;

- Com detector de queda de tensão e carregador bootstrap;

- Monitor de tensão de alimentação com detecção de nível programável.

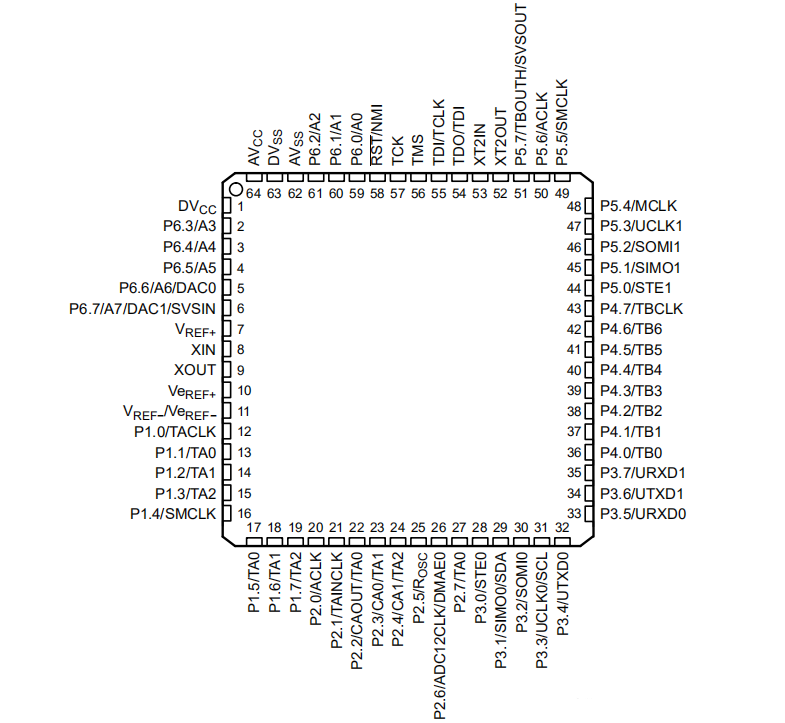

Configuração da pinagem

O MSP430F169 está disponível nas versões de 64 pinos e 100 pinos, com diferentes configurações de pinos para cada uma.

Para a versão de 64 pinos, alguns pinos importantes incluem:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Especificação

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

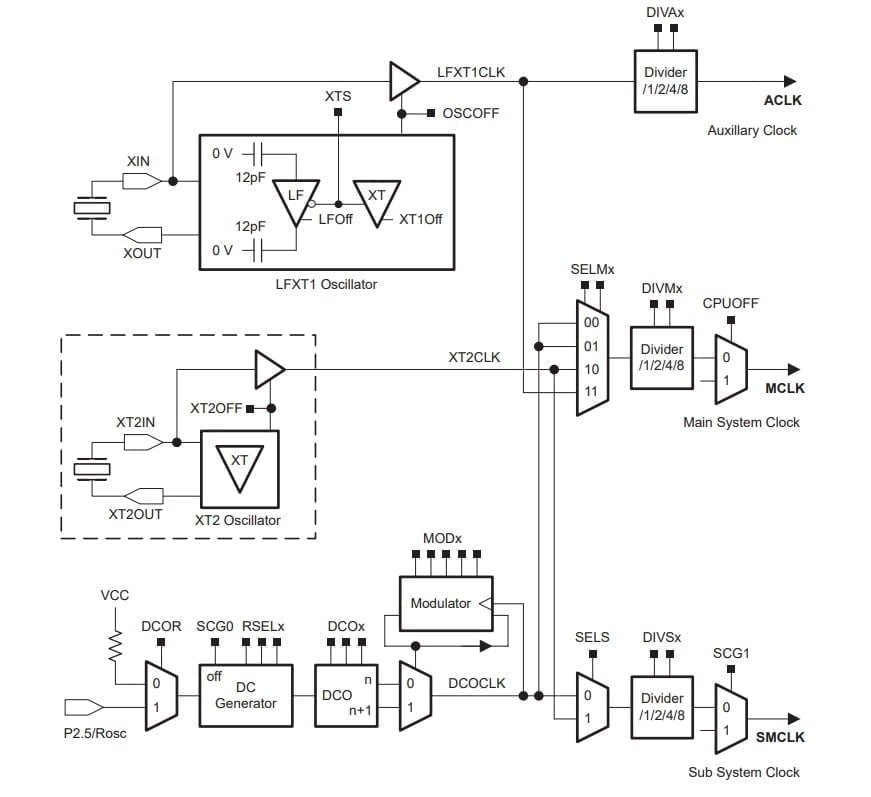

Sistema de relógio do MSP430F169

O sistema de relógio é muito importante para o microcomputador de chip único. A razão pela qual o microcomputador de chip único MSP430F169 tem um consumo de energia tão baixo é porque possui um sistema de relógio poderoso!

Três fontes de sinal de relógio

1. Baixa frequência LFXT1CLK (32,768 KHz)

O oscilador de cristal padrão, o oscilador ou a fonte de clock externa podem ser usados para inserir 4 MHz a 32 MHz. O XT1CLK pode ser usado como clock de referência para o módulo FLL interno.

O oscilador de cristal de baixa frequência (32,768 KHz) é conectado diretamente ao microcomputador de chip único através dos pinos XIN e XOUT, e nenhum outro dispositivo externo é necessário (há uma capacitância de carga de 12 pF interna). Nesse momento, o oscilador LFXT1 funciona no modo de baixa frequência (XTS=0).

Se o MCU estiver conectado a um oscilador ou ressonador de alta velocidade, 0SCOFF=0 pode fazer com que o oscilador LFXT1 funcione no modo de alta frequência (XTS=1). Nesse momento, o oscilador de cristal ou ressonador de alta velocidade é conectado através dos pinos XIN e XOUT, e um capacitor externo é necessário. O tamanho do capacitor é selecionado de acordo com as características do oscilador de cristal ou ressonador.

Se o sinal LFXT1CLK não for usado como sinal SMCLK ou MCIK, o software pode definir OSCOFF=1 para desativar o LFXT1, reduzindo assim o consumo de energia do microcontrolador.

BCSCTL1:

XTS(BIT6)——Seleção do modo de alta/baixa velocidade do LFXT1. 0: O LFXT1 funciona no modo oscilador de cristal de baixa velocidade (padrão); 1: O LFXT1 funciona no modo oscilador de cristal de alta velocidade.

2. XT2CLK de alta frequência (8 MHz)

Um oscilador de cristal padrão, oscilador ou fonte de clock externa pode ser usado para entrar 4 MHz~32 MHz.

O oscilador XT2 gera o sinal de relógio XT2CLK e suas características de funcionamento são semelhantes às do oscilador LFXT1 quando funciona no modo de alta frequência. Se o XT2CLK não for usado como sinal de relógio MCLK e SMCLK, o oscilador XT2 pode ser desativado com o bit de controle XT2OFF.

BCSCTL1:

XT2OFF (BIT7) – Controle do oscilador de cristal de alta velocidade XT2. 0: Oscilador de cristal de alta velocidade XT2 ligado; 1: Oscilador de cristal de alta velocidade XT2 desligado.

3. Oscilador interno DCOCLK (1 MHz)

Estabilizado pelo módulo FLL.

Quando o oscilador falha, o DCO é automaticamente selecionado como fonte de clock para o MCLK.

A frequência do oscilador DCO pode ser ajustada por software, definindo os bits DCOx. MODx e RSEL.x. Quando o sinal DCOCLK não é usado como sinal de clock SMCLK e MCLK, o gerador DC pode ser desativado com o bit de controle SCGO.

Após o sinal PUC, o DCOCLK é automaticamente selecionado como o sinal de clock MCLK, e a fonte de clock do MCLK pode ser adicionalmente definida como LFXT1 ou XT2, conforme necessário. A sequência de configuração é a seguinte:

- Deixe OSCOFF=1;

- Deixe OFIFG=0;

- Adiar e aguardar pelo menos 50 ps;

- Verifique OFIFG novamente, se OFIFG=1, repita os passos (3) e (4) até OFIFG=0.

DCOCTL:

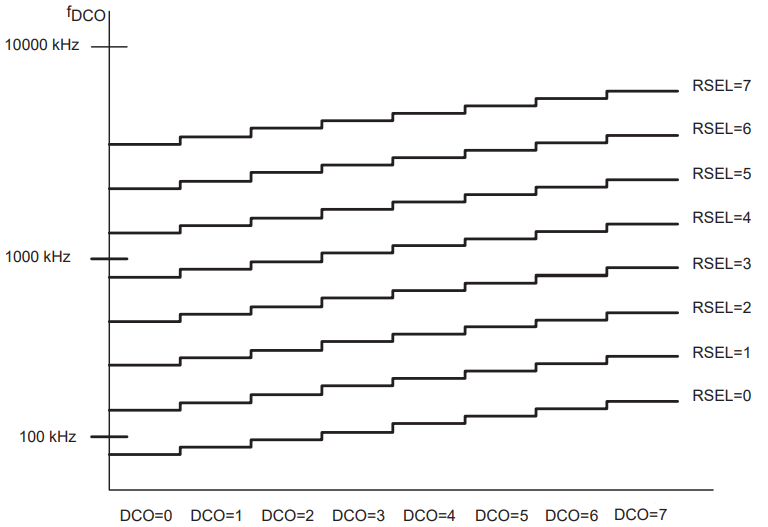

DCOx (BIT7, BIT6, BIT5)——Seleção da frequência DCO, 8 tipos de frequências podem ser selecionados e a frequência DCOCLK pode ser ajustada em seções. A seleção da frequência é baseada na banda de frequência selecionada por RSELx. A relação entre DCOx, RSELx e o relógio interno é a seguinte:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) – Configuração do modulador DAC. O controle alterna entre as duas frequências selecionadas por DCOx e DCOx+1 para ajustar com precisão a frequência de saída do DCO. Se a constante DCOx for 7, isso significa que a frequência mais alta foi selecionada. Nesse momento, MODx é inválido e não pode ser usado para ajuste de frequência.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0) – a seleção da banda de frequência do oscilador DCO, esses 3 bits controlam uma resistência interna para determinar a frequência nominal. 0: Selecione a frequência nominal mais baixa… 7: Selecione a frequência nominal mais alta.

BCSCTL2:

DCOR(BIT0)——Seleciona a resistência do oscilador DCO. 0: resistência interna; 1: resistência externa.

Três fontes de relógio

1. Relógio auxiliar ACLK

O ACLK é obtido após o LFXT1CLK ser dividido por 1, 2, 4 e 8. Ele pode ser usado como sinal de clock de cada módulo periférico e é geralmente usado para periféricos de baixa velocidade.

BCSCTL1:

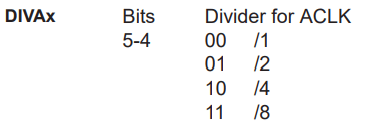

DIVAx (BIT5, BIT4)——Seleção da divisão de frequência ACLK, a relação de seleção da divisão de frequência é a seguinte:

Definição macro: DIVA_0 (1 divisão de frequência/sem divisão de frequência), DIVA_1 (2 divisões de frequência), DIVA_2 (4 divisões de frequência), DIVA_3 (8 divisões de frequência)

2. Relógio principal do sistema MCLK

O MCLK pode ser obtido a partir do LFXT1CLK, XT2CLK e DCOCLK após divisão de frequência por 1, 2, 4 e 8. É frequentemente utilizado para o funcionamento da CPU, execução de programas e outros módulos que utilizam relógios de alta velocidade.

BCSCTL2:

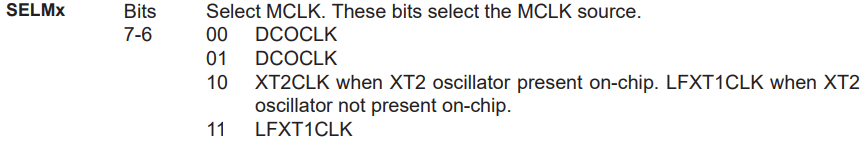

SELMx (BIT7, BIT6) – seleciona a fonte do relógio MCLK, a relação de seleção do relógio é a seguinte:

Definição macro: SELM_0 (DCOCLK padrão), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

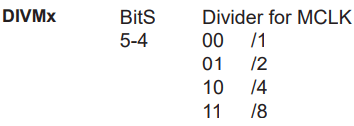

DIVMx (BIT5, BIT4) – Seleção da divisão de frequência MCLK, a relação de seleção da divisão de frequência é a seguinte:

Definição macro: DIVM_0 (1 divisão de frequência/sem divisão de frequência), DIVM_1 (2 divisões de frequência), DIVM_2 (4 divisões de frequência), DIVM_3 (8 divisões de frequência)

3. Relógio do subsistema SMCLK

O SMCLK pode ser obtido pela divisão de frequência do XT2CLK e do DCOCLK por 1, 2, 4 e 8, e é frequentemente utilizado em módulos periféricos de alta velocidade.

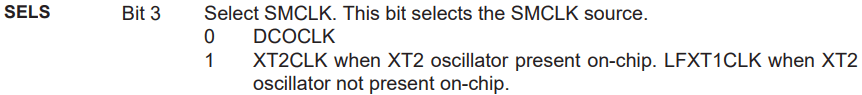

BCSCTL2:

SELSx (BIT3) – selecione a fonte de clock MCLK, a relação de seleção de clock é a seguinte:

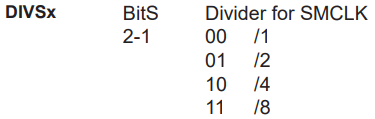

DIVSx (BIT2, BIT1) – Seleção da divisão de frequência SMCLK, a relação de seleção da divisão de frequência é a seguinte:

Definição macro: DIVS_0 (1 divisão de frequência/sem divisão de frequência), DIVS_1 (2 divisões de frequência), DIVS_2 (4 divisões de frequência), DIVS_3 (8 divisões de frequência)