FPGA, abbreviazione di Field Programmable Gate Array, è un’architettura hardware riconfigurabile. In altre parole, è un chip che può essere programmato per cambiare la sua struttura interna. Gli FPGA sono stati utilizzati per molti anni come sostituto a basso volume per i chip specifici per l’applicazione (ASIC).

Struttura base di FPGA

L’architettura FPGA include principalmente quattro parti: blocco logico configurabile (CLB), blocco di input e output (IOB), cablaggio interno (Interconnect) e altre unità incorporate. La struttura interna del dispositivo FPGA è mostrata di seguito.

Blocco logico configurabile (CLB)

CLB è l’unità logica di base di FPGA. Il numero effettivo e le caratteristiche variano da dispositivo a dispositivo, ma ogni CLB contiene una matrice di commutazione configurabile di 4 o 6 ingressi, diversi circuiti di selezione (multiplexer, ecc.) e flip-flop.

Blocco di input e output (IOB)

Gli FPGA possono supportare molti standard di I/O, rendendoli un ponte di interfaccia ideale per i progetti di sistema. L’I/O nell’FPGA è raggruppato per banca e ogni banca può supportare in modo indipendente diversi standard di I/O. Attualmente, l’FPGA più avanzato fornisce più di dieci banche di I/O, che possono fornire un supporto di I/O flessibile.

Cablaggio interno (Interconnect)

I CLB forniscono le prestazioni logiche e il routing di interconnessione flessibile è responsabile del passaggio dei segnali tra i CLB e gli I/O. Esistono diversi tipi di routing, che vanno dalle interconnessioni CLB dedicate (risorse a filo corto) ai fili lunghi orizzontali e verticali ad alta velocità (risorse a filo lungo) all’interno del dispositivo, al routing globale a bassa distorsione per clock e altri segnali globali (risorse di routing dedicate globali).

Unità incorporate

Le unità hard core incorporate includono RAM, DSP, DCM (Digital Clock Management Module) e altre hard core di interfaccia specifiche, ecc.

Caratteristiche FPGA

- Utilizzando FPGA per progettare circuiti ASIC, il ciclo è breve, il costo è basso, il rischio è piccolo e la qualità è stabile;

- FPGA adotta la tecnologia CHMOS ad alta velocità a basso consumo energetico;

- Architettura FPGA, unità logica flessibile, elevata integrazione, ampia gamma di applicazioni;

- FPGA è compatibile con i vantaggi di PLD e array di gate generici e può realizzare circuiti su larga scala;

- È possibile la riprogrammazione in loco e il costo di manutenzione successivo è basso;

- FPGA è un calcolo parallelo in grado di soddisfare requisiti multifunzionali contemporaneamente.

Come funziona FPGA?

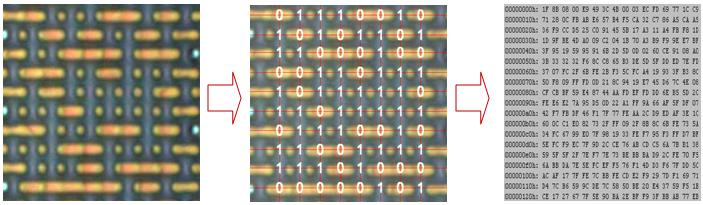

FPGA implementa funzioni logiche caricando dati di programmazione in unità di archiviazione statiche interne. Il valore memorizzato nell’unità di archiviazione determina la funzione logica dell’unità logica e la modalità di connessione tra ciascun modulo di unità logica o tra il modulo e I/O, e infine determina la funzione realizzata da FPGA. FPGA utilizza una piccola tabella di ricerca per implementare la logica combinatoria, ogni tabella di ricerca è collegata all’ingresso di un flip-flop D e il flip-flop D viene utilizzato per pilotare altri circuiti logici o I/O, formando così una funzione logica combinata e realizzando il modulo di unità logica di base della funzione logica sequenziale, questi moduli sono collegati tra loro o al modulo I/O tramite fili metallici.

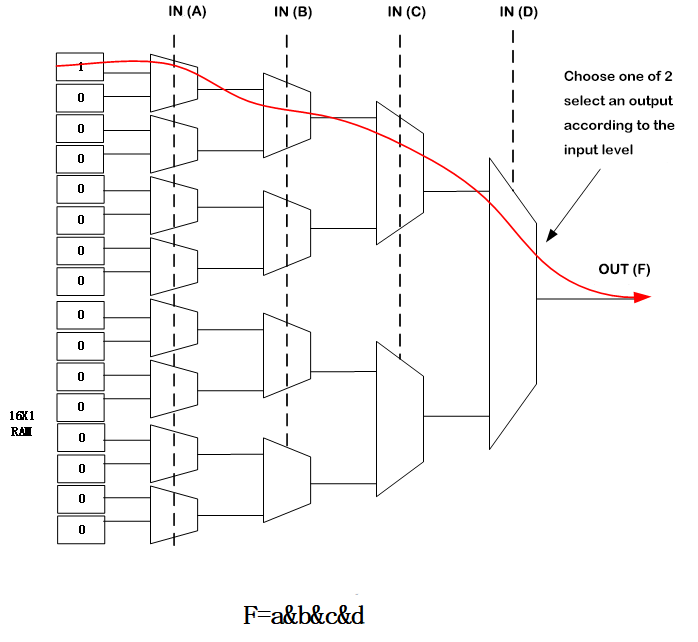

Ecco un semplice esempio per spiegare il principio dell’FPGA:

Come mostrato nella figura sopra, configuriamo 16bitRAM come 0000000000000001 e questo circuito è equivalente a F=A&B&C&D;

Solo quando A=B=C=D=1, F=1, altrimenti F=0;

“0000000000000001” Questa stringa di numeri è la programmazione FPGA.

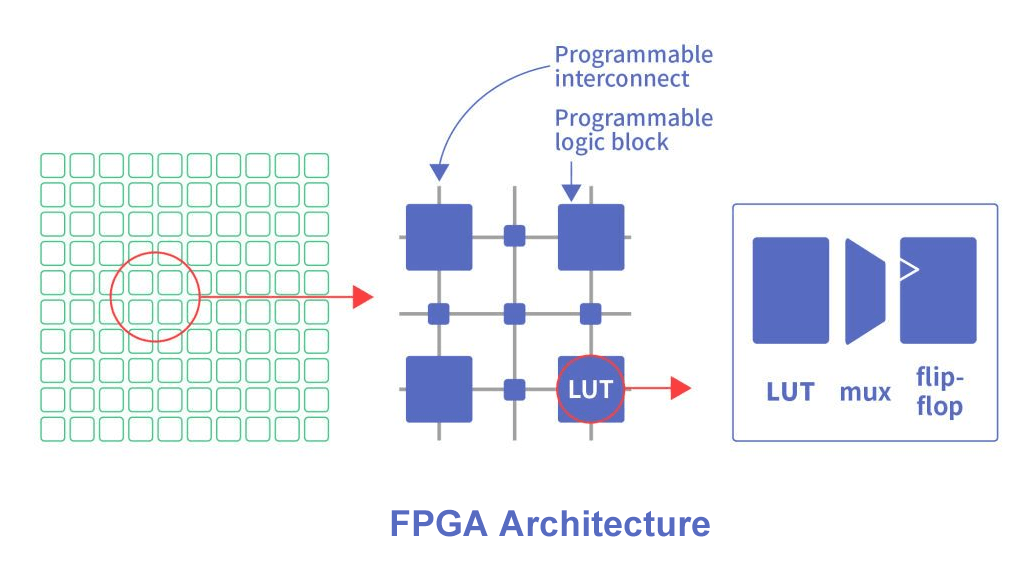

Blocco logico di FPGA

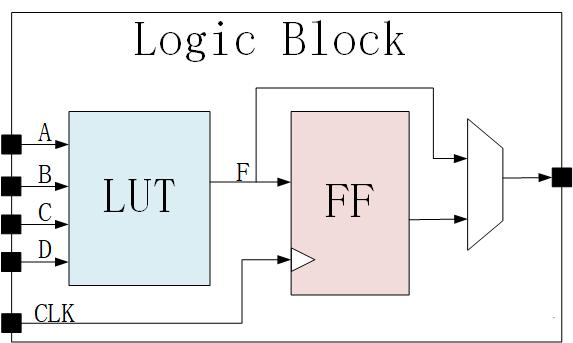

In FPGA esiste un termine appropriato, chiamato LUT, tabella di ricerca (lookup table).

La LUT costituisce l’unità più basilare di qualsiasi FPGA.

La LUT può implementare solo la logica combinatoria digitale, quindi un flip-flop di registro (ff) viene aggiunto per realizzare il latch dei dati;

Come mostrato nella figura seguente: LUT + registri formano la struttura di base degli FPGA moderni.

Processo di sviluppo FPGA

Il processo di sviluppo FPGA è il processo di utilizzo di software di sviluppo EDA e strumenti di programmazione per sviluppare chip FPGA. Il processo di sviluppo di FPGA è generalmente mostrato nella figura seguente, inclusi i passaggi principali come la definizione della funzione/selezione del dispositivo, l’input di progettazione, la simulazione della funzione, la sintesi logica, il layout e il routing e l’implementazione, la programmazione e il debug.

Definizione della funzione/selezione del dispositivo:

Prima che inizi il progetto di progettazione FPGA, deve esserci una definizione delle funzioni di sistema e una divisione dei moduli. Inoltre, in base ai requisiti dell’attività, come la funzione e la complessità del sistema, la velocità di lavoro e le risorse, i costi e le connessioni del dispositivo stesso possono essere distribuiti. Compromessi su aspetti come le prestazioni e la selezione dello schema di progettazione appropriato e del tipo di dispositivo appropriato.

Input di progettazione:

L’input di progettazione si riferisce all’uso di un linguaggio di descrizione hardware per esprimere il sistema o il circuito progettato in codice. Il linguaggio di descrizione hardware più comunemente usato è Verilog HDL.

Simulazione funzionale:

La simulazione funzionale si riferisce alla verifica della funzione logica del circuito progettato dall’utente prima della sintesi logica. Prima della simulazione, è necessario costruire una piattaforma di test e preparare stimoli di test. I risultati della simulazione genereranno file di report e uscite di forme d’onda del segnale, da cui è possibile osservare le variazioni dei segnali di ciascun nodo. Se vengono trovati errori, tornare al progetto per rivedere il progetto logico. Gli strumenti di simulazione comuni includono ModelSim di Model Tech, VCS di Sysnopsys e altri software.

Sintesi logica:

La cosiddetta sintesi consiste nel trasformare la descrizione di un livello di astrazione superiore nella descrizione di un livello inferiore. L’ottimizzazione sintetica ottimizza le connessioni logiche generate in base agli obiettivi e ai requisiti e rende il progetto gerarchico planare per il software di layout e routing FPGA per l’implementazione. Per quanto riguarda il livello corrente, l’ottimizzazione completa si riferisce alla compilazione dell’input di progettazione in un netlist logicamente connesso composto da unità logiche di base come porte AND, porte OR, porte NOT, RAM e flip-flop, piuttosto che circuiti a livello di gate reali.

Layout e implementazione:

Layout e routing possono essere intesi come l’utilizzo di strumenti di implementazione per mappare la logica alle risorse della struttura del dispositivo di destinazione, determinare il layout ottimale della logica, selezionare i canali di cablaggio collegati dalla logica e dalle funzioni di input e output e generare file corrispondenti (come file di configurazione e report correlati); l’implementazione consiste nel configurare il netlist logico generato dalla sintesi a un chip FPGA specifico. Poiché solo il produttore del chip FPGA conosce meglio la struttura del chip, il layout e il routing devono scegliere gli strumenti forniti dallo sviluppatore del chip.

Debug di programmazione:

L’ultimo passaggio del progetto è la programmazione e il debug. La programmazione del chip si riferisce alla generazione di file di dati (file di flusso bit, Bitstream Generaon) e al caricamento dei dati di programmazione nel chip FPGA; dopo di ciò, è possibile eseguire il test della scheda. Infine, scaricare il file FPGA (come il file .bit) dal computer al chip FPGA sulla scheda.

FPGA Vs. CPU e GPU

Sia le CPU che le GPU seguono l’architettura di von Neumann con decodifica delle istruzioni e memoria condivisa. Al contrario, le FPGA hanno un’architettura intrinsecamente diversa che non si basa sulle istruzioni o richiede memoria condivisa. La tabella sottostante mostra le loro differenze:

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Competenze richieste per gli ingegneri FPGA

- Linguaggio Verilog e la sua relazione con i circuiti hardware

- Strumenti di sviluppo (competenti in Synplify, vivodo, ISE, Modelsim)

- Familiarità con il processo di progettazione FPGA (simulazione, sintesi, layout e routing, analisi dei tempi)

- Competenza nella stima delle risorse (in particolare la stima di slice, lut, ram e altre risorse)

- Competenza nei concetti di base (come tempo di setup, tempo di hold, calcolo del flusso, calcolo del ritardo, rischio competitivo, metodi per eliminare i glitch, ecc.)

- Circuiti digitali (circuiti combinatori, flip-flop, in particolare i flip-flop D costituiscono un divisore di frequenza, circuiti sequenziali e possono essere descritti nel linguaggio Verilog)

Produttori di FPGA

- Xilinx: la piattaforma di sviluppo è ISE, l’inventore di FPGA;

- Altera: la piattaforma di sviluppo è Quartus II, l’inventore di dispositivi logici programmabili;

- Actel: la piattaforma di sviluppo è Libero;

- Lattice: la piattaforma di sviluppo è ISPLEVER;

- Atmel