FPGA, singkatan dari Field Programmable Gate Array, adalah arsitektur perangkat keras yang dapat dikonfigurasi ulang. Dengan kata lain, FPGA adalah chip yang dapat diprogram untuk mengubah struktur internalnya. FPGA telah digunakan selama bertahun-tahun sebagai alternatif berproduksi rendah untuk chip khusus aplikasi (ASIC).

Struktur Dasar FPGA

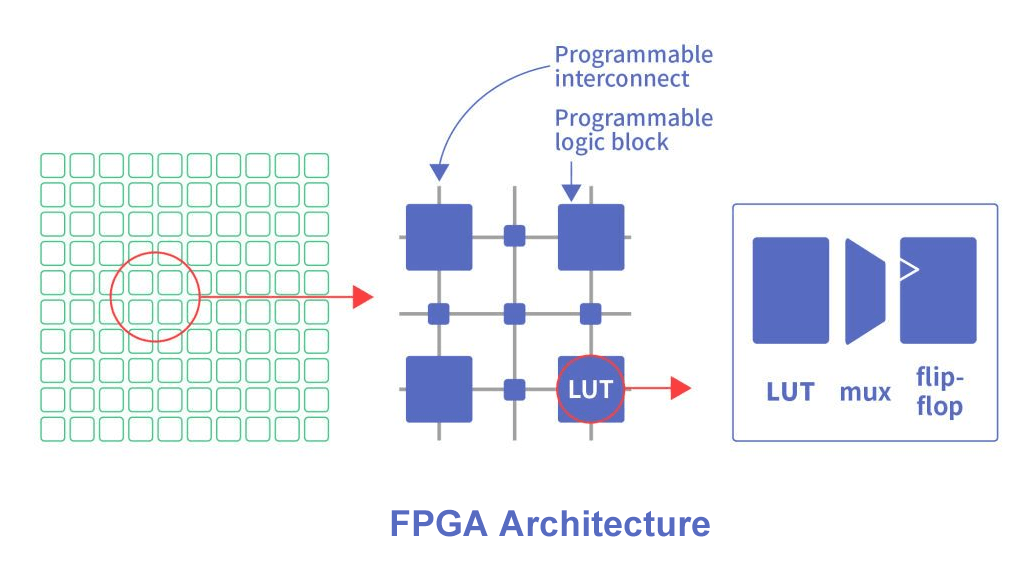

Arsitektur FPGA pada dasarnya terdiri dari empat bagian: blok logika yang dapat dikonfigurasi (CLB), blok input dan output (IOB), penghubung internal (Interconnect), serta unit tertanam lainnya. Struktur internal perangkat FPGA ditunjukkan di bawah ini.

Blok Logika yang Dapat Dikonfigurasi (CLB)

CLB adalah unit logika dasar pada FPGA. Jumlah dan karakteristiknya dapat bervariasi antar perangkat, namun setiap CLB terdiri dari matriks sakelar yang dapat dikonfigurasi dengan 4 atau 6 saluran masukan, beberapa sirkuit selektor (multiplexer, dll.), serta flip-flop.

Blok Masukan dan Keluaran (IOB)

FPGA dapat mendukung berbagai standar I/O, sehingga menjadikannya jembatan antarmuka yang ideal untuk desain sistem. I/O dalam FPGA dikelompokkan berdasarkan bank, dan setiap bank dapat secara mandiri mendukung standar I/O yang berbeda. Saat ini, FPGA paling canggih menyediakan lebih dari sepuluh bank I/O, yang dapat memberikan dukungan I/O yang fleksibel.

Pemasangan Kabel Internal (Interkoneksi)

CLB menyediakan fungsi logika, sedangkan rute interkoneksi yang fleksibel bertugas meneruskan sinyal antara CLB dan I/O. Terdapat beberapa jenis rute, mulai dari interkoneksi CLB khusus (sumber daya kabel pendek), hingga kabel panjang horizontal dan vertikal berkecepatan tinggi (sumber daya kabel panjang) di dalam perangkat, hingga rute global dengan skew rendah untuk sinyal jam dan sinyal global lainnya (sumber daya rute global khusus).

Unit Tertanam

Unit inti tertanam meliputi RAM, DSP, DCM (Modul Manajemen Jam Digital), serta unit inti antarmuka khusus lainnya, dan sebagainya.

Fitur FPGA

- Dengan menggunakan FPGA untuk merancang sirkuit ASIC, siklus pengembangannya singkat, biayanya rendah, risikonya kecil, dan kualitasnya stabil;

- FPGA menggunakan teknologi CMOS berkecepatan tinggi dengan konsumsi daya rendah;

- Arsitektur FPGA, unit logika yang fleksibel, integrasi tinggi, dan jangkauan aplikasi yang luas;

- FPGA menggabungkan keunggulan PLD dan gate array umum, serta mampu merealisasikan sirkuit berskala besar;

- Pemrograman ulang di tempat dimungkinkan, dan biaya pemeliharaan selanjutnya rendah;

- FPGA adalah komputasi paralel yang dapat memenuhi berbagai kebutuhan fungsional secara bersamaan.

Bagaimana Cara Kerja FPGA?

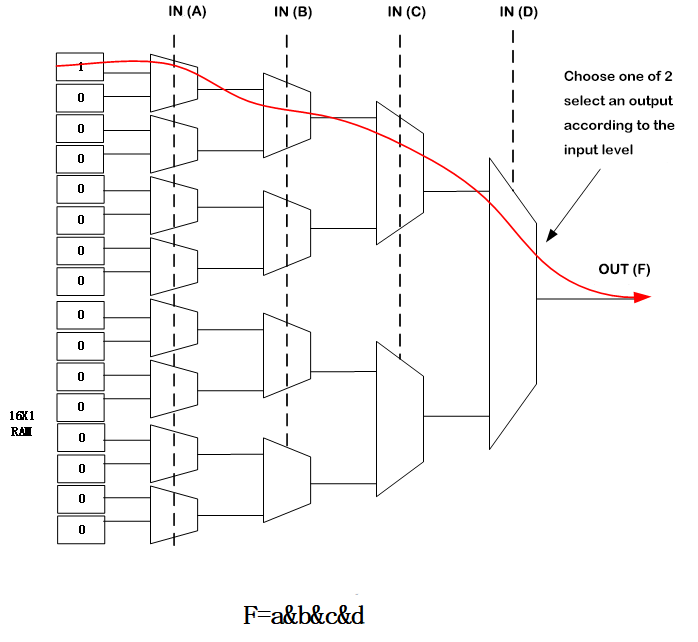

FPGA mengimplementasikan fungsi logika dengan memuat data pemrograman ke unit penyimpanan statis internal. Nilai yang disimpan dalam unit penyimpanan tersebut menentukan fungsi logika dari unit logika tersebut serta mode koneksi antar modul unit logika atau antara modul dan I/O, dan pada akhirnya menentukan fungsi yang direalisasikan oleh FPGA. FPGA menggunakan tabel pencarian kecil untuk mengimplementasikan logika kombinatorial; setiap tabel pencarian terhubung ke input flip-flop D, dan flip-flop D digunakan untuk menggerakkan sirkuit logika lain atau I/O, sehingga membentuk fungsi logika kombinatorial dan merealisasikan modul unit logika dasar dari fungsi logika sekuensial; modul-modul ini terhubung satu sama lain atau ke modul I/O melalui kabel logam.

Berikut adalah contoh sederhana untuk menjelaskan prinsip kerja FPGA:

Seperti yang ditunjukkan pada gambar di atas, kami mengonfigurasi 16bitRAM sebagai 0000000000000001, dan rangkaian ini setara dengan F=A&B&C&D;

Hanya ketika A=B=C=D=1, F=1, sebaliknya F=0;

"0000000000000001" Rangkaian angka ini adalah program FPGA.

Blok Logika FPGA

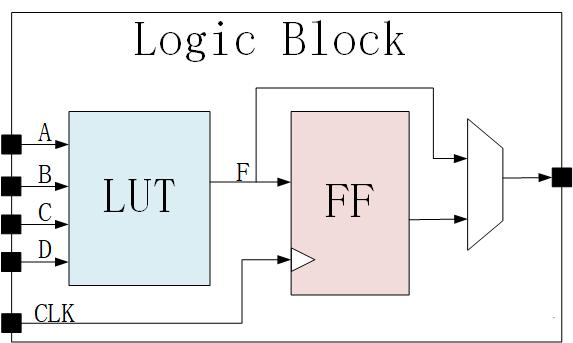

Ada istilah khusus dalam FPGA yang disebut LUT, singkatan dari lookup table (tabel pencarian).

LUT merupakan unit paling dasar dari setiap FPGA.

LUT hanya dapat mengimplementasikan logika kombinatorial digital, sehingga flip-flop register (ff) ditambahkan untuk merealisasikan penahanan data;

Seperti yang ditunjukkan pada gambar di bawah ini: LUT dan register membentuk struktur dasar FPGA modern.

Proses Pengembangan FPGA

Proses pengembangan FPGA adalah proses penggunaan perangkat lunak pengembangan EDA dan alat pemrograman untuk mengembangkan chip FPGA. Proses pengembangan FPGA secara umum ditunjukkan pada gambar di bawah ini, yang mencakup langkah-langkah utama seperti definisi fungsi/pemilihan perangkat, masukan desain, simulasi fungsi, sintesis logika, tata letak dan perutean serta implementasi, pemrograman, dan debugging.

Definisi fungsi/pemilihan perangkat:

Sebelum proyek desain FPGA dimulai, harus ada definisi fungsi sistem dan pembagian modul. Selain itu, sesuai dengan persyaratan tugas, seperti fungsi dan kompleksitas sistem, kecepatan kerja, serta sumber daya, biaya, dan koneksi perangkat itu sendiri, dapat didistribusikan. Pertimbangkan aspek-aspek seperti kinerja dan pilih skema desain yang tepat serta jenis perangkat yang sesuai.

Masukan desain:

Masukan desain mengacu pada penggunaan bahasa deskripsi perangkat keras untuk menggambarkan sistem atau rangkaian yang dirancang dalam bentuk kode. Bahasa deskripsi perangkat keras yang paling umum digunakan adalah Verilog HDL.

Simulasi fungsional:

Simulasi fungsional mengacu pada verifikasi fungsi logika rangkaian yang dirancang oleh pengguna sebelum sintesis logika. Sebelum melakukan simulasi, perlu membangun platform uji dan menyiapkan stimulus uji. Hasil simulasi akan menghasilkan berkas laporan dan bentuk gelombang sinyal keluaran, dari mana perubahan sinyal pada setiap node dapat diamati. Jika ditemukan kesalahan, kembali ke tahap desain untuk merevisi desain logika. Alat simulasi yang umum digunakan antara lain ModelSim dari Model Tech, VCS dari Sysnopsys, dan perangkat lunak lainnya.

Sintesis logis:

Yang disebut sintesis adalah proses mengubah deskripsi pada tingkat abstraksi yang lebih tinggi menjadi deskripsi pada tingkat yang lebih rendah. Optimisasi sintetik mengoptimalkan koneksi logika yang dihasilkan sesuai dengan tujuan dan persyaratan, serta mengubah desain hierarkis menjadi desain planar agar dapat diimplementasikan oleh perangkat lunak tata letak dan rute FPGA. Sejauh tingkat saat ini, optimisasi komprehensif mengacu pada kompilasi masukan desain menjadi daftar jaringan (netlist) yang terhubung secara logis, yang terdiri dari unit logika dasar seperti gerbang AND, gerbang OR, gerbang NOT, RAM, dan flip-flop, bukan sirkuit tingkat gerbang yang sebenarnya.

Tata letak dan implementasi:

Tata letak dan perutean dapat dipahami sebagai penggunaan alat implementasi untuk memetakan logika ke sumber daya struktur perangkat target, menentukan tata letak logika yang optimal, memilih saluran pengkabelan yang dihubungkan oleh logika serta fungsi masukan dan keluaran, serta menghasilkan berkas-berkas terkait (seperti berkas konfigurasi dan laporan terkait); sedangkan implementasi adalah mengonfigurasi daftar jaringan logika yang dihasilkan oleh sintesis ke chip FPGA tertentu. Karena hanya pabrikan chip FPGA yang paling memahami struktur chip tersebut, tata letak dan rute harus menggunakan alat yang disediakan oleh pengembang chip.

Pemeriksaan kesalahan dalam pemrograman:

Langkah terakhir dalam proses desain adalah pemrograman dan debugging. Pemrograman chip mengacu pada pembuatan berkas data (berkas bit stream, Bitstream Generation), serta pemuatan data pemrograman ke dalam chip FPGA; setelah itu, pengujian papan dapat dilakukan. Terakhir, unduh berkas FPGA (seperti berkas .bit) dari komputer ke chip FPGA pada papan.

FPGA vs. CPU dan GPU

Baik CPU maupun GPU menggunakan arsitektur von Neumann yang mencakup dekodasi instruksi dan memori bersama. Sebaliknya, FPGA memiliki arsitektur yang secara inheren berbeda, yang tidak bergantung pada instruksi maupun memerlukan memori bersama. Tabel di bawah ini menunjukkan perbedaannya:

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Keterampilan yang Diperlukan bagi Insinyur FPGA

- Bahasa Verilog dan hubungannya dengan sirkuit perangkat keras

- Alat pengembangan (mahir dalam Synplify, Vivado, ISE, Modelsim)

- Terbiasa dengan proses desain FPGA (simulasi, sintesis, tata letak dan perutean, analisis waktu)

- Mahir dalam estimasi sumber daya (terutama estimasi slice, lut, ram, dan sumber daya lainnya)

- Mahir dalam konsep dasar (seperti waktu setup, waktu hold, perhitungan aliran, perhitungan waktu tunda, risiko kompetitif, metode untuk menghilangkan glitch, dll.)

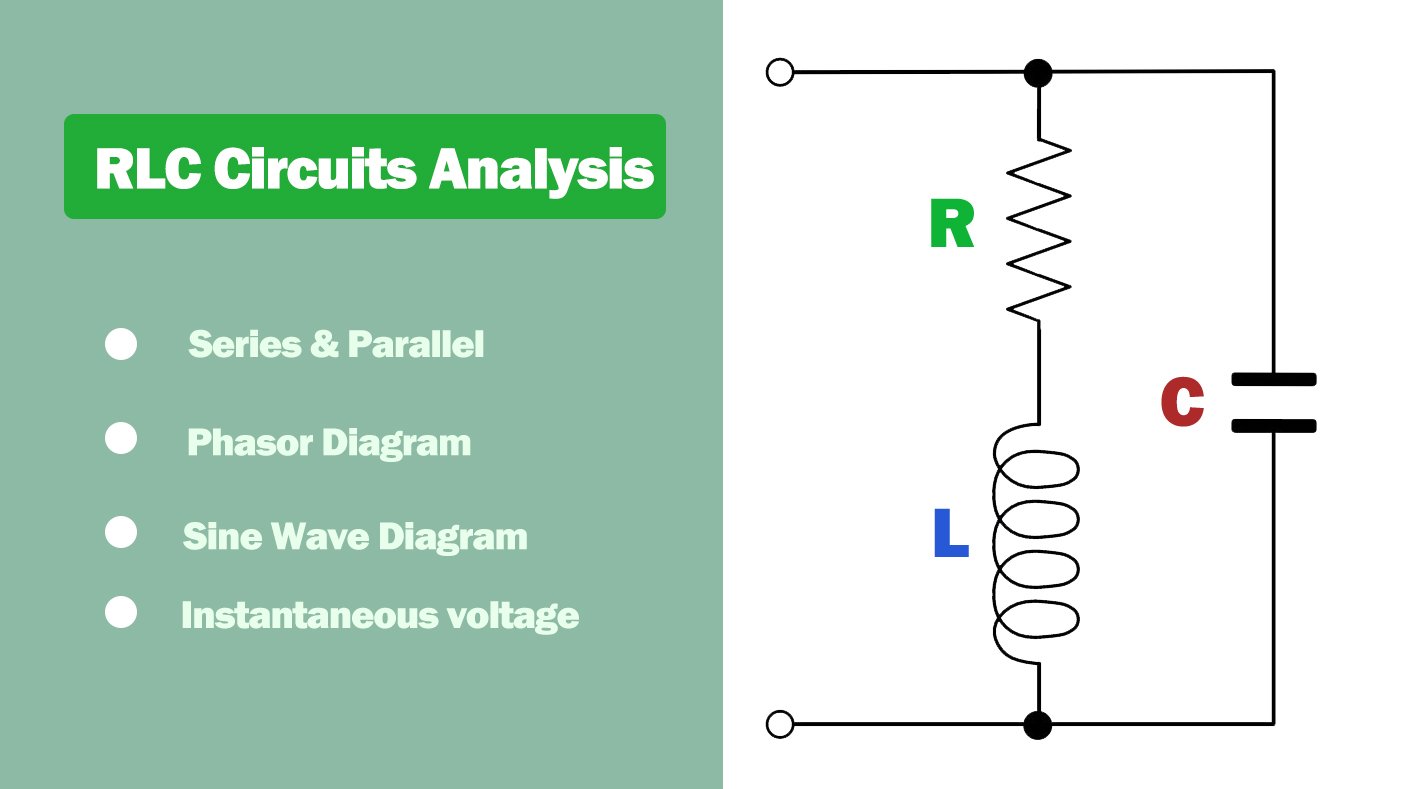

- Sirkuit digital (sirkuit kombinasi, flip-flop, terutama D flip-flop yang membentuk pembagi frekuensi, sirkuit sekuensial, dan dapat dijelaskan dalam bahasa Verilog)

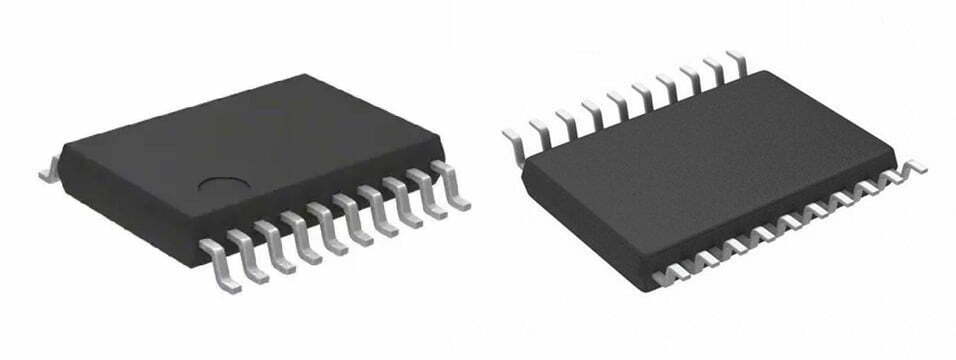

Produsen FPGA

- Xilinx: platform pengembangannya adalah ISE, penemu FPGA;

- Altera: platform pengembangannya adalah Quartus II, penemu perangkat logika yang dapat diprogram;

- Actel: platform pengembangannya adalah Libero;

- Lattice: platform pengembangannya adalah ISPLEVER;

- Atmel