A placa central STM32F103C8T6 é baseada no chip microcontrolador oficial ST STM32F103C8T6. Esta placa compacta e versátil foi meticulosamente projetada para criar uma configuração de sistema mínima, tornando-a a escolha ideal para vários projetos de sistemas embarcados. Ela oferece uma variedade de componentes essenciais, incluindo circuitos para seleção do modo BOOT, desacoplamento, oscilador de cristal, download SWD, funcionalidade de reinicialização, indicação de energia e interface de porta IO periférica. Com seu design cuidadosamente pensado, a placa pode ser facilmente integrada e expandida para uso com outras placas-base. Sua eficiência energética e recursos robustos a tornam uma ferramenta valiosa para desenvolvedores, permitindo-lhes construir e experimentar aplicações inovadoras na plataforma STM32F103C8T6.

Descrição do projeto STM32F103C8T6

Este projeto utiliza o chip oficial ST STM32F103C8T6 e projeta uma placa de sistema mínima, que pode ser facilmente expandida e utilizada com a placa-base.

- Os circuitos projetados incluem circuito BOOT, circuito de desacoplamento, circuito oscilador de cristal, circuito de download SWD, circuito de reinicialização, circuito indicador de energia e circuito de porta IO periférica.

- A placa é alimentada por meio de conexões externas ao pino +3V3 e ao pino GND. Recomenda-se alimentar a placa dentro da faixa de 3,3 V a 3,6 V, e é melhor não exceder 3,6 V de alimentação.

- Um circuito indicador de alimentação +3V3 foi projetado para indicar convenientemente se a entrada de alimentação está normal.

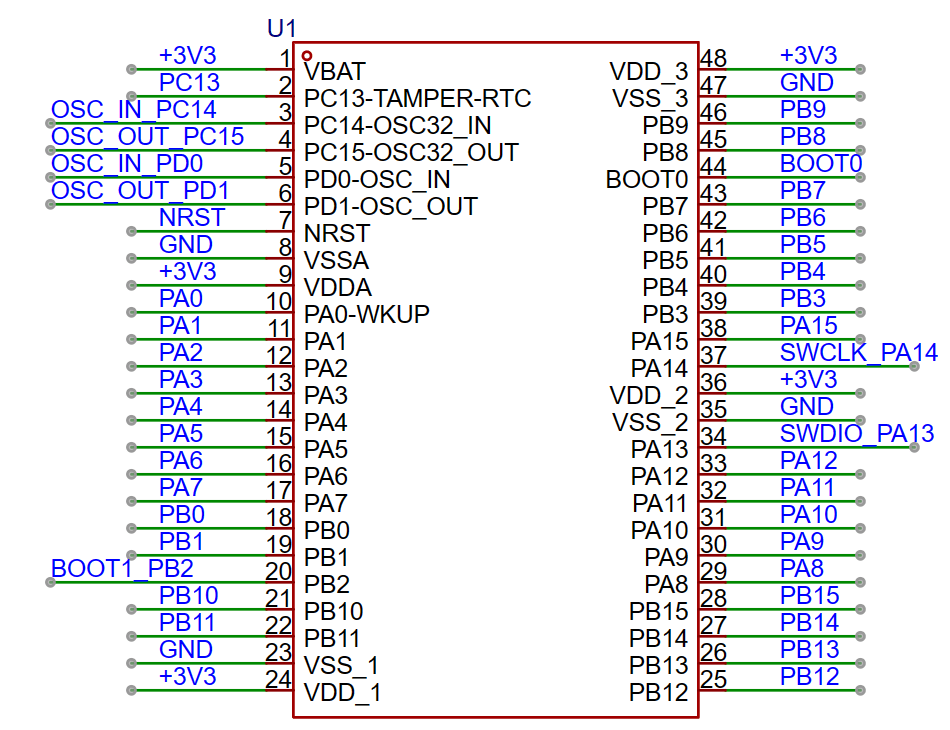

Pinagem do STM32F103C8T6

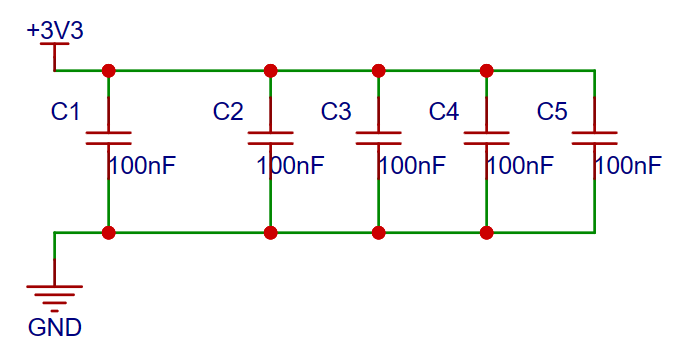

Circuito de desacoplamento

Diagrama esquemático

Colocar um capacitor 104 (0,1 μF) nos pinos de alimentação suprime eficazmente o ruído na fonte de alimentação, o que é conhecido como desacoplamento do ruído da fonte de alimentação.

Quanto mais próximos estiverem os pontos "Alimentação – Capacitor de Desacoplamento – Terra", melhor será o efeito de desacoplamento.

Para capacitores do mesmo material, mesmo que a capacitância diminua para 1/10, o efeito de desacoplamento não muda significativamente. Para desacoplamento de alta frequência, capacitores com o mesmo pacote, valores de capacitância de 0,01μF, 0,1μF e 1μF apresentam resultados semelhantes.

Os capacitores de montagem em superfície (SMD) têm melhores efeitos de desacoplamento do que os capacitores de furo passante com a mesma capacitância, devido à maior indutância equivalente dos capacitores de furo passante, que afeta o efeito de desacoplamento.

O capacitor com a menor capacitância tem a frequência de ressonância mais alta e o menor raio de desacoplamento. Portanto, ele deve ser colocado o mais próximo possível do chip.

Capacitores com capacitância ligeiramente maior podem ser colocados um pouco mais longe, e a maior capacitância deve ser colocada na camada mais externa. No entanto, todos os capacitores para desacoplamento deste chip devem ser colocados o mais próximo possível do chip.

Para projetos de PCB de alta velocidade, é melhor colocar os capacitores no mesmo lado do chip para obter um melhor desacoplamento. Para capacitores de desacoplamento do tipo MCU, não há uma diferença significativa entre colocá-los na parte frontal ou traseira.

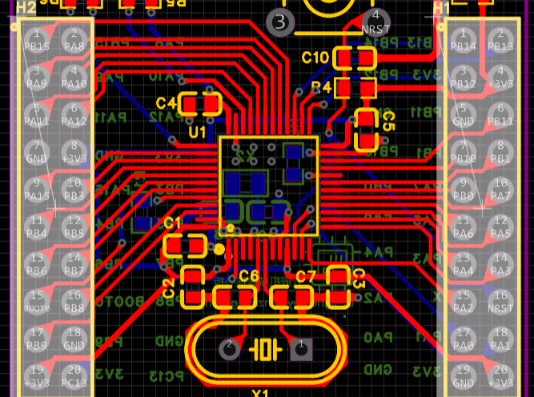

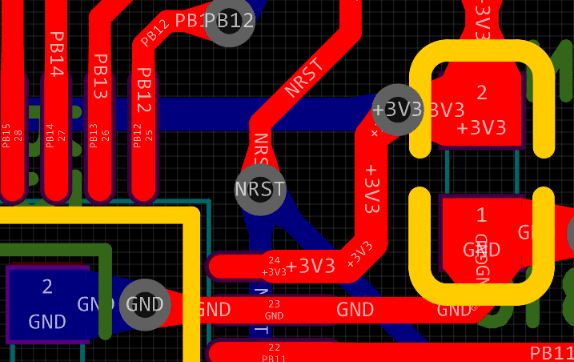

Design de PCB

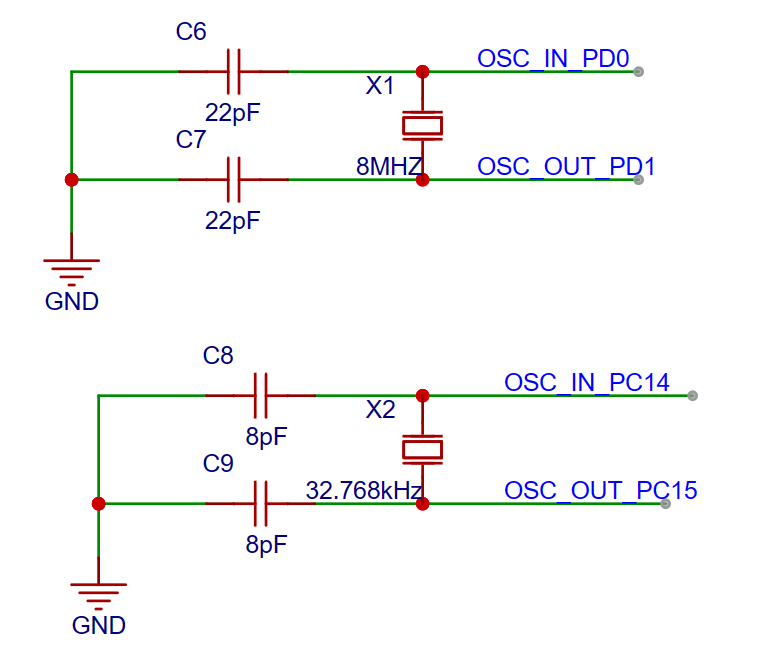

Circuito oscilador de cristal

Diagrama esquemático

O STM32 tem três fontes de clock internas, mas a árvore de clock do chip de 32 bits requer cinco fontes de clock. Portanto, o PCB precisa acomodar clocks externos de alta e baixa velocidade.

O relógio externo de alta velocidade pode ser um ressonador de quartzo/cerâmica ou uma fonte de relógio externa, com uma faixa de frequência de 4 MHz a 16 MHz. Uma escolha comum é um oscilador de cristal de 8 MHz para a frequência principal do sistema.

O relógio externo de baixa velocidade é um cristal de quartzo com uma frequência de 32,768 kHz, usado para acionar o relógio RTC.

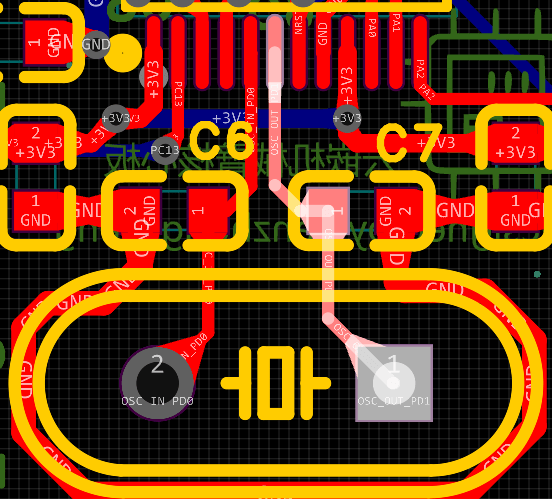

Design de PCB

Observe que a área ao redor do oscilador de cristal é cercada por traços GND, e é aconselhável adicionar vias nesses traços GND. Isso é feito para isolar o oscilador de cristal. Além disso, evite passar traços nas camadas superior e inferior da área onde o oscilador de cristal está localizado, pois isso pode afetar a integridade do sinal.

Além disso, os dois capacitores próximos ao oscilador de cristal devem ser posicionados simetricamente.

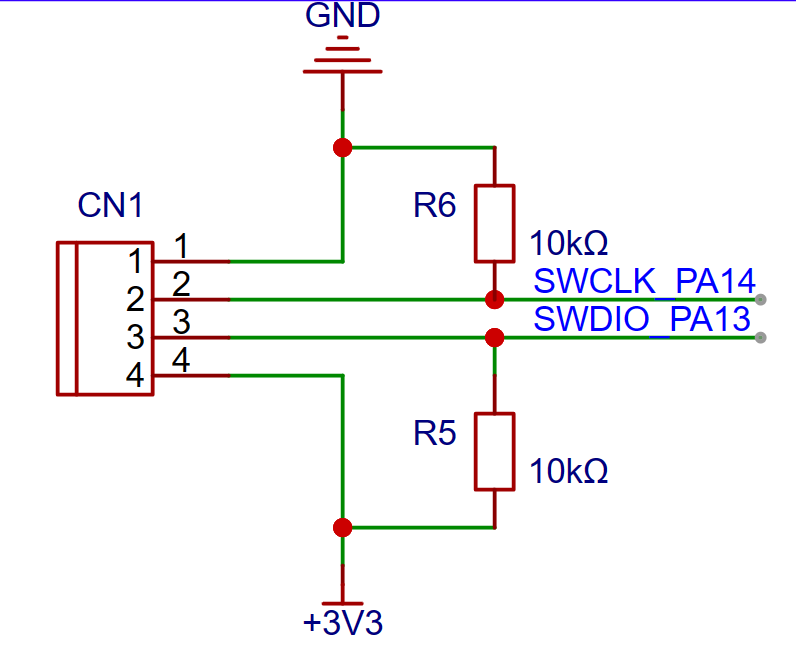

Circuito de download SWD

Diagrama esquemático

Introdução ao JTAG:

Normalmente utilizamos o downloader Jlink, que tem a desvantagem de usar a interface Jtag 20PIN. O número excessivo de pinos pode causar congestionamento em placas PCB pequenas e aumentar a complexidade da fiação.

O uso da interface SWD para download e depuração requer apenas 4 pinos: GND, RST, SWDIO, SWDCLK. A velocidade de download pode chegar a 10 M/s, oferecendo vantagens claras.

Modo SWD:

O modo SWD é mais confiável do que o JTAG em cenários de alta velocidade. Em situações com grandes quantidades de dados, o download do programa JTAG pode falhar com mais frequência em comparação com o SWD, que tem uma taxa de falha menor. Geralmente, se o seu emulador suporta o modo de simulação JTAG, você pode usar diretamente o modo SWD, desde que ele o suporte.

Design de PCB

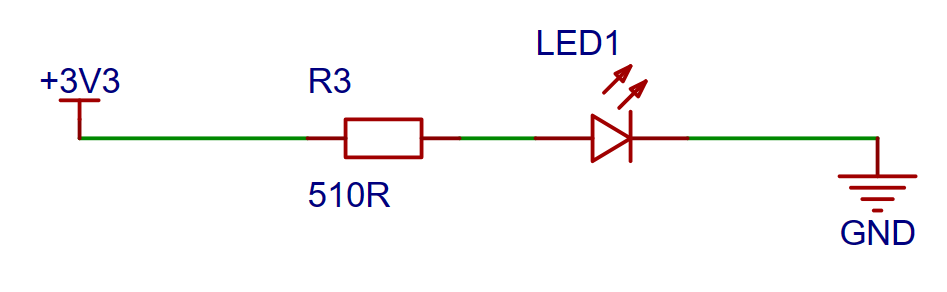

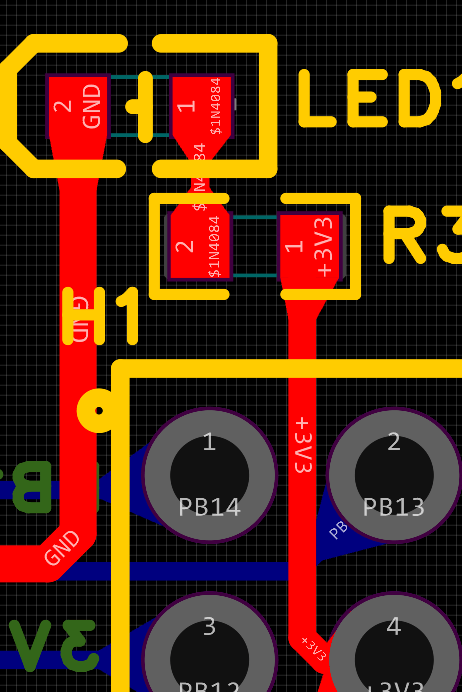

Circuito indicador de energia

Diagrama esquemático

De acordo com a ficha técnica, a queda de tensão direta máxima é de 2,4 V, com um valor típico de 2,1 V. Portanto, quando o LED está funcionando normalmente, a queda de tensão máxima no LED é de 2,4 V. Nesse caso, a divisão de tensão em R3 é de 0,9 V.

Normalmente, os LEDs acendem normalmente em correntes que variam de 3 mA a 10 mA. A corrente nominal máxima é de 20 mA. Dentro da corrente nominal, quanto maior a corrente que flui através do LED, mais brilhante ele fica.

Aqui, escolhemos I = 10 mA, portanto, R3 = U / I = 0,9 V / 10 mA = 90 Ω. Como os resistores de 100 Ω são mais comuns em nossos materiais, podemos usar um resistor de 100 Ω.

Design de PCB

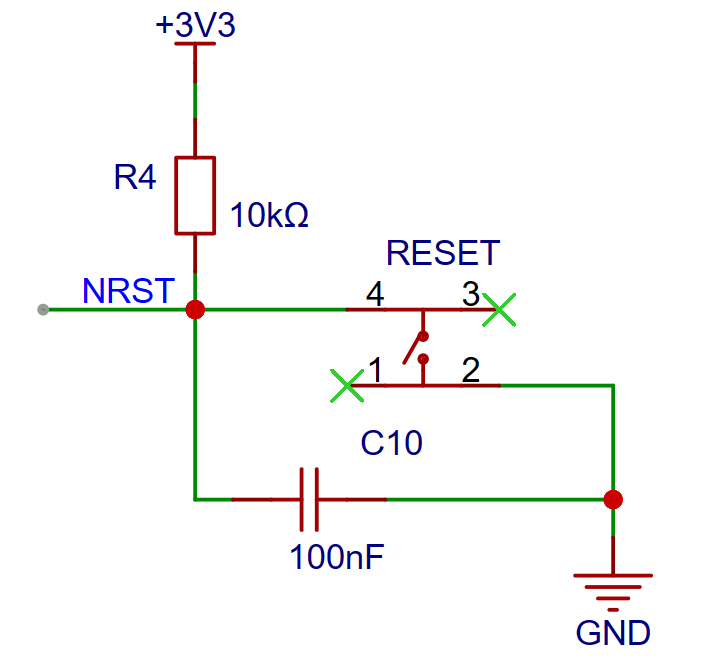

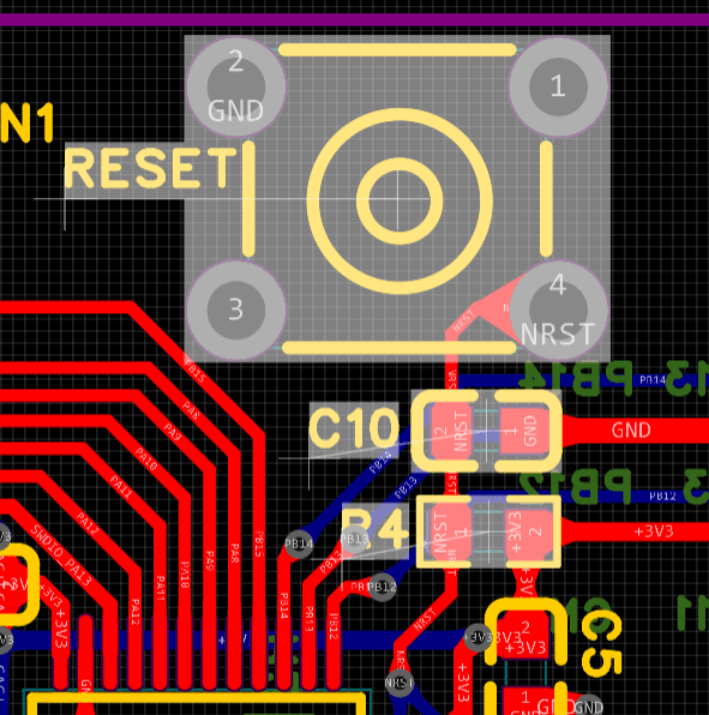

Projeto do circuito de reinicialização

Diagrama esquemático

Quando o pino NRST é puxado para baixo, um sinal de reinicialização é gerado, permitindo-nos realizar uma operação de reinicialização em nosso microcontrolador.

No diagrama do circuito:

– Quando o microcontrolador é ligado novamente, o capacitor C14 carrega e conduz. A tensão RESET é baixa, causando uma reinicialização do sistema. Após um certo período, quando o capacitor C9 termina de carregar e se desconecta, a tensão RESET fica alta e o microcontrolador permanece estável sem reinicializar.

– Quando o botão é pressionado, ele permanece condutor por 20 a 50 ms, conectando o nRST ao terra, resultando em uma tensão baixa e uma reinicialização do sistema.

Design de PCB

Projeto do circuito BOOT

Diagrama esquemático

BOOT0 e BOOT1 do STM32 controlam o modo de inicialização do chip, suportando inicialização FLASH interna, inicialização da memória do sistema e inicialização SRAM interna. Especificamente:

- Flash do usuário: Flash integrado ao chip.

- SRAM: Área RAM integrada no chip.

- Memória do sistema: uma área específica dentro do chip onde um bootloader é pré-carregado durante a fabricação. Isso é frequentemente chamado de programa ISP.

- Os programas ISP geralmente se comunicam via USART1.

Ao depurar e baixar programas usando JTAG ou SWD, o programa geralmente é baixado para o Flash. Nesse caso, você pode definir os pinos BOOT0 e BOOT1 como baixos.

Um resistor de 10K é usado porque BOOT0 e BOOT1 estão em um estado de alta impedância sem dispositivos externos. Os resistores pull-up e pull-down de 10K servem como bons limitadores de corrente e também protegem o chip IC interno.

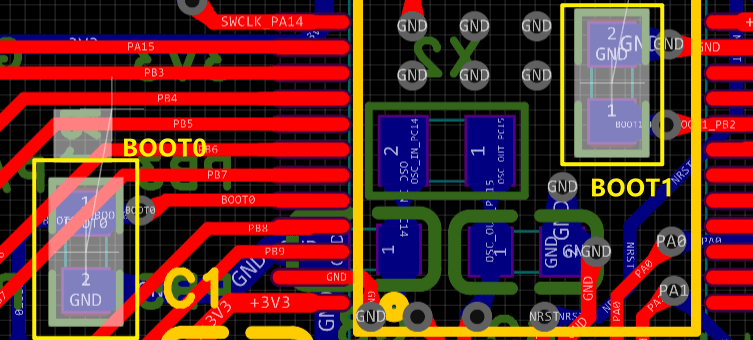

Design de PCB

Aqui, colocamos os resistores pull-down para BOOT0 e BOOT1 na parte traseira da placa de circuito impresso para evitar interferência com nossos traços.

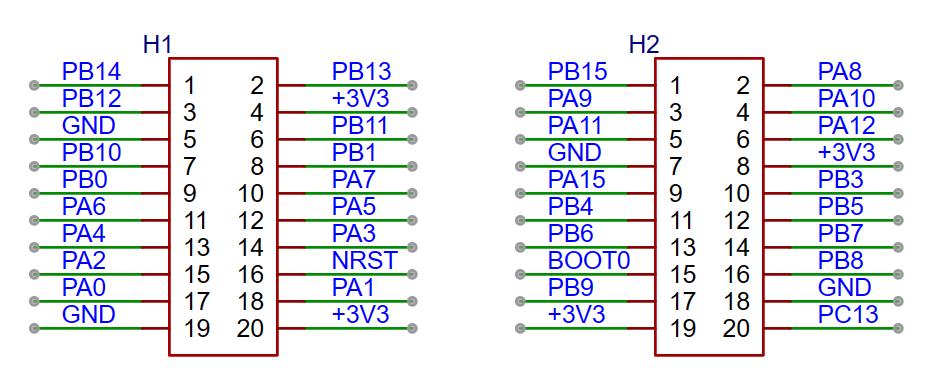

Circuito da porta IO periférica

Diagrama esquemático

Os pinos não utilizados são normalmente conduzidos através de conectores de pinos. Recomenda-se a utilização de conectores de pinos de duas filas para aumentar a estabilidade e minimizar a flexão durante a inserção ou remoção, evitando conectores de pinos de uma única fila.

Além disso, é aconselhável conduzir o BOOT0. Isso facilita o projeto posterior de um circuito de download ISP de um botão, permitindo o download do programa com um único cabo USB.

Por último, recomenda-se conduzir pelo menos dois conjuntos de pinos +3V3 e GND, para que cada lado do conector de pinos tenha uma fonte de alimentação, facilitando a fiação da placa de circuito impresso.

Design de PCB