Na era dos servidores com IA, dos smartphones 5G e dos veículos autónomos, o desempenho de um chip depende inteiramente do «sistema nervoso» que o suporta: o substrato do circuito integrado. À medida que a densidade dos circuitos atinge os seus limites físicos, a escolha do processo de fabrico determina a integridade do sinal e a fiabilidade do produto final.

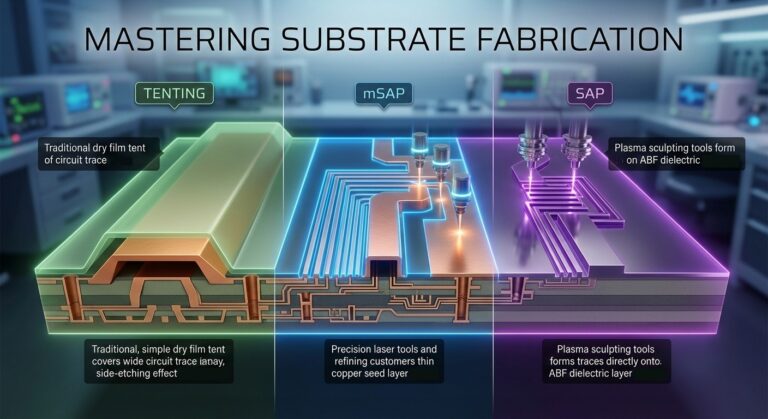

Atualmente, três «ferramentas de modelagem» principais dominam a indústria: Tenting (Subtrativo), mSAP (Processo Semi-Aditivo Modificado) e SAP (Processo Semi-Aditivo). Este guia detalha os seus mecanismos técnicos, vantagens e desvantagens, e onde se encaixam no ecossistema eletrónico moderno.

1. Processo de ententagem (método subtrativo)

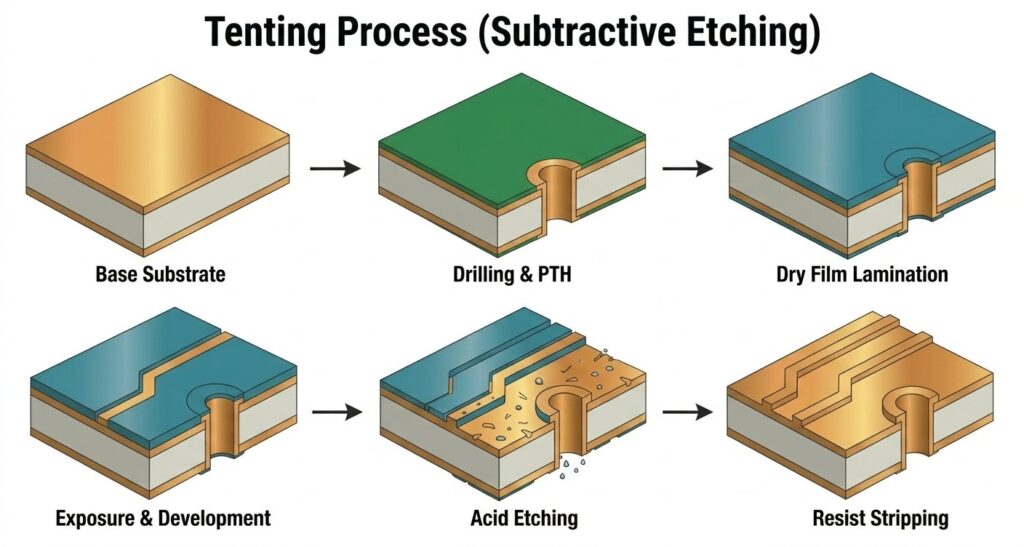

O processo de Tenting é a tecnologia de formação de linhas mais tradicional e amplamente utilizada na indústria de placas de circuito impresso (PCB) e de substratos de baixa densidade. A sua filosofia central é «cobrir e remover» — muito semelhante a esculpir um selo a partir de um bloco de pedra.

Como funciona: Começa com um laminado revestido de cobre (CCL) com uma folha de cobre espessa (normalmente > 12 µm). Uma película seca (fotorresistência) cobre as áreas do circuito pretendidas como uma «tenda» sobre os orifícios (daí o nome). O cobre desprotegido é então removido por corrosão química.

O problema (gravação lateral): Como a gravação remove o cobre vertical e horizontalmente em simultâneo, cria uma secção transversal «trapezoidal». Esta «gravação lateral» limita a precisão da largura da linha e do espaço ($L/S$) a cerca de $30\mu m/30\mu m$.

Ideal para: Eletrónica de consumo padrão, PCBs automotivas e substratos tradicionais de BGA com ligação por fio (WB BGA).

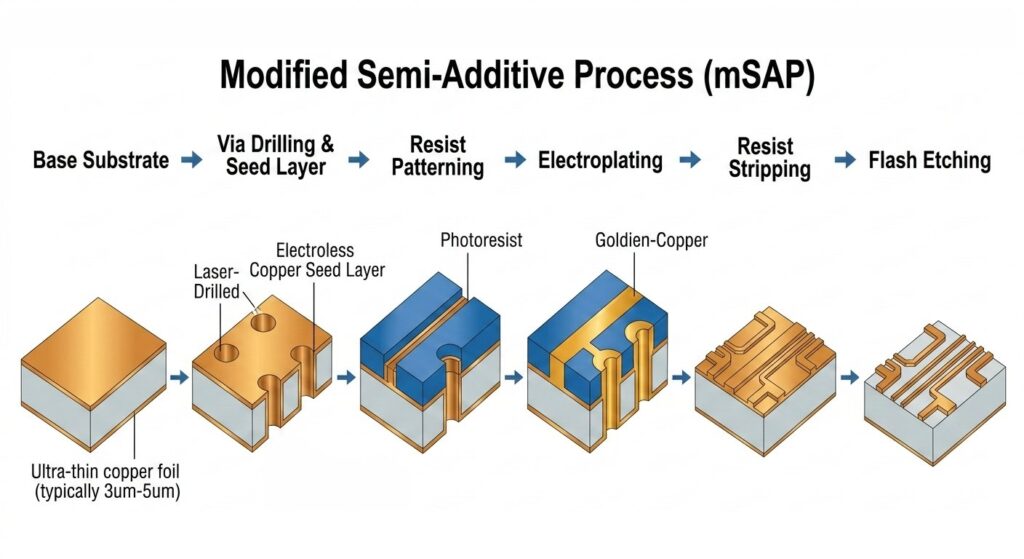

2. mSAP (Processo Semi-Aditivo Modificado)

À medida que o número de pinos aumentava e os sinais ganhavam velocidade, o mSAP surgiu como a ponte entre as placas de circuito impresso (PCB) tradicionais e os substratos de circuitos integrados (IC) de alta tecnologia. Atualmente, é a escolha predominante para substratos FCBGA utilizados em chips de rede e processadores de smartphones de gama alta.

Como funciona: Em vez de cobre espesso, o mSAP começa com uma base de cobre ultrafina (normalmente 3 a 5 µm) ou uma «camada de semente» depositada quimicamente. A circuitaria é «adicionada» através de galvanoplastia seletiva até à espessura desejada.

A vantagem: Após a galvanização, uma rápida «gravação instantânea» remove a camada de base ultrafina. Como a base é tão fina, o tempo de gravação é mínimo, resultando em paredes de circuito retangulares quase verticais com capacidades $L/S$ até $10\mu m/10\mu m$.

Ideal para: Processadores de smartphones topo de gama (série A da Apple, Snapdragon), embalagens à escala do chip (FCCSP) e PCBs tipo substrato (SLP).

3. SAP (Processo Semi-Aditivo)

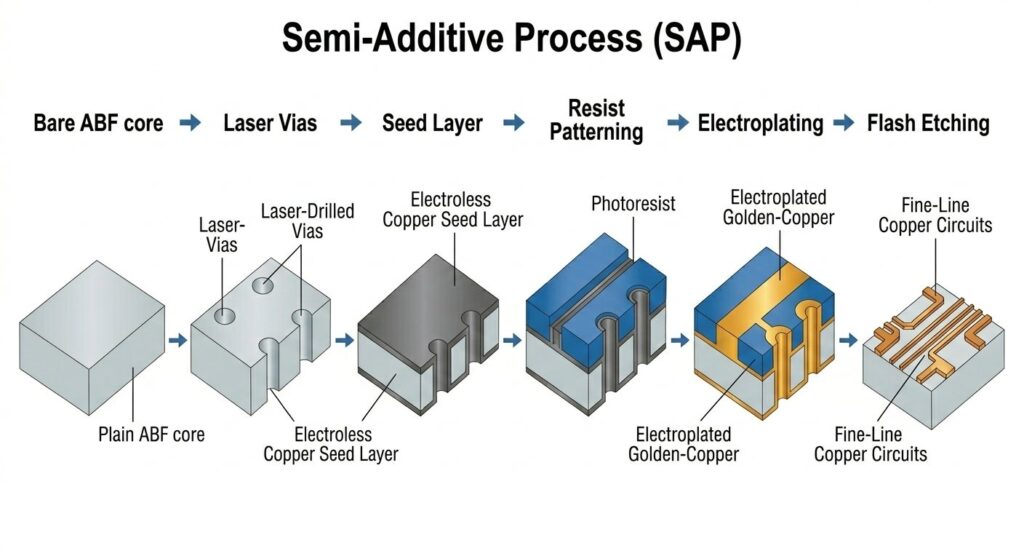

O SAP representa o auge da precisão dos circuitos, sendo frequentemente referido como uma versão «purificada» do mSAP. Abandona totalmente a folha de cobre em favor da «adição pura».

Como funciona: Utiliza um material dielétrico isento de cobre, nomeadamente o ABF (Ajinomoto Build-up Film). Uma «camada semente» microscópica ($< 1\mu m$) é depositada quimicamente sobre a superfície lisa, seguida de galvanização seletiva para construir os circuitos.

A vantagem: Uma vez que a camada de semente é praticamente inexistente, a gravação tem impacto nulo na morfologia do circuito. Isto permite uma precisão extrema ($L/S < 10\mu m$) e um controlo de impedância superior para sinais de alta velocidade.

Ideal para: Computação de alto desempenho (HPC), aceleradores de IA (Nvidia H100) e embalagens avançadas como CoWoS e HBM.

4. Tabela comparativa: Tenting vs. mSAP vs. SAP

| Feature | Tenting | mSAP | SAP |

|---|---|---|---|

| Core Principle | Subtractive: Etch away thick copper foil | Additive: Plate over ultra-thin copper base | Pure Additive: Seed layer on copper-free dielectric |

| Line Precision (L/S) | > 30μm | 10μm - 30μm | < 10μm |

| Cross-section Shape | Trapezoidal (Side-etching) | Near-Rectangular | Perfectly Rectangular |

| Base Material | Standard CCL | Ultra-thin copper foil | ABF (Ajinomoto Build-up Film) |

| Primary Application | Consumer PCBs / Motherboards | Smartphone AP / High-end HDI | AI Accelerators / CPU / GPU Substrates |

| Cost & Maturity | Low Cost / Highly Mature | Medium-High / Mainstream High-end | Very High / Cutting-edge |

Perspetivas para o futuro: o futuro da fabricação

A indústria está a avançar para uma abordagem «híbrida» com o objetivo de equilibrar custos e desempenho — utilizando a técnica de «tenting» para as camadas centrais e mSAP/SAP para as camadas externas de alta densidade. À medida que a procura de IA desafia os limites da Lei de Moore, tecnologias emergentes como os substratos de vidro e os chips incorporados continuarão a evoluir a par destes três processos fundamentais.

Compreender as nuances destes métodos de fabrico é o primeiro passo para dominar o panorama complexo da embalagem moderna de chips e da segurança de hardware.