Il test IC serve a rilevare se il chip presenta difetti di progettazione o fisici causati dal processo di fabbricazione. Il processo può essere condotto utilizzando vari metodi di prova.

Il confezionamento IC è il processo di racchiusura di un circuito integrato (IC) in un involucro protettivo. Questo processo protegge l’IC da danni e ne garantisce il corretto funzionamento. Consente inoltre la connessione dell’IC ad altri dispositivi e circuiti.

come testare un IC utilizzando un tester IC?

kit di test IC

Sono disponibili sul mercato diversi tipi di kit di test IC, ciascuno progettato per uno scopo specifico. Ad esempio, alcuni kit di test IC sono progettati per test generici. Mentre altri sono progettati per applicazioni specifiche come IC automobilistici o IC di potenza.

La maggior parte dei kit di test IC include una varietà di accessori di base, come un multimetro, sonde, tester IC digitale e cavi di prova. Alcuni kit possono includere anche apparecchiature più specializzate, come un oscilloscopio o un analizzatore logico.

Metodo di prova

Ci sono diversi modi per testare gli IC, ma il metodo più comune è chiamato test in circuito (ICT). Questo tipo di test viene eseguito collegando un dispositivo di test al dispositivo in prova (DUT). Quindi eseguiamo una serie di test per verificare le funzionalità di base.

L’ICT può essere utilizzato per testare sia IC digitali che analogici. Per gli IC digitali, il tester invierà una serie di segnali di ingresso al DUT. E quindi controlla le uscite per vedere se corrispondono ai risultati previsti. Gli IC analogici vengono in genere testati utilizzando una tecnica chiamata test dinamico. Durante questo processo, il tester applica una serie di segnali al DUT e quindi misura la risposta.

Ci sono diverse aziende che producono tester ICT, è necessario sceglierne uno compatibile con i propri IC specifici. Una volta che si ha un tester, è necessario creare un dispositivo di test che si connetta al DUT. Il dispositivo di test può applicare i segnali necessari al DUT e anche misurare la risposta.

Una volta che si hanno entrambi, è necessario scrivere un programma di test per controllare i risultati. Questo può essere un processo lungo, ma è importante garantire che i propri IC funzionino correttamente.

Tipi di test

test di continuità IC

Il test di continuità IC è semplice, che puoi utilizzare per determinare se gli IC funzionano correttamente o meno.

Questo test viene eseguito collegando un multimetro all’IC e misurando la resistenza tra i vari pin.

Se l’IC funziona correttamente, la resistenza dovrebbe essere bassa (di solito inferiore a 10 ohm). Altrimenti, la resistenza sarà alta (di solito superiore a 10 ohm).

test di livello

Il test di livello IC è un tipo di test elettrico per determinare la funzione e le prestazioni dei circuiti integrati (IC).

Questo test viene in genere eseguito su IC già installati su una scheda di circuito.

Lo scopo del test è verificare che l’IC funzioni correttamente e soddisfi le specifiche per l’uso previsto.

Esistono una varietà di diversi metodi di test per il test di livello IC, tra cui test logici, test funzionali e test parametrici.

Percorso di sviluppo del confezionamento IC

L’imballaggio ha attraversato approssimativamente il seguente processo di sviluppo:

1. In termini di struttura:

TO→DIP→PLCC→QFP→BGA→CSP→WLP e SiP, ecc.

2. Materiali:

Metallo, ceramica → ceramica, plastica → plastica;

3. Forma del pin:

Lungo lead in-line → montaggio a lead corto o senza lead → bump a sfera

4. Metodo di assemblaggio:

Through Hole Insertion → Surface Mounting → Direct Mounting

5. La forza trainante del continuo miglioramento dell’imballaggio:

Dimensioni più piccole, più tipi di chip, più I/O

6. Difficoltà:

Il processo sta diventando sempre più complesso, ed è necessario tenere conto della dissipazione del calore e della conducibilità elettrica riducendo il volume.

Caratteristiche e competitività di base

1. Forti attributi manifatturieri

La capacità produttiva dipende completamente dall’acquisto di attrezzature (investimenti di capitale) e, come nella produzione tradizionale, attraverserà anche il processo di aumento della capacità e ottimizzazione del processo. Con la scala arriva l’accumulo di esperienza e i vantaggi della tecnologia leader.

2. La scala dell'imballaggio e dei test determina la struttura del cliente

I grandi produttori di progetti collaboreranno solo con i produttori di test con una certa scala. Se la scala non aumenta, è difficile intraprendere grandi ordini ed è difficile ottimizzare la struttura del cliente. Pertanto, le aziende con tecnologia leader e scala entreranno in un circolo virtuoso: tecnologia leader ➔ sviluppo del cliente ➔ espansione del finanziamento ➔ aumento della capacità produttiva ➔ ottimizzazione del processo ➔ tecnologia leader e amplieranno gradualmente il divario con i concorrenti.

3. Competitività di base

Le due caratteristiche del settore di cui sopra determinano la competitività di base delle aziende di test professionali per circuiti integrati:

Capacità di R&S: concentrarsi sullo sviluppo di procedure di test e soluzioni di test.

Grado di commercializzazione: le capacità di sviluppo del programma di test e ottimizzazione del processo derivano dall’esperienza di test di diversi tipi di chip portata da un gran numero di clienti.

Processo di test perfetto: attraverso la stretta integrazione della progettazione a monte e della lavorazione delle wafer, il processo e il processo di test vengono continuamente ottimizzati.

Capacità di gestione del capitale: l’attuale fase di sviluppo nazionale determina che la scala è il presupposto dello sviluppo. Pertanto, la capacità di finanziamento che corrisponde alla tecnologia e alla forza del mercato è il supporto per lo sviluppo e la crescita dell’impresa.

mercato dell'imballaggio e dei test IC

1. Scala dell'imballaggio e dei test IC

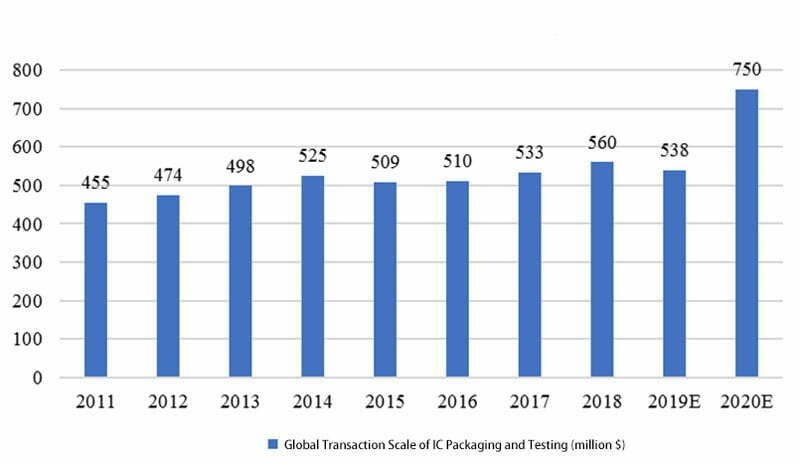

1.1 Transazione globale di imballaggio e test IC (2011-2020)

Nel 2019, l’industria dei semiconduttori nel suo complesso ha rallentato e ha mostrato una crescita negativa, così come il mercato dell’imballaggio e dei test dei chip. Tuttavia, il mercato successivo si è ripreso grazie alla domanda di 5G, AI, IoT, cloud computing e big data. Gli esperti hanno previsto che il mercato complessivo dell’imballaggio e dei test dei chip nel 2024 potrà raggiungere i 75 miliardi di dollari.

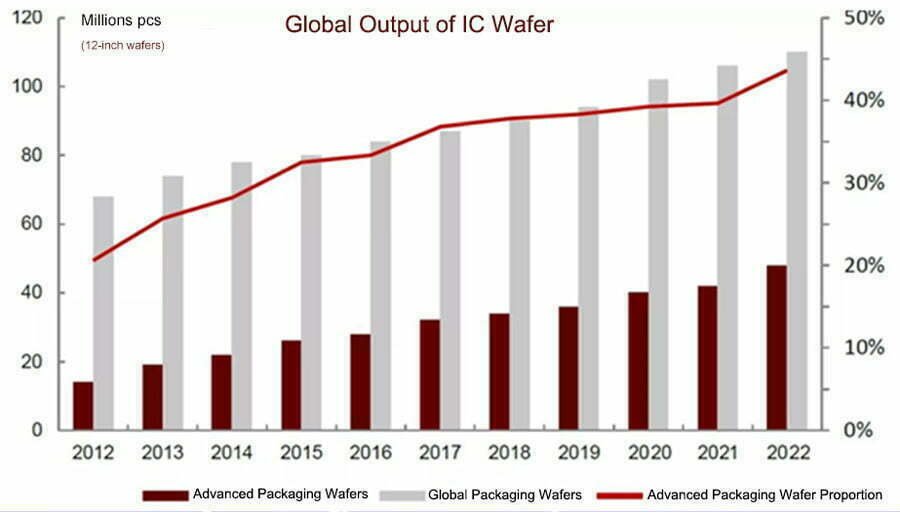

1.2 Produzione globale di wafer IC (2012-2022)

Con l’accelerazione di campi emergenti come 5G, IoT e AI, le dimensioni dei chip richieste diventano sempre più piccole. Allo stesso tempo, ci sono sempre più tipi di chip. Il numero di pin I/O è aumentato anche in modo significativo e la domanda di imballaggi avanzati è gradualmente aumentata.

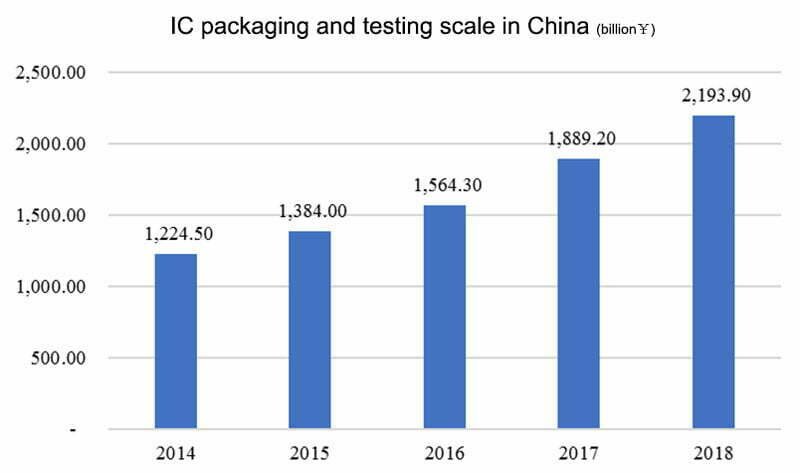

1.3 Scala dell'imballaggio e dei test iC in Cina (2014-2018)

Nel 2018, la capacità di assemblaggio e test IC nella Cina continentale ha raggiunto i 217,44 miliardi di unità e le dimensioni del mercato dell’industria dell’assemblaggio e del test IC hanno raggiunto i 219,39 miliardi di yuan, con un aumento anno su anno del 16,1%.

2. La crescita della scala di imballaggio avanzato

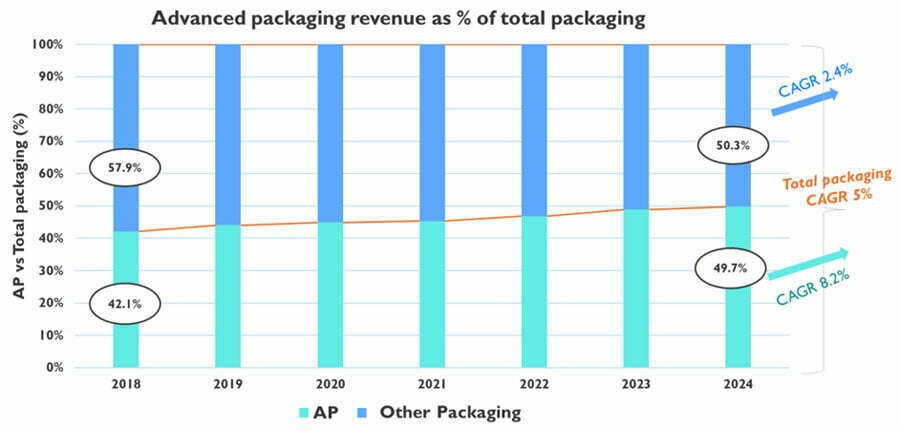

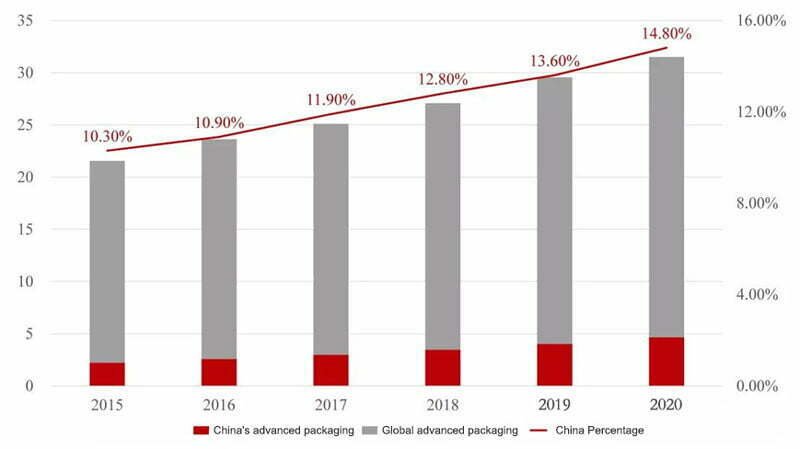

2.1 Proporzione di imballaggio IC avanzato sul totale

Secondo le statistiche di Yole, sebbene l’industria dei semiconduttori nel suo complesso abbia rallentato e abbia subito una crescita negativa nel 2019, le dimensioni del mercato dell’imballaggio avanzato manterranno una tendenza alla crescita. Nel 2018, le dimensioni del mercato dell’imballaggio avanzato erano di 27,6 miliardi di dollari USA.

In crescita a un tasso di crescita annuale composto dell’8%, raggiungendo circa 44 miliardi di dollari entro il 2024. Il mercato dell’imballaggio tradizionale crescerà a un tasso di crescita annuale composto del 2,4%, mentre il CAGR dell’intera industria dell’imballaggio IC raggiungerà il 5%.

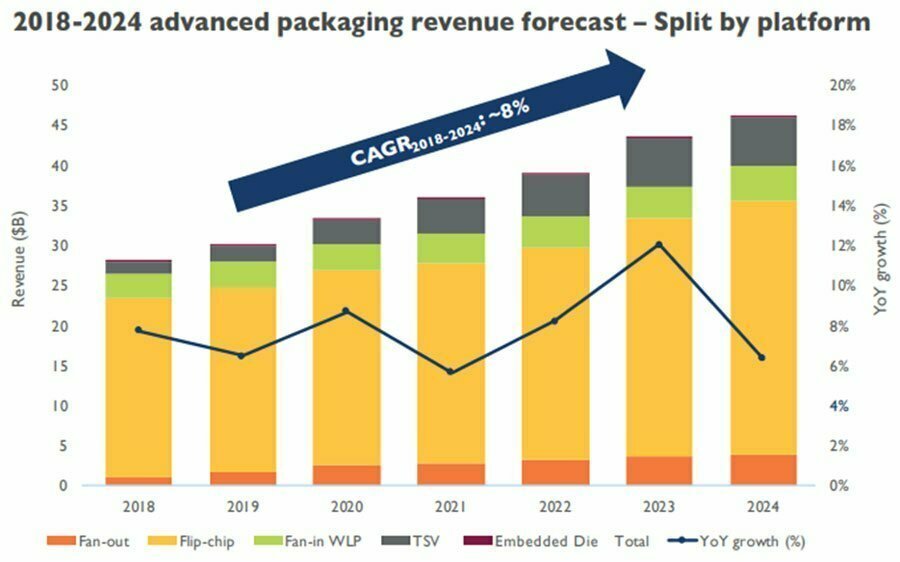

2.2 Tendenze delle previsioni dei ricavi per l'imballaggio avanzato (2018-2024)

Nel settore dell’imballaggio avanzato, la tecnologia flip-chip rappresenta la proporzione più alta. Nel 2018, i ricavi dell’imballaggio e del test flip-chip hanno rappresentato circa l’81% del mercato dell’imballaggio avanzato. Entro il 2024, a causa del rapido sviluppo di altre tecnologie, diminuirà al 72%.

Dal 2018 al 2024, TVS, ED e fan-out sono le tecnologie a più rapida crescita. Si prevede che il tasso di crescita dei ricavi per l’imballaggio 2.5D/3D (TSV), ED e fan-out (Fan-out) sarà rispettivamente del 26%, 49%, 26%.

Il CAGR di Fan-in WLP 2018-2024 è relativamente basso, solo il 6,5%, e le dimensioni del mercato dei die embedded nel 2018 sono inferiori a 25 milioni di dollari USA.

Tuttavia, il CAGR sarà elevato quanto il 49% nei prossimi cinque anni e i principali fattori trainanti deriveranno dalla domanda di strutture di comunicazione, elettronica automobilistica e mercati mobili.

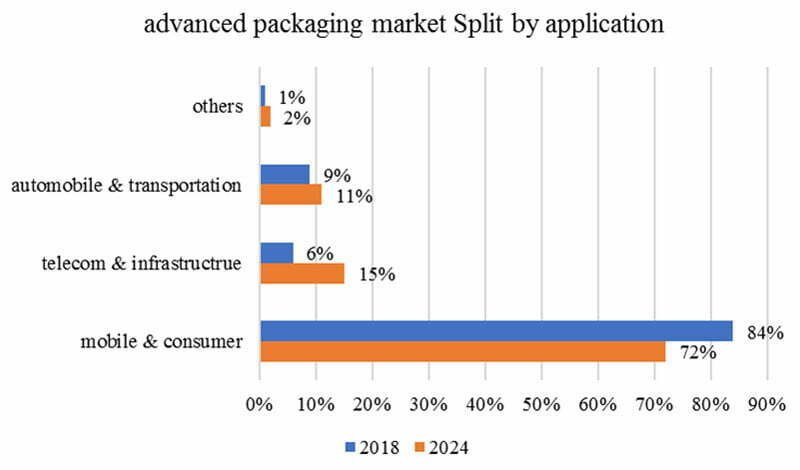

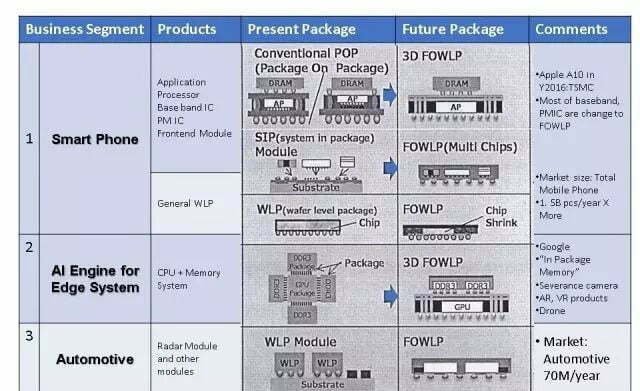

2.3 applicazioni di imballaggio avanzato

Per campo di applicazione, nel 2018, le applicazioni mobili e consumer hanno rappresentato l’84% del mercato totale dell’imballaggio avanzato. Dal 2019 al 2024, il CAGR di questo segmento del mercato applicativo è stato del 5% e nel 2024 ha rappresentato il 72% del mercato totale dell’imballaggio avanzato.

Il segmento delle telecomunicazioni e delle infrastrutture è il segmento in più rapida crescita del mercato dell’imballaggio avanzato (circa il 28%) e la sua quota di mercato crescerà dal 6% nel 2018 al 15% nel 2024.

Allo stesso tempo, la quota di mercato del segmento automobilistico e dei trasporti è cresciuta dal 9% nel 2018 all’11% nel 2024.

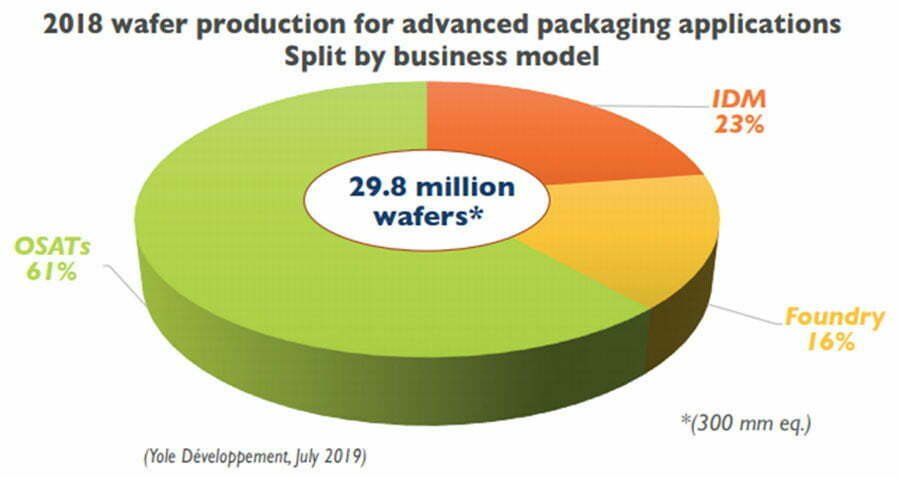

Nel 2018, le fonderie professionali di assemblaggio e test di chip hanno rappresentato il 61% del mercato dell’assemblaggio e del test avanzato, mentre le società di tipo IDM hanno rappresentato il 23% e i produttori di tipo foundry hanno rappresentato il 16%.

Panorama competitivo

1. Le 10 aziende globali (2018-2019)

Il mercato dell’assemblaggio e del test di chip è relativamente concentrato. I primi dieci produttori controllano circa l’80% del mercato. I produttori della Cina continentale e di Taiwan dominano il mercato. Per molti anni, l’industria taiwanese dell’assemblaggio e del test ha catturato quasi la metà delle entrate operative globali, affermandosi saldamente tra i primi dieci.

Indipendentemente dai ricavi dell’assemblaggio e del test di chip di IDM (come Intel e Samsung), ASE e Amkor sono saldamente ai primi due posti nell’assemblaggio e nel test di chip professionali.

2. Opportunità e sfide

I cambiamenti nella catena di approvvigionamento dei semiconduttori, i cambiamenti nei modelli di business e l’incertezza nelle relazioni commerciali tra Stati Uniti e Cina hanno creato opportunità per alcuni produttori e minacce per altri.

2.1 Estensione della catena industriale

In questo ambiente aziendale in continua evoluzione, la catena di approvvigionamento dei semiconduttori sta cambiando a ogni livello. Alcuni fornitori hanno esteso con successo nuovi modelli di business.

Hanno influenzato significativamente la catena di produzione di circuiti integrati, mentre altri produttori non sono riusciti a sfruttare lo slancio. Diversi fornitori hanno diversi fattori che li spingono a espandersi in nuove attività.

Ad esempio, società di software come Google, Microsoft, Facebook e Alibaba stanno progettando i propri processori per ottenere integrazione/personalizzazione a livello di sistema e controllo della catena di approvvigionamento a livello di assemblaggio.

Il cambiamento più grande si riscontra nelle fonderie che iniziano a espandersi nel settore del packaging avanzato. Anche se sono relativamente “nuovi arrivati”, il loro impatto è enorme.

2.2 Innovazione nella tecnologia di packaging

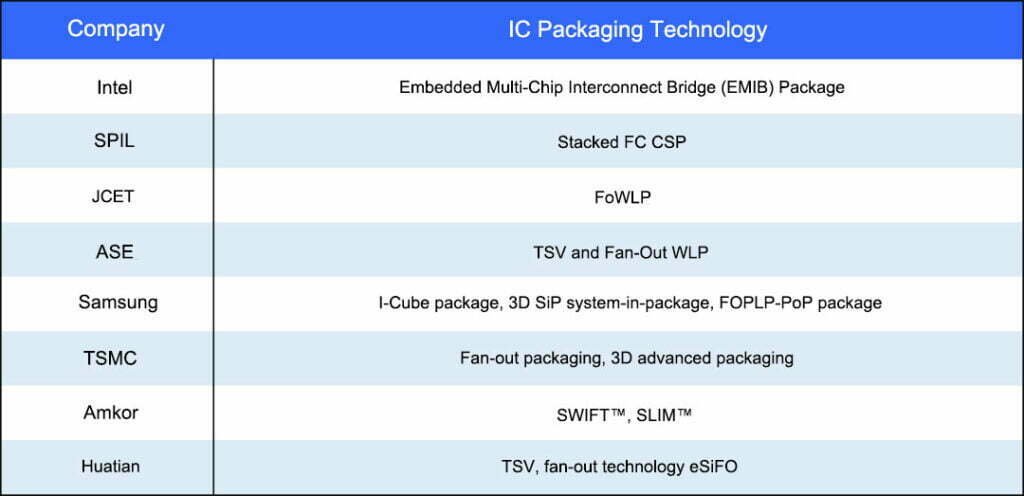

TSMC guida l’innovazione nel packaging fan-out e nelle piattaforme di packaging avanzato 3D. Offre una varietà di prodotti come InFO (e le sue varianti), CoWoS, WoW, 3D SoIC e altro ancora.

Il packaging avanzato è diventato un’attività consolidata per TSMC. Si prevede che genererà 3 miliardi di dollari di entrate nel 2019, il che la collocherebbe al quarto posto nella classifica OSAT.

UMC è un importante fornitore di interposer in silicio per il packaging 2.5D. Recentemente ha stretto una partnership con Xperi per ottimizzare e commercializzare le tecnologie ZiBond e DBI per vari dispositivi a semiconduttore.

Nel frattempo, Wuhan Xinxin (XMC) fornisce pacchetti 3D IC TSV per sensori di immagine e applicazioni ad alte prestazioni. Collettivamente, questi attori hanno svolto un ruolo importante nel passaggio del packaging da substrati a piattaforme in silicio.

2.3 Il packaging a livello di sistema tende a essere popolare

È una tendenza che i partecipanti all’industria del packaging SiP estendano a monte e a valle. Nella tradizionale catena industriale del packaging SiP, le aziende rappresentative del packaging e del test di circuiti integrati includono Changdian Technology e ASE, che forniscono principalmente prodotti di packaging e test standard a livello funzionale. L’azienda rappresentativa del packaging a livello di sistema è USI, che si occupa principalmente di packaging di sistemi a livello di modulo. Queste due aziende appartengono alla relazione a monte e a valle e i processi e le attrezzature coinvolte sono diversi.

2.4 Chip incorporati

D’altra parte, i produttori di substrati IC e PCB come Samsung Electro-Mechanics (SEMCO), Unimicron, AT&S e Shinko Electric (Shinko) stanno sfruttando i chip incorporati (e i componenti passivi) nei pacchetti fan-out a livello di pannello e nei substrati organici. componenti) nello spazio del packaging avanzato e stanno erodendo la quota di mercato di OSAT (soprattutto nel business che coinvolge il packaging avanzato).

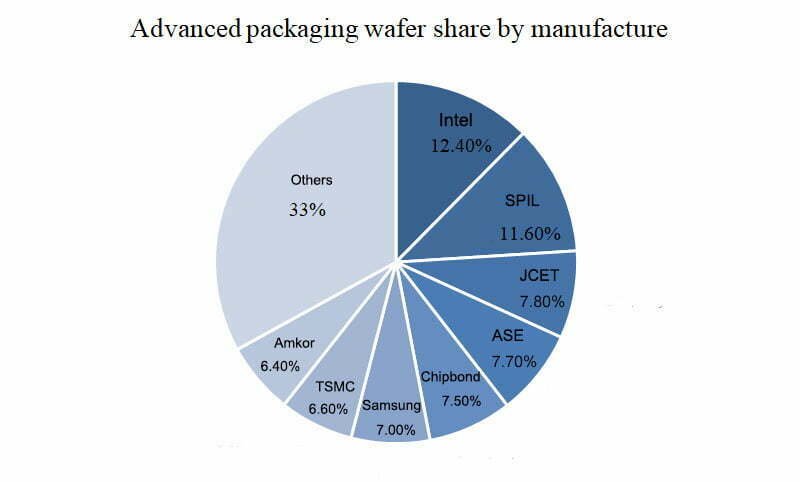

3. Quota di mercato dei wafer di packaging avanzato

Rispetto alla concentrazione complessiva del mercato del packaging e del test, la concentrazione del mercato del packaging e del test avanzato è relativamente bassa. Nel 2017, i primi 8 produttori rappresentavano il 67% della quota di mercato del packaging avanzato.

I fornitori nel mercato del packaging avanzato hanno diverse aree di competenza:

Situazione dell'industria del packaging IC cinese

L’industria del packaging IC cinese è iniziata molto presto e si è sviluppata rapidamente, basandosi principalmente su prodotti di packaging tradizionali. Negli ultimi anni, i produttori nazionali hanno superato fusioni e acquisizioni. Attualmente, la piattaforma tecnologica cinese si è fondamentalmente sincronizzata con i produttori esteri. Inoltre, le tecnologie di packaging avanzato come BGA, TVS, WLCSP e SiP sono state prodotte in serie.

Tuttavia, esiste ancora un certo divario tra le entrate complessive del packaging avanzato a Taiwan e negli Stati Uniti. Secondo le statistiche di TrendForce, le entrate del packaging avanzato cinese nel 2018 ammontavano a circa 52,6 miliardi di yuan. Rappresentavano il 25% delle entrate totali nazionali del packaging e dei test, inferiori al rapporto globale del 41%. Quindi c’è ancora molto spazio per la crescita in futuro.

Mercato cinese del packaging avanzato di IC

Inoltre, esiste anche un grande divario tra le aziende di packaging cinesi e i principali produttori internazionali. In particolare, il divario è evidente nella tecnologia di packaging di circuiti integrati ad alta densità, come la tecnologia di packaging di chip HPC. La tecnologia di stacking 3D multi-chip proposta da TSMC. Adotta una struttura di bonding non-bump, che può migliorare notevolmente la velocità di calcolo complessiva di CPU/GPU e memoria. Anche Intel ha proposto un concetto di packaging 3D simile, impilando la memoria su chip CPU e GPU.

Il valore della produzione globale del mercato cinese del packaging avanzato è relativamente basso, ma sta crescendo rapidamente e la sua proporzione si sta espandendo. I dati di Yole mostrano. Nel 2017, il valore della produzione del packaging avanzato cinese era di 2,9 miliardi di dollari USA, rappresentando l’11,9% del mondo, e raggiungerà i 4,6 miliardi di dollari USA entro il 2020, rappresentando il 14,8% del mondo. Secondo i dati, le aziende cinesi di packaging e test hanno accelerato l’aumento della capacità produttiva nel campo del packaging avanzato nel 2018, con un tasso di crescita del 16%, il doppio del tasso globale.

forza trainante del mercato

Ci sono due percorsi di sviluppo per il packaging avanzato:

Uno è ridurre le dimensioni per renderlo vicino alle dimensioni del chip. Un indicatore importante è il rapporto tra l’area del chip e l’area del package. Più questo rapporto è vicino a 1, meglio è, inclusi WLCSP, FC, Bumping, Fanout, ecc.

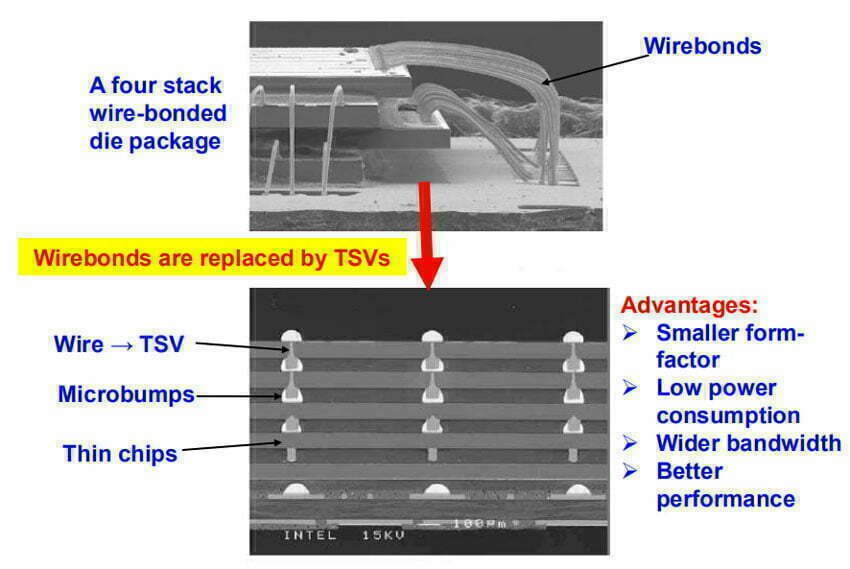

Il secondo è lo sviluppo funzionale, che enfatizza l’integrazione eterogenea e fornisce funzionalità multiple nella miniaturizzazione del sistema, inclusi TSV, SIP e così via.

1. Tecnologia SIP

Il processo di fabbricazione dei semiconduttori globali si sta avvicinando al limite fisico dei diodi. Il processo più avanzato è 7nm. A causa degli enormi investimenti, diventa sempre più costoso migliorare ulteriormente le prestazioni del chip dal lato della produzione. Partendo dal packaging del chip, la tecnologia system-in-package SIP combina chip con funzioni diverse come chip logici e memoria.

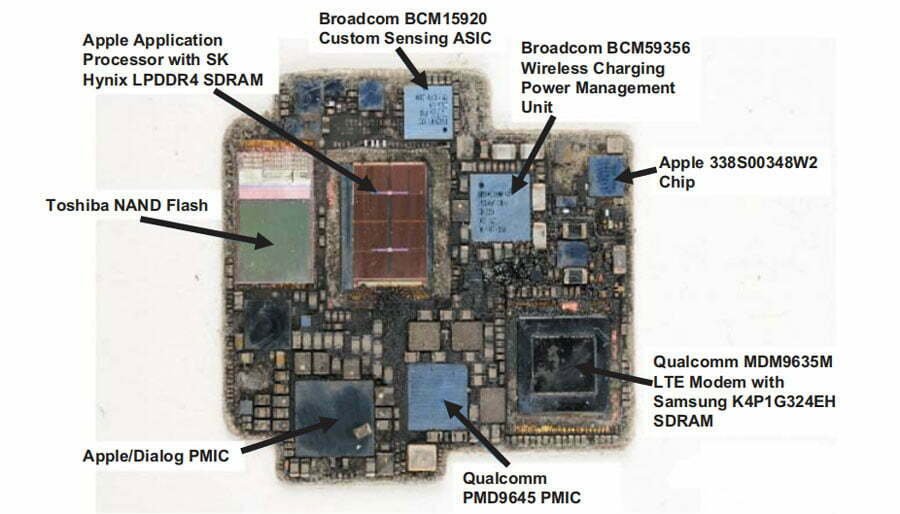

I componenti passivi IPD, RF RF e sensori e altri chip sono confezionati in un unico modulo, il che può ridurre le dimensioni del chip, migliorare le prestazioni del chip e ridurre il consumo di energia. L’Internet delle cose (IoT) è uno scenario applicativo importante che promuove lo sviluppo della tecnologia di packaging SIP, e i dispositivi indossabili sono un campo con un grande potenziale applicativo per la tecnologia system-in-package in futuro. Il sensore di riconoscimento delle impronte digitali, il sensore di riconoscimento facciale 3D, la rete wireless WiFi e altri moduli funzionali in Apple Watch sono confezionati insieme, che è l’uso della tecnologia del modulo system-in-package (SiP) di ASE.

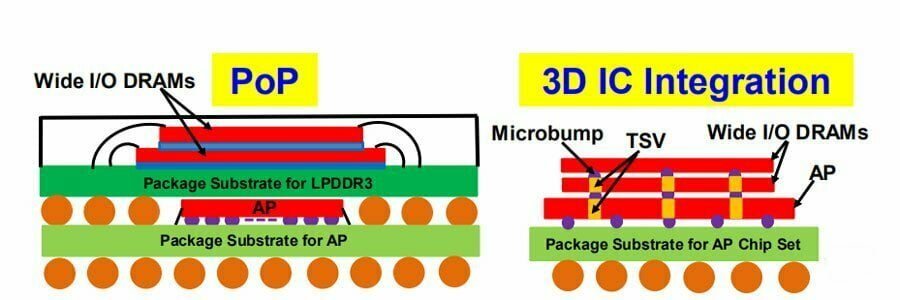

La tecnologia SIP integra con successo circuiti integrati, dispositivi discreti, dispositivi ottici, memorie, condensatori ceramici multistrato e resistori di chip in substrati sottili, sottili e corti senza che le loro informazioni interferiscano l’una con l’altra. Riteniamo che Apple sia almeno in vantaggio di uno o due anni nell’applicazione del packaging del sistema rispetto ai concorrenti. A seconda dei requisiti applicativi e della complessità del prodotto, i tipi di system-in-package SiP possono essere suddivisi in moduli 2D contenenti più componenti attivi e passivi e moduli 3D più complessi. Ad esempio, PiP (Package-in-Package) nel sistema, PoP (Package-on-Package) e tecnologia di packaging 2.5D/3D sul sistema.

2. Tecnologia TSV

In qualità di rappresentante della tecnologia di packaging 3D, la tecnologia TSV avrà applicazioni più ampie nel campo del packaging di memorie flash 3DNAND e nel packaging di memorie DRAM in futuro. La memoria è diventata la sottosezione con il maggior potenziale di crescita nel settore nazionale dei semiconduttori. I due principali progetti di memoria, Yangtze Memory (NAND FLASH) e Hefei Changxin (DRAM), saranno prodotti in massa nel 2020, il che rappresenterà senza dubbio enormi opportunità di crescita per i produttori nazionali con tecnologie di packaging avanzate.

3. Packaging Fan-out

Entrando nell’era del 5G, al fine di ottenere una maggiore velocità di trasmissione dei dati e capacità di larghezza di banda, è necessario utilizzare onde elettromagnetiche a frequenza più elevata come mezzo di trasmissione e le lunghezze d’onda sono più corte ed entrano nel livello delle onde millimetriche. Le due frequenze principali nell’era del 5G, la banda di frequenza Sub-6GHz e la banda di frequenza a onde millimetriche a 28GHz, a causa dell’aumento della frequenza, il risultato della diminuzione della lunghezza d’onda è che l’antenna è più corta, quindi l’antenna dovrebbe essere integrata nel chip nell’era del chip 5G per semplificare il design e ridurre i costi.

Esistono due possibili tecnologie di packaging per i chip 5G di nuova generazione: AiP (Antenna in Package) con un substrato e un package fan-out senza una scheda portante. Poiché la seconda soluzione di packaging fan-out non richiede un substrato, può ridurre ulteriormente i costi e ridurre le dimensioni del chip sulla base dell’integrazione di più chip, quindi la tecnologia di packaging fan-out potrebbe diventare la tecnologia mainstream del packaging dei chip 5G.

Ogni modulo elettronico in auto adotta diverse tecnologie di packaging e il packaging del chip radar a onde millimetriche nell’elettronica automobilistica utilizzerà anche un gran numero di tecnologie di packaging Fan-out.

La fabbrica nazionale di packaging e test Changdian Technology ha acquisito la tecnologia di packaging eWLB dopo aver acquisito Xingke Jinpeng, diventando uno dei primi produttori di packaging e test nel campo del radar a onde millimetriche. Si prevede che Huatian Technology farà degli sforzi in questo campo dopo le recenti scoperte tecnologiche.

Direzione dello sviluppo tecnologico

Esistono due tipi di packaging di semiconduttori: packaging tradizionale e packaging avanzato. Con la continua espansione della scala del packaging avanzato, la proporzione si è gradualmente avvicinata e superato la tendenza del packaging tradizionale. Per l’industria dei semiconduttori, il packaging e il test non sono più solo un collegamento di fonderia separato nel passato, ma una soluzione integrata che combina design, materiali e attrezzature.

Pertanto, il packaging avanzato sta diventando sempre più importante nel campo del packaging e del test dei semiconduttori. Secondo le previsioni di Yole, il mercato globale del packaging avanzato raggiungerà il 44% dell’intero servizio di packaging di circuiti integrati entro il 2020, con un reddito operativo annuo di circa 31,5 miliardi di dollari USA; il mercato cinese del packaging avanzato raggiungerà i 4,6 miliardi di dollari USA nel 2020, con un tasso di crescita annuale composto del 16%. Dal punto di vista tecnico, FOWLP, SiP e 3DTSV sono le tre tecnologie di packaging e test avanzate più importanti.

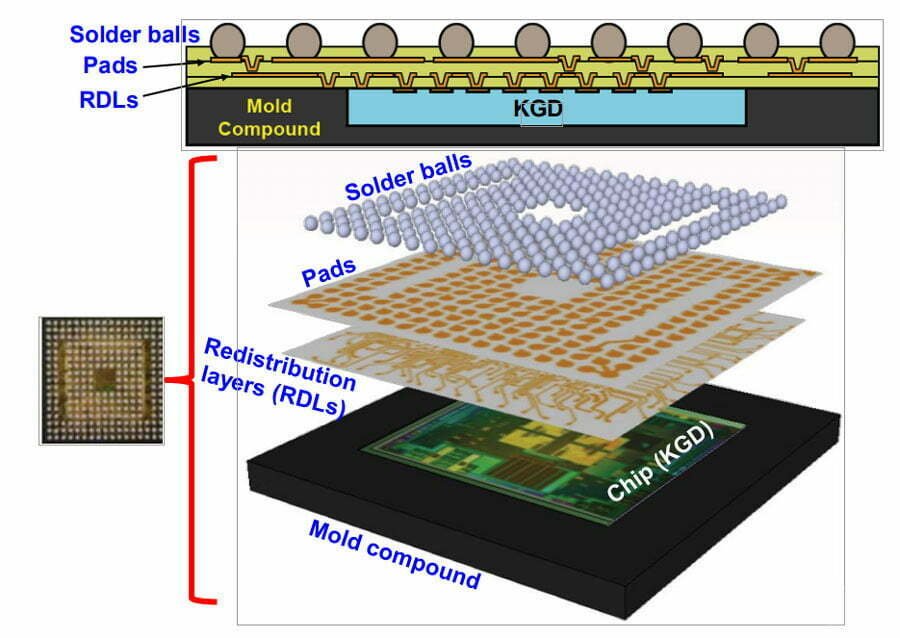

1. Packaging FOWLP

Il package FOWLP si riferisce a un nuovo metodo per combinare più die da processi eterogenei in un package compatto. È stato proposto per la prima volta da Intel. I vantaggi di FOWLP rispetto alla tecnologia di packaging fan-in sono: spessore del package ridotto, scalabilità (per aumentare il numero di I/O), prestazioni elettriche migliorate, buone prestazioni termiche e un processo senza substrato.

2. Packaging SiP

System-in-package (SiP) è un nuovo tipo di tecnologia di packaging all’avanguardia nel campo del packaging IC, che integra uno o più chip IC e componenti passivi in un unico package. SiP è una soluzione ideale che combina i vantaggi delle risorse principali esistenti e dei processi di produzione di semiconduttori per ridurre i costi e abbreviare i tempi di commercializzazione. Allo stesso tempo, supera le difficoltà come la compatibilità dei processi, il mixaggio dei segnali, le interferenze di rumore e le interferenze elettromagnetiche in SOC. Inoltre, l’applicazione di SiP è molto ampia. Attualmente, il valore della produzione di smartphone rappresenta la percentuale più alta, circa il 70%.

La crescente domanda di packaging SiP derivante dall’uso commerciale della tecnologia 5G. Innanzitutto, a causa dell’aumento del valore di RF stand-alone, le dimensioni complessive del mercato RF front-end sono cresciute rapidamente. C’è una tendenza generale alla modularizzazione di RF front-end, antenna 5G a onde millimetriche e componenti di integrazione RF, che si basano solitamente su GaAs. L’antenna 5G è composta principalmente da LCP (Liquid Crystal Polymer) e il packaging SiP è ben adatto per l’integrazione eterogenea. Si prevede che il packaging SiP diventerà più popolare nel settore RF.

3. Packaging 3D - TSV

Il packaging 3D migliora le prestazioni del core come dimensioni, peso, velocità, resa e consumo energetico ed è considerato dalla maggior parte dei produttori di semiconduttori come il metodo di packaging più promettente. Poiché i tentacoli del packaging avanzato continuano ad estendersi alle tecnologie avanzate con prestazioni elevate e integrazione ad alta densità, TSV, noto come tecnologia di packaging 3D di quarta generazione, dovrebbe diventare una forza trainante sostenibile per lo sviluppo futuro del packaging avanzato.