Nell'era dei server basati sull'intelligenza artificiale, degli smartphone 5G e dei veicoli autonomi, le prestazioni di un chip dipendono interamente dal "sistema nervoso" che lo sostiene: il substrato del circuito integrato. Man mano che la densità dei circuiti raggiunge i propri limiti fisici, la scelta del processo di fabbricazione determina l'integrità del segnale e l'affidabilità del prodotto finale.

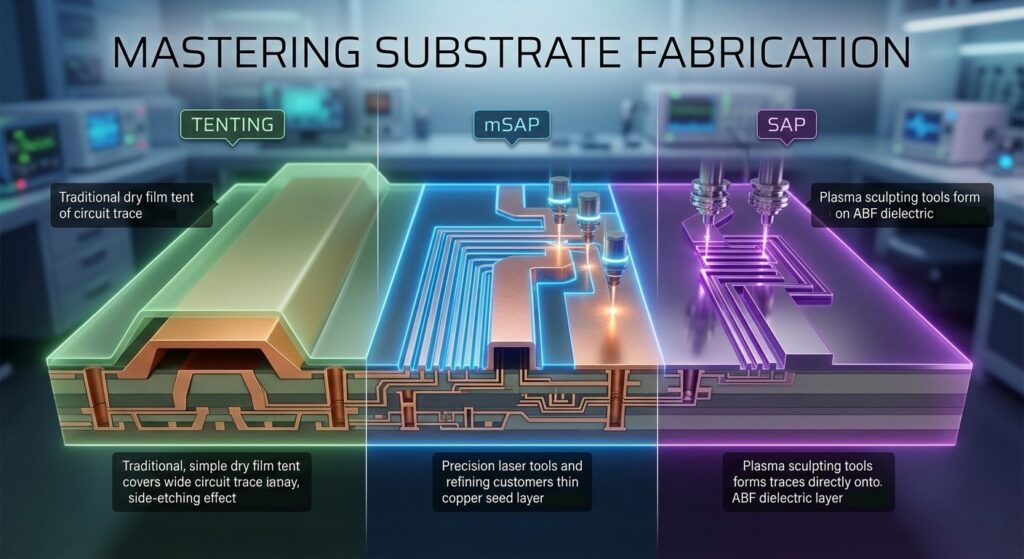

Oggi, tre principali "strumenti di modellazione" dominano il settore: Tenting (sottrattivo), mSAP (processo semi-additivo modificato) e SAP (processo semi-additivo). Questa guida ne analizza i meccanismi tecnici, i pro e i contro e il ruolo che ricoprono nell'ecosistema dell'elettronica moderna.

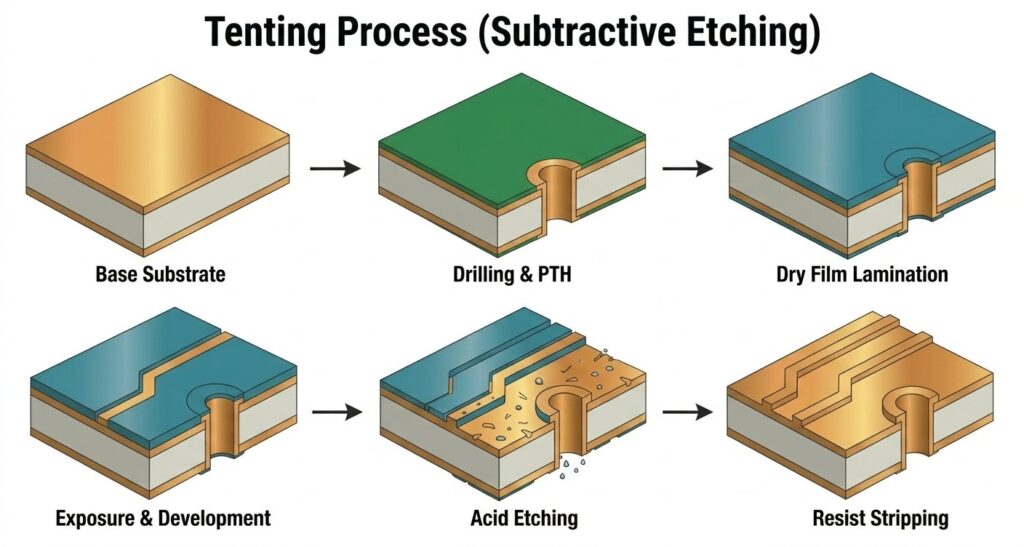

1. Processo di incisione (metodo sottrattivo)

Il processo di tenting è la tecnologia di formazione dei circuiti più tradizionale e diffusa nel settore dei circuiti stampati (PCB) e dei substrati a bassa densità. Il suo principio fondamentale è "coprire e rimuovere", proprio come quando si scolpisce un sigillo da un blocco di pietra.

Come funziona: si parte da un laminato rivestito di rame (CCL) con una lamina di rame spessa (di solito > 12 μm). Una pellicola secca (fotoresist) copre le aree del circuito previste come una "tenda" sopra i fori (da cui il nome). Il rame non protetto viene quindi rimosso mediante incisione chimica.

Il problema (incisione laterale): poiché l'incisione rimuove il rame contemporaneamente in verticale e in orizzontale, crea una sezione trasversale "trapezoidale". Questa "incisione laterale" limita la precisione della larghezza della linea e dello spazio ($L/S$) a circa $30\mu m/30\mu m$.

Ideale per: Elettronica di consumo standard, PCB per il settore automobilistico e substrati BGA tradizionali con saldatura a filo (WB BGA).

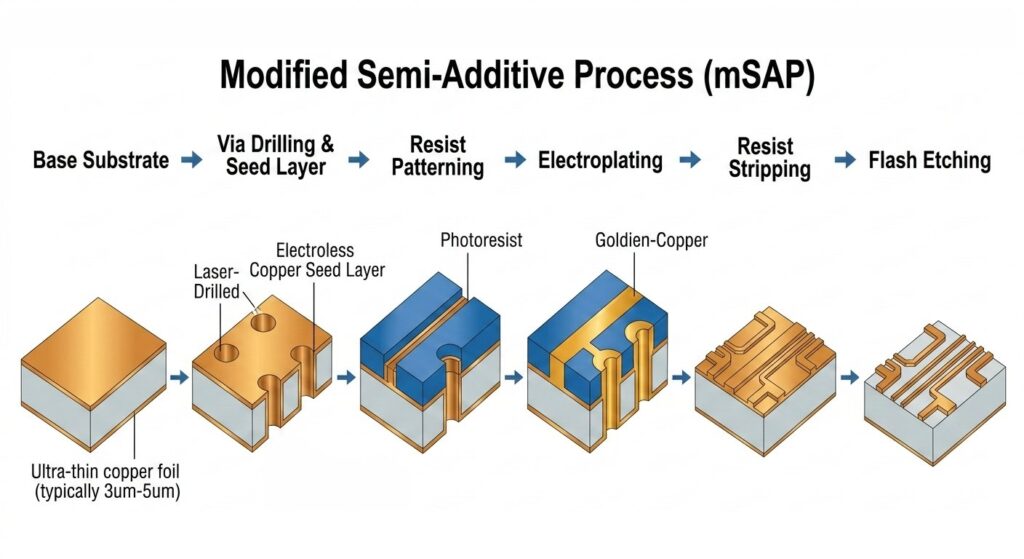

2. mSAP (Processo semi-additivo modificato)

Con l'aumento del numero di pin e l'accelerazione dei segnali, l'mSAP si è affermato come ponte tra i PCB tradizionali e i substrati per circuiti integrati di fascia alta. Attualmente rappresenta la scelta prevalente per i substrati FCBGA utilizzati nei chip di rete e nei processori per smartphone di fascia alta.

Come funziona: invece del rame spesso, l'mSAP parte da una base di rame ultrasottile (di solito 3–5 μm) o da uno "strato seme" depositato chimicamente. Il circuito viene "aggiunto" tramite elettrodeposizione selettiva fino allo spessore desiderato.

Il vantaggio: dopo la placcatura, una rapida "incisione flash" rimuove lo strato di base ultrasottile. Poiché la base è così sottile, il tempo di incisione è minimo, con il risultato di pareti del circuito rettangolari quasi verticali con capacità $L/S$ fino a $10\mu m/10\mu m$.

Ideale per: AP per smartphone di fascia alta (serie Apple A, Snapdragon), Chip Scale Packaging (FCCSP) e PCB simili a substrati (SLP).

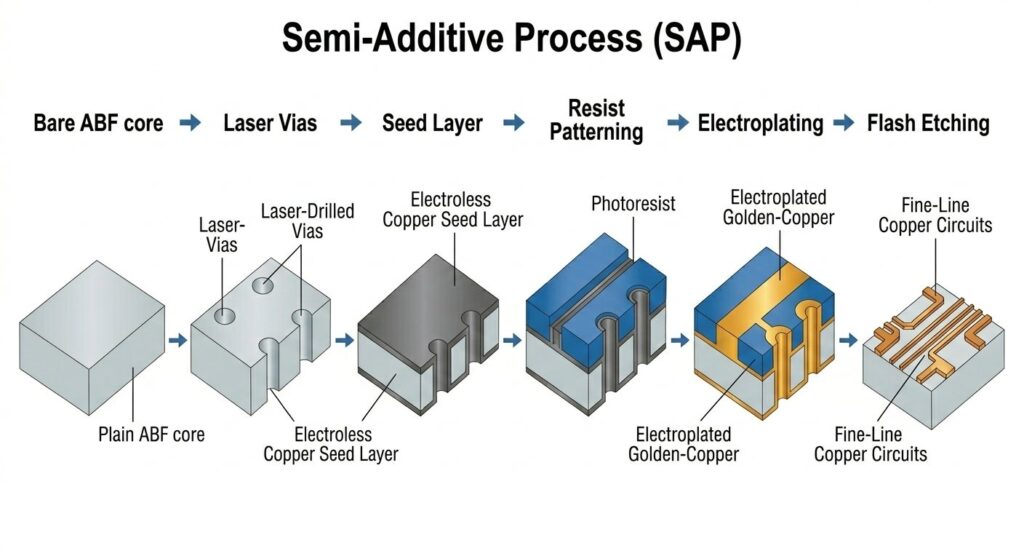

3. SAP (processo semi-additivo)

La tecnologia SAP rappresenta il massimo livello di precisione dei circuiti ed è spesso definita una versione "purificata" della tecnologia mSAP. Essa rinuncia completamente all'uso della lamina di rame a favore della "pura aggiunta".

Come funziona: utilizza un materiale dielettrico privo di rame, in particolare l'ABF (Ajinomoto Build-up Film). Uno "strato seme" microscopico ($< 1\mu m$) viene depositato chimicamente sulla superficie liscia, seguito da una placcatura selettiva per costruire i circuiti.

Il vantaggio: poiché lo strato di semina è quasi inesistente, l'incisione non ha alcun impatto sulla morfologia del circuito. Ciò consente una precisione estrema ($L/S < 10\mu m$) e un controllo superiore dell'impedenza per i segnali ad alta velocità.

Ideale per: calcolo ad alte prestazioni (HPC), acceleratori AI (Nvidia H100) e packaging avanzato come CoWoS e HBM.

4. Tabella comparativa: Tenting vs. mSAP vs. SAP

| Feature | Tenting | mSAP | SAP |

|---|---|---|---|

| Core Principle | Subtractive: Etch away thick copper foil | Additive: Plate over ultra-thin copper base | Pure Additive: Seed layer on copper-free dielectric |

| Line Precision (L/S) | > 30μm | 10μm - 30μm | < 10μm |

| Cross-section Shape | Trapezoidal (Side-etching) | Near-Rectangular | Perfectly Rectangular |

| Base Material | Standard CCL | Ultra-thin copper foil | ABF (Ajinomoto Build-up Film) |

| Primary Application | Consumer PCBs / Motherboards | Smartphone AP / High-end HDI | AI Accelerators / CPU / GPU Substrates |

| Cost & Maturity | Low Cost / Highly Mature | Medium-High / Mainstream High-end | Very High / Cutting-edge |

Uno sguardo al futuro: il futuro della produzione

Il settore si sta orientando verso un approccio "ibrido" volto a bilanciare costi e prestazioni, utilizzando la tecnica del "tenting" per gli strati centrali e mSAP/SAP per gli strati esterni ad alta densità. Man mano che la domanda di IA spinge i limiti della Legge di Moore, le tecnologie emergenti come i substrati in vetro e i die integrati continueranno a evolversi parallelamente a questi tre processi fondamentali.

Comprendere le sfumature di questi metodi di fabbricazione è il primo passo per padroneggiare il complesso panorama del packaging dei chip moderni e della sicurezza hardware.