O teste de IC serve para detectar se o chip tem defeitos de design ou defeitos físicos causados pelo processo de fabricação. O processo pode ser realizado usando vários métodos de teste.

A embalagem de IC é o processo de envolver um circuito integrado (IC) em uma embalagem protetora. Esse processo protege o IC contra danos e garante que ele funcione corretamente. Ele também permite a conexão do IC a outros dispositivos e circuitos.

Como testar um IC usando um testador de IC?

Kit de teste ic

Existem alguns tipos diferentes de kits de teste de IC disponíveis no mercado, cada um projetado para uma finalidade específica. Por exemplo, alguns kits de teste de IC são projetados para testes de uso geral. Enquanto outros são projetados para aplicações específicas, como ICs automotivos ou ICs de potência.

A maioria dos kits de teste de IC inclui uma variedade de acessórios básicos, como um multímetro, sondas, testador digital de IC e cabos de teste. Alguns kits também podem incluir equipamentos mais especializados, como um osciloscópio ou analisador lógico.

Método de teste

Existem várias maneiras diferentes de testar ICs, mas o método mais comum é chamado de teste em circuito (ICT). Esse tipo de teste é feito conectando um dispositivo de teste ao dispositivo em teste (DUT). Em seguida, executamos uma série de testes para verificar as funcionalidades básicas.

O ICT pode ser usado para testar ICs digitais e analógicos. Para ICs digitais, o testador enviará uma série de sinais de entrada para o DUT. Em seguida, verifica as saídas para ver se correspondem aos resultados esperados. Os ICs analógicos são normalmente testados usando uma técnica chamada teste dinâmico. Durante esse processo, o testador aplica uma série de sinais ao DUT e, em seguida, mede a resposta.

Existem diferentes empresas que fabricam testadores ICT, você precisa escolher um que seja compatível com seus ICs específicos. Depois de ter um testador, você precisará criar um dispositivo de teste que se conecte ao DUT. O dispositivo de teste pode aplicar os sinais necessários ao DUT e também medir a resposta.

Depois de ter os dois, você precisará escrever um programa de teste para verificar os resultados. Esse pode ser um processo demorado, mas é importante para garantir que seus ICs estejam funcionando corretamente.

Tipos de testes

Teste de continuidade do IC

O teste de continuidade do IC é simples e pode ser usado para determinar se os ICs estão funcionando corretamente.

Este teste é realizado conectando um multímetro ao IC e medindo a resistência entre os vários pinos.

Se o IC estiver funcionando corretamente, a resistência deve ser baixa (geralmente inferior a 10 ohms). Caso contrário, a resistência será alta (geralmente superior a 10 ohms).

teste de nível

O teste de nível IC é um tipo de teste elétrico para determinar a função e o desempenho dos circuitos integrados (ICs).

Este teste é normalmente realizado em ICs que já estão instalados numa placa de circuito.

O objetivo do teste é verificar se o IC está funcionando corretamente e atende às especificações para o uso pretendido.

Existem vários métodos de teste diferentes para o teste de nível de IC, incluindo teste lógico, teste funcional e teste paramétrico.

Caminho de desenvolvimento da embalagem IC

A embalagem passou aproximadamente pelo seguinte processo de desenvolvimento:

1. Em termos de estrutura:

TO → DIP → PLCC → QFP → BGA → CSP → WLP e SiP, etc.

2. Materiais:

Metal, cerâmica -> cerâmica, plástico -> plástico;

3. Forma dos pinos:

Pino longo em linha -> pino curto ou montagem sem pino -> bola saliente

4. Método de montagem:

Inserção através de orifício -> Montagem em superfície -> Montagem direta

5. A força motriz da melhoria contínua da embalagem:

Tamanho menor, mais tipos de chips, mais I/O

6. Dificuldades:

O processo está se tornando cada vez mais complexo, e é necessário levar em consideração a dissipação de calor e a condutividade elétrica ao reduzir o volume.

Características e competitividade central

1. Fortes atributos de fabricação

A capacidade de produção depende totalmente da aquisição de equipamentos (investimento de capital) e, tal como na fabricação tradicional, também passará pelo processo de aumento da capacidade e otimização dos processos. Com a escala vem a acumulação de experiência e as vantagens da tecnologia de ponta.

2. A escala de embalagem e teste determina a estrutura do cliente

Os grandes fabricantes de design só cooperam com fabricantes de testes com uma determinada escala. Se a escala não aumentar, é difícil aceitar grandes encomendas e otimizar a estrutura de clientes. Por isso, as empresas com tecnologia e escala líderes entrarão num círculo virtuoso: tecnologia líder → desenvolvimento de clientes → expansão do financiamento → aumento da capacidade de produção → otimização do processo → tecnologia líder, e irão gradualmente aumentar a diferença em relação aos concorrentes.

3. Competitividade essencial

As duas características acima determinam a competitividade central das empresas de testes profissionais de IC:

Capacidade de P&D: foco no desenvolvimento de procedimentos e soluções de teste.

Grau de comercialização: as capacidades de desenvolvimento de programas de teste e otimização de processos provêm da experiência de teste de diferentes tipos de chips trazida por um grande número de clientes.

Processo de teste perfeito: por meio da integração estreita do design upstream e do processamento de wafer, o processo e o procedimento de teste são continuamente otimizados.

Capacidade de operação de capital: o atual estágio de desenvolvimento doméstico determina que a escala é a premissa do desenvolvimento. Portanto, a capacidade de financiamento que corresponde à tecnologia e à força do mercado é o suporte para o desenvolvimento e o crescimento das empresas.

mercado de embalagem e teste de circuitos integrados

1. Embalagem e escala de teste de IC

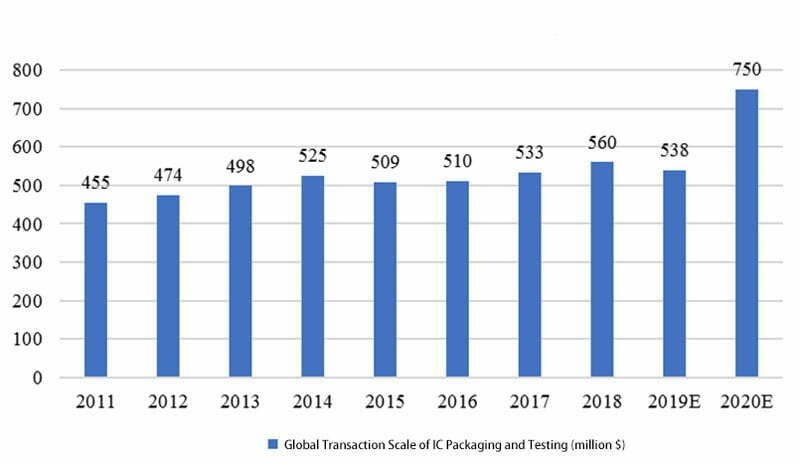

1.1 Transações globais de embalagem e teste de circuitos integrados (2011-2020)

Em 2019, o setor de semicondutores como um todo desacelerou e apresentou crescimento negativo, assim como o mercado de embalagem e teste de chips. No entanto, o mercado se recuperou posteriormente devido à demanda por 5G, IA, IoT, computação em nuvem e big data. Especialistas previram que o mercado geral de embalagem e teste de chips em 2024 poderá atingir US$ 75 bilhões.

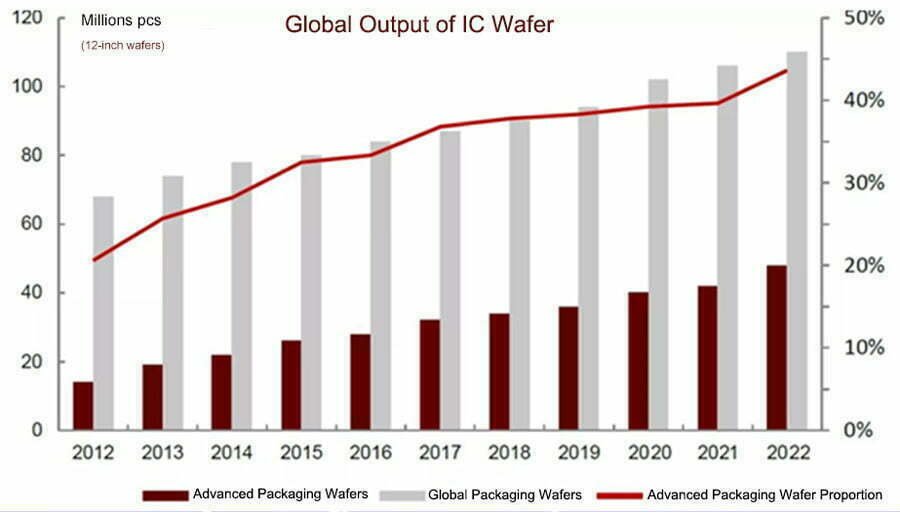

1.2 Produção global de wafers IC (2012-2022)

Com a aceleração de campos emergentes, como 5G, IoT e IA, o tamanho necessário dos chips está ficando cada vez menor. Ao mesmo tempo, há cada vez mais tipos de chips. O número de pinos de E/S também aumentou significativamente, e a demanda por embalagens avançadas aumentou gradualmente.

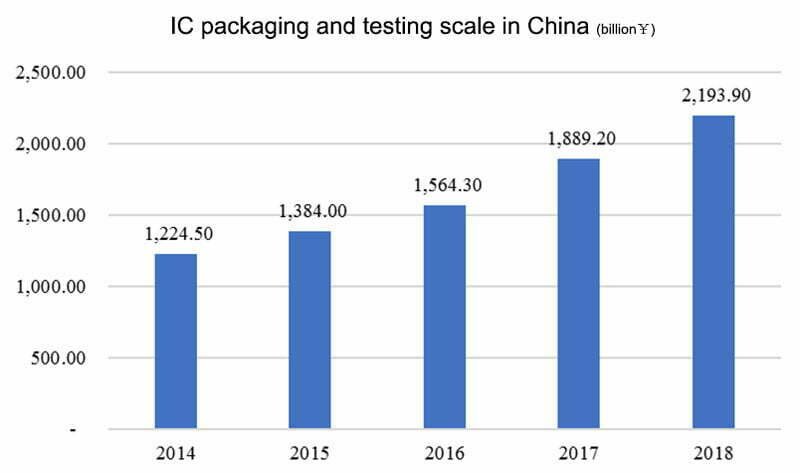

1.3 Escala de embalagem e testes iC na China (2014-2018)

Em 2018, a capacidade de embalagem e teste de IC na China continental atingiu 217,44 bilhões de peças, e o tamanho do mercado da indústria de embalagem e teste de IC atingiu 219,39 bilhões de yuans, um aumento anual de 16,1%.

2. O crescimento da escala de embalagens avançadas

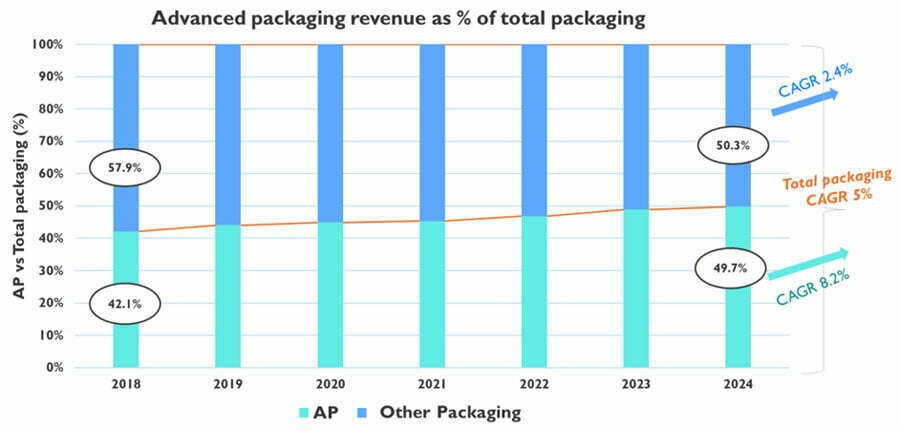

2.1 Proporção de embalagens IC avançadas no total

De acordo com as estatísticas da Yole, embora a indústria de semicondutores em geral tenha desacelerado e apresentado um crescimento negativo em 2019, o tamanho do mercado de embalagens avançadas manterá uma tendência de crescimento. Em 2018, o tamanho do mercado de embalagens avançadas foi de US$ 27,6 bilhões.

Crescendo a uma taxa composta anual de 8%, atingindo aproximadamente US$ 44 bilhões até 2024. O mercado de embalagens tradicionais crescerá a uma taxa composta anual de 2,4%, enquanto a CAGR de toda a indústria de embalagens de IC atingirá 5%.

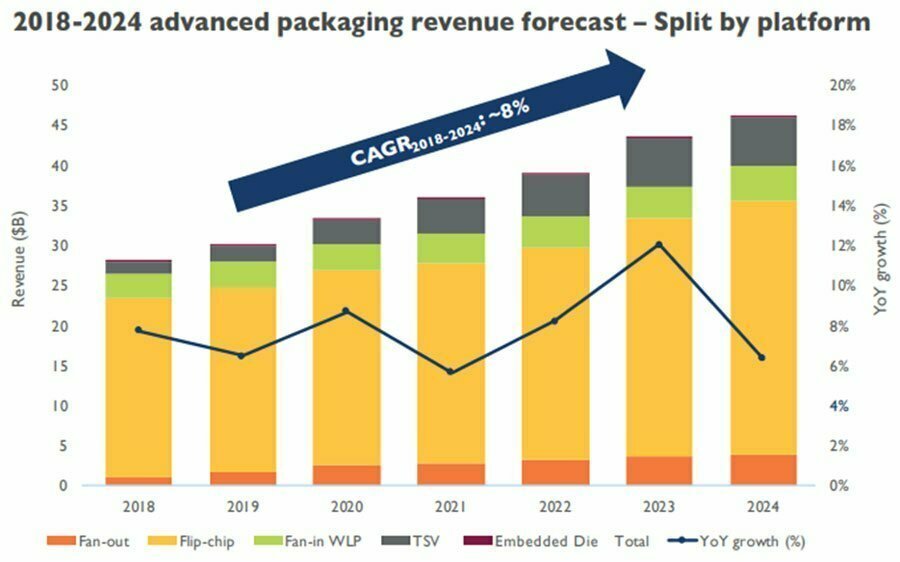

2.2 Tendências de previsão de receita para embalagens avançadas (2018-2024)

No setor de embalagens avançadas, a tecnologia flip-chip representa a maior proporção. Em 2018, a receita com embalagens e testes flip-chip representou cerca de 81% do mercado de embalagens avançadas. Até 2024, devido ao rápido desenvolvimento de outras tecnologias, ela cairá para 72%.

De 2018 a 2024, TVS, ED e fan-out são as tecnologias que mais crescem. A taxa de crescimento da receita de embalagens 2.5D/3D (TSV), ED e fan-out (Fan-out) está prevista para ser, respectivamente, 26%, 49% e 26%.

O CAGR do Fan-in WLP 2018-2024 é relativamente baixo, apenas 6,5%, e o tamanho do mercado de die embutido em 2018 é inferior a US$ 25 milhões.

No entanto, o CAGR será de até 49% nos próximos cinco anos, e os principais fatores impulsionadores virão da demanda por instalações de comunicação, eletrônicos automotivos e mercados móveis.

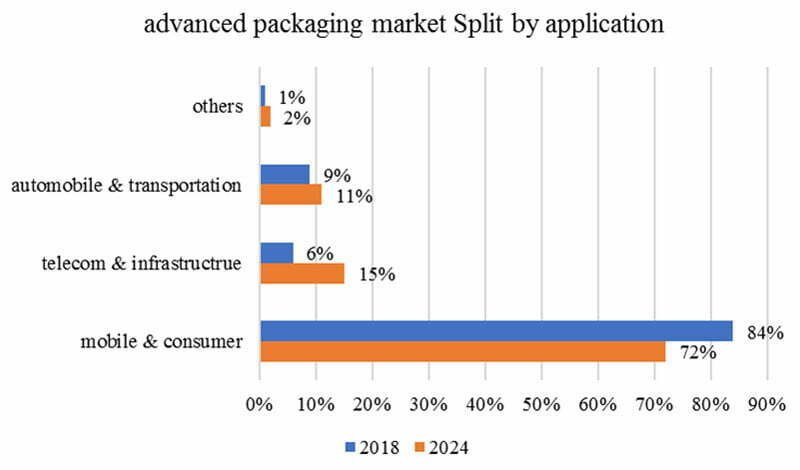

2.3 aplicações avançadas de embalagem

Por área de aplicação, em 2018, as aplicações móveis e de consumo representaram 84% do mercado total de embalagens avançadas. De 2019 a 2024, a CAGR deste segmento do mercado de aplicações foi de 5% e, em 2024, representou 72% do mercado total de embalagens avançadas.

O segmento de telecomunicações e infraestrutura é o segmento de crescimento mais rápido do mercado de embalagens avançadas (cerca de 28%), e sua participação no mercado crescerá de 6% em 2018 para 15% em 2024.

Ao mesmo tempo, a participação de mercado do segmento automotivo e de transporte cresceu de 9% em 2018 para 11% em 2024.

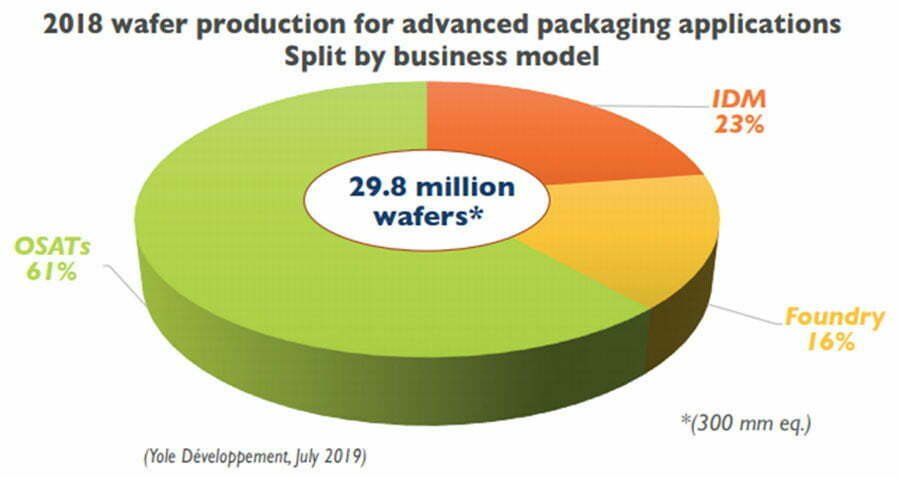

Em 2018, as fundições profissionais de embalagem e teste de chips representaram 61% do mercado de embalagem e teste avançados, enquanto as empresas do tipo IDM representaram 23% e os fabricantes do tipo fundição representaram 16%.

Panorama competitivo

1. As 10 maiores empresas globais (2018-2019)

O mercado de embalagem e teste de chips é relativamente concentrado. Os dez maiores fabricantes controlam cerca de 80% do mercado. Fabricantes da China continental e de Taiwan dominam o mercado. Por muitos anos, a indústria de embalagem e teste de Taiwan conquistou quase metade da receita operacional mundial, estabelecendo-se firmemente entre as dez maiores.

Independentemente da receita de embalagem e teste de chips das IDMs (como Intel e Samsung), a ASE e a Amkor estão firmemente entre as duas primeiras em embalagem e teste profissional de chips.

2. Oportunidades e desafios

Mudanças na cadeia de suprimentos de semicondutores, mudanças nos modelos de negócios e incertezas nas relações comerciais entre os EUA e a China criaram oportunidades para alguns fabricantes e ameaças para outros.

2.1 Extensão da cadeia industrial

Neste ambiente empresarial em constante mudança, a cadeia de abastecimento de semicondutores está mudando em todos os níveis. Alguns fornecedores conseguiram expandir novos modelos de negócios com sucesso.

Isso afetou significativamente a cadeia de fabricação de ICs, enquanto outros fabricantes não conseguiram aproveitar o momento. Diferentes fornecedores têm diferentes motivadores que os levam a expandir para novos negócios.

Por exemplo, empresas de software como Google, Microsoft, Facebook e Alibaba estão projetando seus próprios processadores para obter integração/personalização em nível de sistema e controle da cadeia de suprimentos no nível de montagem.

A maior mudança é que as fundições estão começando a se expandir para o negócio de embalagens avançadas. Embora sejam relativamente "novatas", seu impacto é enorme.

2.2 Inovação em tecnologia de embalagem

A TSMC lidera a inovação em embalagens fan-out e plataformas avançadas de embalagens 3D. Eles oferecem uma variedade de produtos, como InFO (e suas variantes), CoWoS, WoW, 3D SoIC e muito mais.

A embalagem avançada tornou-se um negócio maduro para a TSMC. A empresa espera que ela gere uma receita de US$ 3 bilhões em 2019, o que a colocaria em quarto lugar no ranking da OSAT.

A UMC é uma importante fornecedora de interposers de silício para embalagens 2.5D. Recentemente, ela fez uma parceria com a Xperi para otimizar e comercializar as tecnologias ZiBond e DBI para vários dispositivos semicondutores.

Enquanto isso, a Wuhan Xinxin (XMC) fornece pacotes 3D IC TSV para sensores de imagem e aplicações de alto desempenho. Coletivamente, esses participantes têm desempenhado um papel importante na mudança da embalagem de substratos para plataformas de silício.

2.3 As embalagens de nível de sistema tendem a ser populares

É uma tendência que os participantes da cadeia da indústria de embalagens SiP se expandam para os setores upstream e downstream. Na cadeia tradicional da indústria de embalagens SiP, as empresas representativas de embalagem e teste de IC incluem Changdian Technology e ASE, que fornecem principalmente produtos de embalagem e teste padrão em nível funcional. A empresa representativa de embalagem em nível de sistema é a USI, que atua principalmente na embalagem de sistemas em nível de módulo. Essas duas empresas pertencem à relação upstream e downstream, e seus processos e equipamentos envolvidos são diferentes.

2.4 Chips incorporados

Por outro lado, fabricantes de substratos IC e PCB, como Samsung Electro-Mechanics (SEMCO), Unimicron, AT&S e Shinko Electric (Shinko), estão aproveitando os chips embutidos (e passivos) em pacotes fan-out no nível do painel e substratos orgânicos. componentes) no espaço de embalagens avançadas e estão corroendo a participação de mercado da OSAT (especialmente nos negócios envolvendo embalagens avançadas).

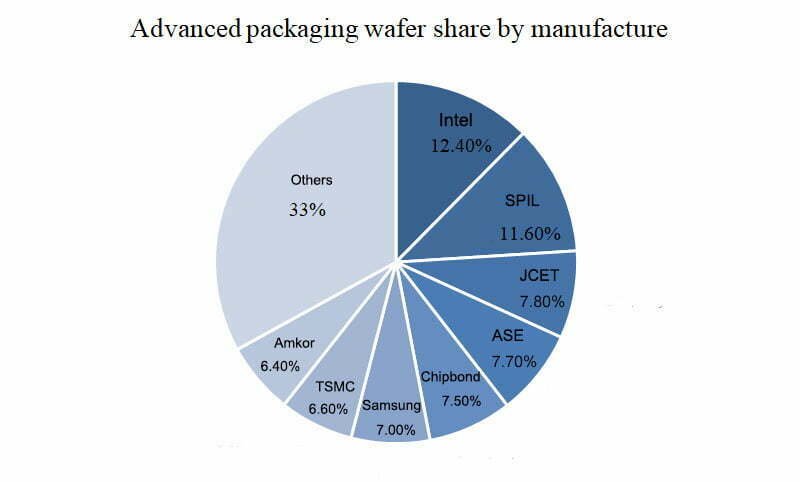

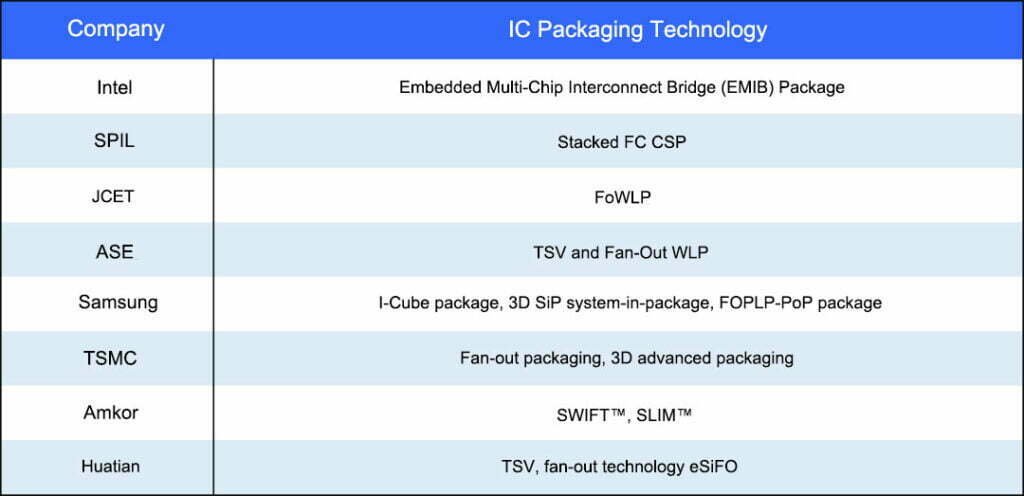

3. Quota de mercado das embalagens avançadas para wafers

Em comparação com a concentração geral do mercado de embalagens e testes, a concentração do mercado de embalagens e testes avançados é relativamente baixa. Em 2017, os oito principais fabricantes representavam 67% da quota de mercado das embalagens avançadas.

Os fornecedores no mercado de embalagens avançadas têm diferentes áreas de especialização:

Situação da indústria de embalagens de circuitos integrados da China

A indústria chinesa de embalagens IC começou muito cedo e desenvolveu-se rapidamente, baseando-se principalmente em produtos de embalagem tradicionais. Nos últimos anos, os fabricantes nacionais passaram por fusões e aquisições. Atualmente, a plataforma tecnológica chinesa está basicamente sincronizada com os fabricantes estrangeiros. Além disso, tecnologias avançadas de embalagem, como BGA, TVS, WLCSP e SiP, têm sido produzidas em massa.

No entanto, ainda existe uma certa diferença entre a receita total das embalagens avançadas em Taiwan e nos Estados Unidos. De acordo com as estatísticas da TrendForce, a receita das embalagens avançadas da China em 2018 foi de cerca de 52,6 bilhões de yuans. Isso representou 25% da receita total doméstica de embalagens e testes, inferior à proporção global de 41%. Portanto, ainda há muito espaço para crescimento no futuro.

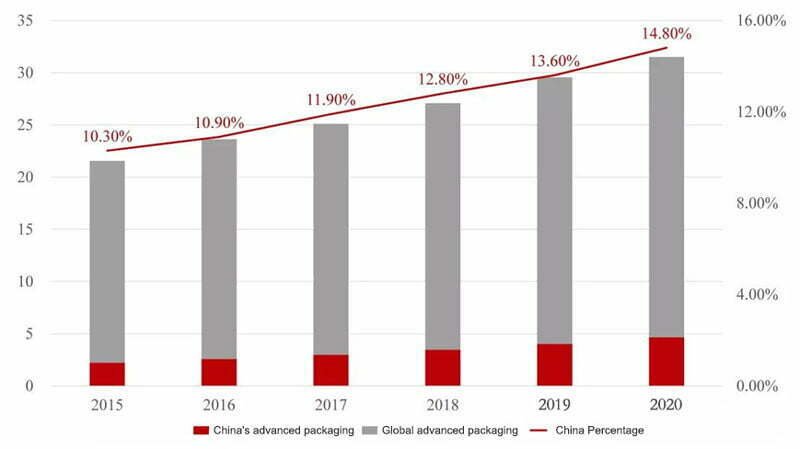

Mercado avançado de embalagens de circuitos integrados da China

Além disso, existe também uma grande diferença entre as empresas de embalagem do continente e os principais fabricantes internacionais. Especialmente, a diferença é evidente na tecnologia de embalagem de circuitos integrados de alta densidade, como a tecnologia de embalagem de chips HPC. A tecnologia de empilhamento 3D multi-chip SoC proposta pela TSMC. Ela adota uma estrutura de ligação sem saliências, que pode melhorar significativamente a velocidade geral de computação da CPU/GPU e da memória. A Intel também propôs um conceito de embalagem 3D semelhante, empilhando memória em chips de CPU e GPU.

O valor global da produção do mercado chinês de embalagens avançadas é relativamente baixo, mas está crescendo rapidamente e sua proporção está se expandindo. Dados da Yole. Em 2017, o valor da produção de embalagens avançadas da China foi de US$ 2,9 bilhões, representando 11,9% do total mundial, e chegará a US$ 4,6 bilhões em 2020, representando 14,8% do total mundial. De acordo com os dados, as empresas chinesas de embalagem e testes aceleraram o aumento da capacidade de produção no campo das embalagens avançadas em 2018, com uma taxa de crescimento de 16%, o dobro da taxa global.

força motriz do mercado

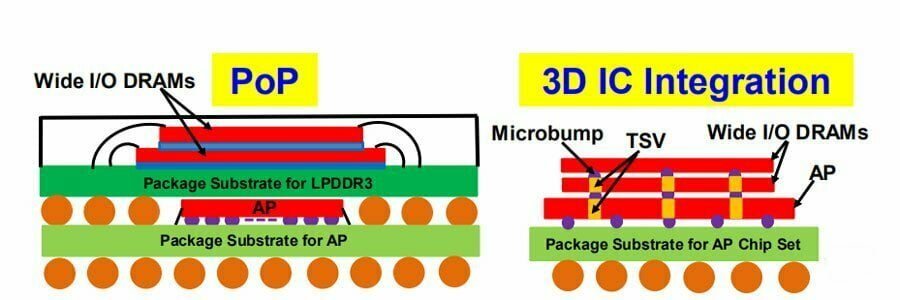

Existem dois caminhos de desenvolvimento para embalagens avançadas:

um é reduzir o tamanho para torná-lo próximo ao tamanho do chip. Um indicador importante é a relação entre a área do chip e a área da embalagem. Quanto mais próxima essa relação estiver de 1, melhor, incluindo WLCSP, FC, Bumping, Fanout, etc.

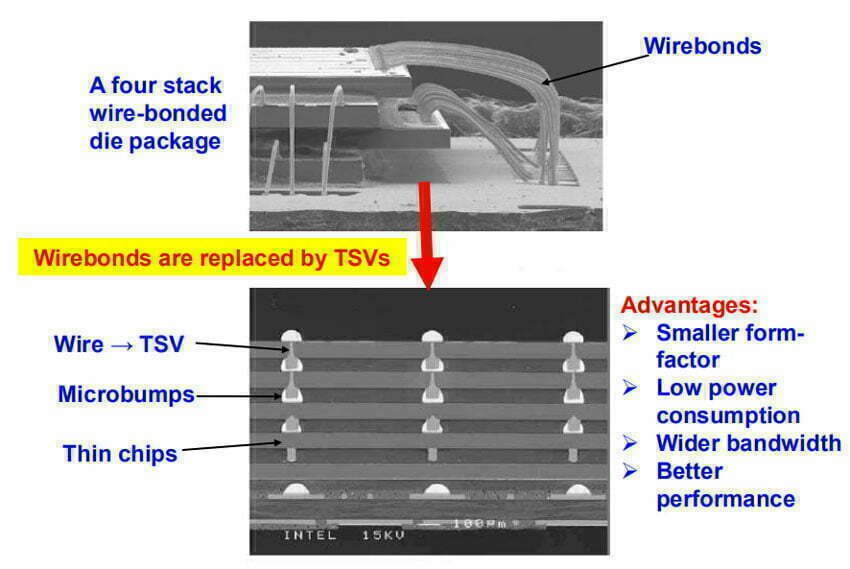

O segundo é o desenvolvimento funcional, que enfatiza a integração heterogênea e fornece multifuncionalidade na miniaturização do sistema, incluindo TSV, SIP e assim por diante.

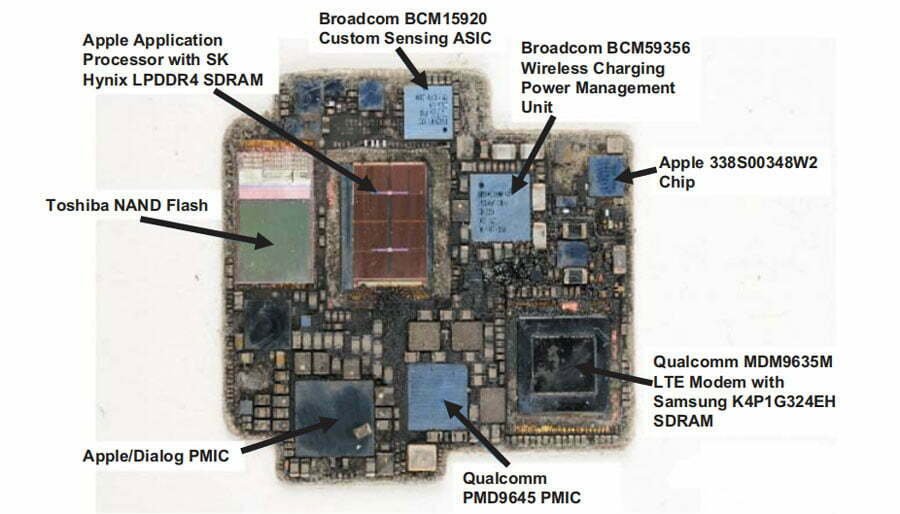

1. Tecnologia SIP

O processo global de fabricação de semicondutores está se aproximando do limite físico dos diodos. O processo mais avançado é o de 7 nm. Devido ao enorme investimento, torna-se cada vez mais caro melhorar ainda mais o desempenho do chip do lado da fabricação. A partir da embalagem do chip, a tecnologia SIP (system-in-package) combina chips com diferentes funções, como chips lógicos e memória.

Componentes passivos IPD, RF RF e sensores e outros chips são embalados em um único módulo, o que pode reduzir o tamanho do chip, melhorar o desempenho do chip e reduzir o consumo de energia. A Internet das Coisas (IoT) é um importante cenário de aplicação que promove o desenvolvimento da tecnologia de embalagem SIP, e os dispositivos vestíveis são um campo com grande potencial de aplicação para a tecnologia de sistema em pacote no futuro. O sensor de reconhecimento de impressão digital, o sensor de reconhecimento facial 3D, a rede sem fio WiFi e outros módulos funcionais do Apple Watch são embalados juntos, o que é o uso da tecnologia de módulo system-in-package (SiP) da ASE.

A tecnologia SIP integra com sucesso circuitos integrados, dispositivos discretos, dispositivos ópticos, memórias, capacitores cerâmicos multicamadas e resistores de chip em substratos finos, delgados e curtos, sem que suas informações interfiram entre si. Acreditamos que a Apple está pelo menos um ou dois anos à frente dos concorrentes na aplicação de embalagens de sistemas. De acordo com diferentes requisitos de aplicação e complexidade do produto, os tipos de SiP (sistema em pacote) podem ser divididos em módulos 2D contendo vários componentes ativos e passivos e módulos 3D mais complexos. Por exemplo, PiP (Package-in-Package) no sistema, PoP (Package-on-Package) e tecnologia de embalagem 2.5D/3D no sistema.

2. Tecnologia TSV

Como representante da tecnologia de embalagem 3D, a tecnologia TSV terá maiores aplicações no campo da embalagem de memória flash 3DNANDFLASH e embalagem de memória DRAM no futuro. A memória tornou-se a subseção com maior potencial de crescimento no campo dos semicondutores domésticos. Os dois principais projetos de memória, Yangtze Memory (NAND FLASH) e Hefei Changxin (DRAM), serão produzidos em massa em 2020, o que sem dúvida será uma grande oportunidade de crescimento para os fabricantes domésticos com tecnologia de embalagem avançada.

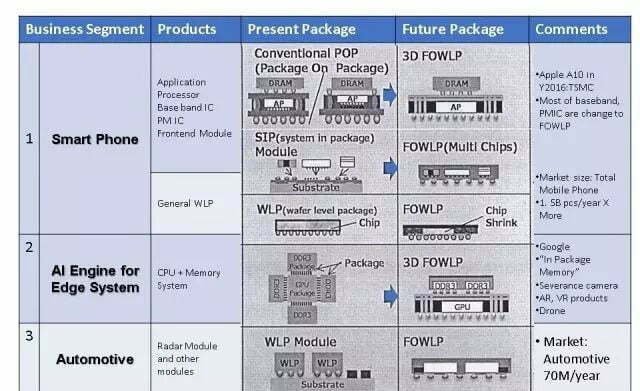

3. Fan-out

Ao entrar na era 5G, para obter maior taxa de transmissão de dados e capacidade de largura de banda, ondas eletromagnéticas de frequência mais alta devem ser usadas como meio de transmissão, e os comprimentos de onda são mais curtos e entram no nível de ondas milimétricas. As duas frequências principais na era 5G, a banda de frequência Sub-6GHz e a banda de frequência de ondas milimétricas de 28GHz, devido ao aumento da frequência, o resultado da queda do comprimento de onda é que a antena é mais curta, portanto, espera-se que a antena seja integrada ao chip na era dos chips 5G para simplificar o design e reduzir custos.

Existem duas tecnologias de embalagem possíveis para chips 5G de última geração: AiP (Antenna in Package) com um substrato e uma embalagem fan-out sem placa transportadora. Como o segundo esquema de embalagem fan-out não requer um substrato, ele pode reduzir ainda mais os custos e diminuir o tamanho do chip com base na integração de vários chips, de modo que a tecnologia de embalagem fan-out pode se tornar a tecnologia dominante da embalagem de chips 5G.

Cada módulo eletrônico do carro adota diferentes tecnologias de embalagem, e a embalagem do chip de radar de ondas milimétricas na eletrônica automotiva também utilizará um grande número de tecnologias de embalagem Fan-out.

A fábrica nacional de embalagem e testes Changdian Technology adquiriu a tecnologia de embalagem eWLB após adquirir a Xingke Jinpeng, tornando-se um dos primeiros fabricantes de embalagem e testes na área de radar de ondas milimétricas. Espera-se que a Huatian Technology envidar esforços nesta área após os recentes avanços tecnológicos.

Direção do desenvolvimento tecnológico

Existem dois tipos de embalagem de semicondutores: embalagem tradicional e embalagem avançada. Com a expansão contínua da escala de embalagens avançadas, a proporção aproximou-se gradualmente e ultrapassou a tendência das embalagens tradicionais. Para a indústria de semicondutores, a embalagem e o teste já não são apenas um elo separado da fundição no passado, mas uma solução integrada que combina design, material e equipamento.

Portanto, a embalagem avançada está se tornando cada vez mais importante no campo da embalagem e teste de semicondutores. De acordo com a previsão da Yole, o mercado global de embalagens avançadas atingirá 44% dos serviços gerais de embalagem de circuitos integrados até 2020, com uma receita operacional anual de aproximadamente US$ 31,5 bilhões; o mercado de embalagens avançadas da China atingirá US$ 4,6 bilhões em 2020, com uma taxa de crescimento anual composta de 16%. Do ponto de vista técnico, FOWLP, SiP e 3DTSV são as três tecnologias de embalagem e teste avançadas mais importantes.

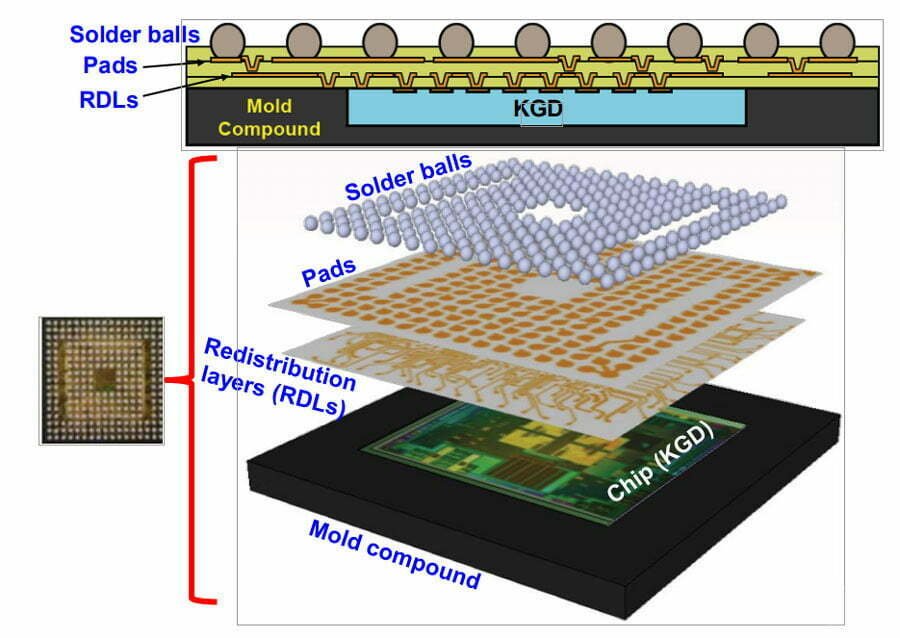

1. Embalagem FOWLP

O pacote FOWLP refere-se a um novo método de combinar vários chips de processos heterogêneos em um pacote compacto. Ele foi proposto pela primeira vez pela Intel. As vantagens do FOWLP em relação à tecnologia de empacotamento fan-in são: espessura reduzida do pacote, escalabilidade (para aumentar o número de I/Os), desempenho elétrico aprimorado, bom desempenho térmico e um processo sem substrato.

2. Embalagem SiP

O System-in-package (SiP) é um novo tipo de tecnologia de embalagem de ponta no campo da embalagem de IC, que integra um ou mais chips IC e componentes passivos em uma única embalagem. O SiP é uma solução ideal que combina as vantagens dos recursos essenciais existentes e dos processos de produção de semicondutores para reduzir custos e encurtar o tempo de lançamento no mercado. Ao mesmo tempo, supera dificuldades como compatibilidade de processos, mistura de sinais, interferência de ruído e interferência eletromagnética no SOC. Além disso, a aplicação do SiP é muito extensa. Atualmente, o valor de produção dos smartphones representa a maior proporção, cerca de 70%.

A crescente demanda por embalagens SiP provocada pelo uso comercial da tecnologia 5G. Primeiro, devido ao aumento no valor do RF autônomo, o tamanho geral do mercado de front-end de RF cresceu rapidamente. Há uma tendência geral para a modularização do front-end RF, da antena de ondas milimétricas 5G e dos componentes de integração RF, que geralmente são baseados em GaAs. A antena 5G é composta principalmente por LCP (polímero de cristal líquido), e a embalagem SiP é adequada para integração heterogênea. Espera-se que a embalagem SiP se torne mais popular no setor de RF.

3. Embalagem 3D - TSV

A embalagem 3D melhora o desempenho básico, como tamanho, peso, velocidade, rendimento e consumo de energia, e é considerada pela maioria dos fabricantes de semicondutores como o método de embalagem mais promissor. À medida que os tentáculos da embalagem avançada continuam a se estender para tecnologias avançadas com alto desempenho e integração de alta densidade, espera-se que o TSV, conhecido como a tecnologia de embalagem 3D de quarta geração, se torne uma força motriz sustentável para o desenvolvimento futuro da embalagem avançada.