В последние годы технология перераспределительного слоя (RDL) приобрела значительную популярность. Это революционное решение для упаковки, которое изменило подход к упаковке интегральных схем.

В этой статье мы рассмотрим определение RDL, его функции, преимущества, процесс, применение и сравнение с другими технологиями упаковки интегральных схем.

Что такое технология перераспределительного уровня?

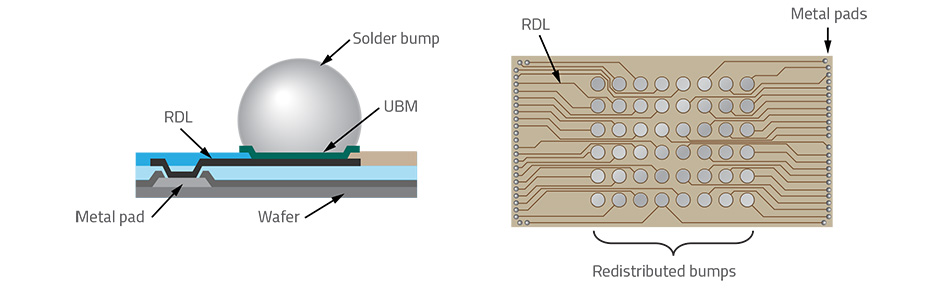

Слой перераспределения, также известный как RDL, представляет собой слой металла, который добавляется к интегральной схеме или микрочипу для перераспределения электрических соединений. Технология RDL — это передовое решение для упаковки интегральных схем (ИС), которое позволяет интегрировать несколько кристаллов в один корпус. Это процесс создания металлического слоя с рисунком поверх диэлектрического слоя, который перераспределяет входы/выходы (I/O) ИС в новое место. Новое местоположение обычно находится на краю кристалла, что позволяет подключить IC к печатной плате (PCB) с помощью стандартной технологии поверхностного монтажа (SMT). Технология RDL позволяет конструктору разместить кристалл компактным и эффективным образом, тем самым уменьшая общую площадь устройства.

Технология RDL играет ключевую роль в разработке современных электронных устройств, которые становятся все более компактными и сложными. Она позволяет создавать более компактные, быстрые и эффективные чипы. Обычно она используется в упаковке устройств MEMS, датчиков, силовых устройств, памяти, микропроцессоров и графических процессоров.

Функция слоя перераспределения

Слой перераспределения (RDL) играет важную роль в расширении и соединении плоскости XY при проектировании и производстве микросхем.

Перераспределить соединение ввода-вывода

Контактные площадки ввода/вывода (I/O) — это модули обработки выводов микросхемы, которые обычно располагаются по краю или по периферии микросхемы. Они могут обрабатывать сигнал выводов микросхемы и после обработки выводить сигнал микросхемы на вывод.

RDL может облегчить перераспределение соединений ввода/вывода от чипа к корпусу. RDL соединяет контактные площадки на чипе с выводами или шариками корпуса, что упрощает сборку и улучшает производительность ИС.

Это, естественно, удобно для процесса соединения проволокой, но несколько затруднительно для флип-чипов. Поэтому RDL стал ключом к этому моменту. Он наносит металлический слой и соответствующий диэлектрический слой на поверхность чипа, формируя металлическую проволоку и перепроектируя порты IO в новую, более просторную область, формируя макет поверхностного массива.

Сигналы маршрута и питание

Кроме того, RDL также обеспечивает средства для маршрутизации сигналов и питания внутри ИС. Использование RDL становится все более важным, поскольку ИС становятся все более сложными и требуют большего количества соединений ввода-вывода. Они используются в широком спектре приложений, таких как микропроцессоры, микросхемы памяти и датчики.

Преимущества уровня перераспределения

Технология RDL предлагает ряд преимуществ для разработчиков, стремящихся создать высокопроизводительные, компактные и экономичные электронные устройства. Некоторые из преимуществ использования технологии RDL в корпусах интегральных схем:

Уменьшенная площадь основания

Технология RDL позволяет интегрировать несколько кристаллов в один корпус, тем самым уменьшая общий размер устройства. Это дает возможность разработчикам создавать более компактные электронные устройства, что крайне важно для таких приложений, как смартфоны, носимые устройства и устройства Интернета вещей.

Улучшенные электрические характеристики

Технология RDL позволяет разработчику разместить кристалл компактно и эффективно, что сокращает длину межсоединений. Это, в свою очередь, уменьшает задержку сигнала и улучшает электрические характеристики устройства. Технология RDL также снижает паразитную емкость и индуктивность, что улучшает целостность сигнала устройства.

Снижение затрат

Технология RDL устраняет необходимость в дорогостоящих и трудоемких процессах соединения проводов и флип-чип-соединения. Технология RDL также сокращает количество компонентов, необходимых для устройства, что еще больше снижает его стоимость. Технология RDL является экономичным решением для создания высокопроизводительных интегральных схем, требующих небольшого форм-фактора.

Типы технологий перераспределительного уровня

Существует два типа технологии перераспределительного слоя (RDL): fan-in и fan-out. Технология fan-in RDL используется для упаковки одного кристалла, а технология fan-out RDL — для упаковки нескольких кристаллов.

Технология Fan-in RDL

Технология fan-in RDL используется для упаковки одного кристалла. Технология fan-in RDL также известна как упаковка на уровне пластины (WLP), которая представляет собой процесс создания упаковки непосредственно на пластине. Технология fan-in RDL является экономичным решением для создания небольших и тонких упаковок.

Технология fan-in RDL подходит для таких применений, как датчики, устройства MEMS, устройства RF, микропроцессоры и устройства памяти.

Технология Fan-out RDL

Технология Fan-Out RDL используется для упаковки нескольких кристаллов. Технология Fan-Out RDL также известна как Fan-Out на уровне пластин (WLFO) и представляет собой процесс создания упаковки на восстановленной пластине. Технология Fan-Out RDL является экономичным решением для создания высокопроизводительных упаковок с небольшим форм-фактором.

Технология fan-out RDL подходит для таких применений, как графические процессоры, системы на кристалле (SoC), устройства памяти, силовые устройства и светодиодные устройства.

Процесс перераспределения

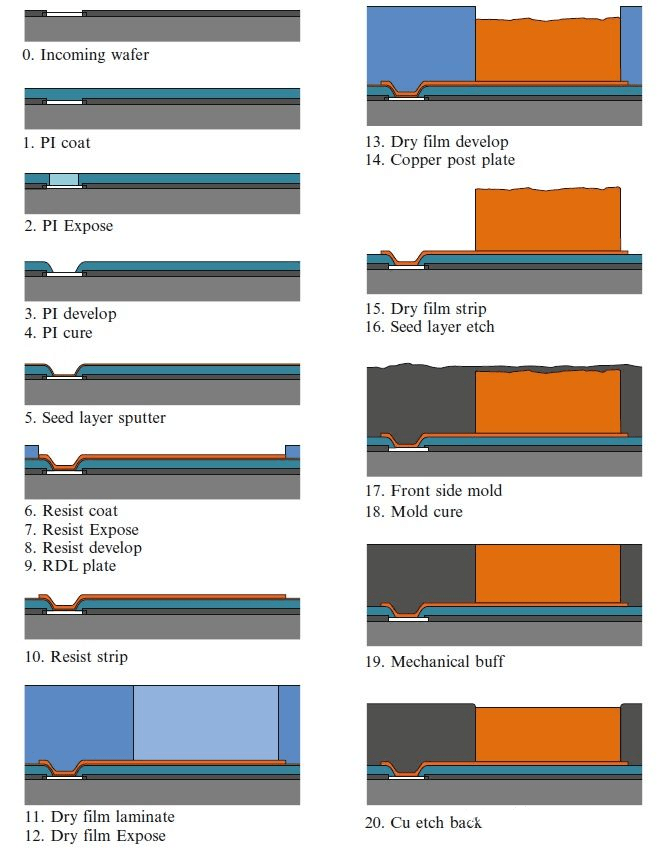

Технология RDL представляет собой сложный процесс, включающий в себя множество этапов, таких как осаждение диэлектрика, осаждение металла, формирование рисунка и травление. Ниже приведены технологические процессы для Fan-in RDL и Fan-out RDL.

Процесс Fan-in RDL

Процесс Fan-in RDL используется в производстве передовых упаковочных решений, таких как упаковка на уровне кристалла (WLCSP) и система в корпусе (SiP). Он позволяет достичь более высокого уровня интеграции, уменьшить размеры и улучшить характеристики полупроводниковых устройств. Процесс включает в себя несколько этапов, описанных ниже:

Процесс начинается с поступления пластины, которая затем покрывается PI (фоторезистивным изолятором) на этапе 1. Затем следует экспонирование PI на этапе 2, проявление PI на этапе 3 и отверждение PI на этапе 4.

На этапе 5 на пластину напыляется затравочный слой, который затем покрывается фоторезистом на этапе 6. Затем фоторезист экспонируется на этапе 7, проявляется на этапе 8, а RDL наносится на этапе 9.

После этого фоторезист удаляется на этапе 10, а на этапе 11 на пластину наносится сухая пленка. Затем сухая пленка подвергается экспонированию на этапе 12 и проявлению на этапе 13. Далее на этапе 14 на пластину наносятся медные столбики, а на этапе 15 удаляется сухая пленка.

На этапе 16 вытравливается затравочный слой, а на этапе 17 создается передняя форма. Затем форма отвердевает на этапе 18, а пластина механически полируется на этапе 19. Наконец, на этапе 20 избыток меди вытравливается, завершая процесс Fan-in RDL.

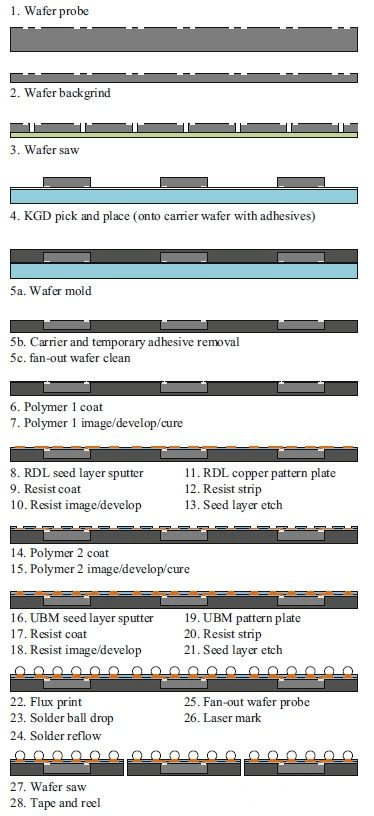

Процесс Fan-out RDL

Подобно процессу Fan-in RDL, процесс Fan-out RDL также является способом создания более компактных и высокопроизводительных микросхем с большим количеством соединений. Ниже приведены этапы производства:

1. Проверка пластин: это первоначальное тестирование пластин, чтобы убедиться, что они соответствуют требуемым спецификациям, прежде чем переходить к последующим этапам обработки.

2. Заднее шлифование пластины: задняя сторона пластины шлифуется до заданной толщины, чтобы уменьшить толщину корпуса.

3. Резка пластин: пластина разрезается на отдельные кристаллы.

4. Отбор и размещение KGD (известных исправных кристаллов): исправные кристаллы отбираются и переносятся на несущую пластину с помощью клея.

5a. Формование пластины: пластина с кристаллами, прикрепленными к несущей пластине, формуется с помощью диэлектрического материала для образования веерообразной структуры.

5b. Удаление носителя и временного клея: Несущая пластина удаляется с веерной пластины, а также удаляется любой временный клей, использованный в процессе.

5c. Очистка фанатной пластины: фанатная пластина очищается для удаления оставшихся частиц или примесей.

6. Покрытие полимером 1: на поверхность веерной пластины наносится слой полимера, который служит диэлектрическим слоем.

7. Полимер 1: изображение/проявление/отверждение: на полимерный слой наносится рисунок с помощью фотолитографии для создания желаемой формы и размера структуры RDL.

8. Распыление затравочного слоя RDL: тонкий слой меди или другого проводящего материала наносится на полимерный слой с помощью распыления.

9. Покрытие фоторезистом: на затравочный слой наносится слой фоторезиста.

10. Изображение/проявление фоторезиста: слой фоторезиста структурируется с помощью фотолитографии для создания желаемой формы и размера структуры RDL.

11. Пластина с медным рисунком RDL: на открытые участки затравочного слоя наносится медь с помощью гальваники, создавая желаемый рисунок RDL.

12. Снятие резиста: оставшийся резист удаляется, оставляя только медный рисунок RDL.

13. Травление затравочного слоя: ненужная часть затравочного слоя удаляется с помощью травления.

14. Покрытие полимером 2: на структуру RDL наносится еще один слой полимера, который служит диэлектрическим слоем.

15. Полимер 2: изображение/проявление/отверждение: на полимерный слой наносится рисунок с помощью фотолитографии для создания желаемой формы и размера структуры UBM.

16. Распыление затравочного слоя UBM: тонкий слой меди или другого проводящего материала наносится на полимерный слой с помощью распыления.

17. Покрытие фоторезистом: на затравочный слой наносится слой фоторезиста.

18. Изображение/проявление фоторезиста: слой фоторезиста структурируется с помощью фотолитографии для создания желаемой формы и размера структуры UBM.

19. Пластина с рисунком UBM: на открытые участки затравочного слоя наносится медь с помощью гальваники, создавая желаемый рисунок UBM.

20. Снятие резиста: оставшийся резист удаляется, оставляя только медный узор UBM.

21. Травление затравочного слоя: ненужная часть затравочного слоя удаляется с помощью травления.

22. Печать флюса: на контактные площадки UBM наносится флюс.

23. Нанесение шариков припоя: шарики припоя помещаются на контактные площадки UBM.

24. Переплавка припоя: шарики припоя нагреваются до плавления и образуют соединения между контактными площадками UBM и внешними выводами или выпуклостями.

25. Проверка вентиляторной пластины: Упакованная ИС тестируется для обеспечения соответствия требуемым спецификациям.

26. Лазерная маркировка: на поверхность IC с помощью лазера наносится уникальный идентификатор или штрих-код.

27. Резка пластин: пластина с разветвлением разрезается на отдельные корпуса.

28. Лента и катушка: отдельные упакованные ИС монтируются на катушку для удобства обращения и транспортировки.

Применение RDL в передовых упаковочных технологиях

В передовых технологиях упаковки, таких как фанат-ин на уровне пластин (FIWLP) и фанат-аут на уровне пластин (FOWLP), RDL является наиболее важной технологией. Именно благодаря развитию этой технологии упаковочные заводы смогли конкурировать с фабриками по производству пластин в области технологий фанат-аут упаковки. С помощью RDL IOPad может быть преобразован в различные типы упаковок на уровне пластин в FIWLP или FOWLP. В FIWLP все выступы вырастают на кристалле, и соединение между кристаллом и контактной площадкой в основном зависит от металлической линии RDL. После упаковки IC имеет почти такой же размер, как и площадь кристалла. В FOWLP выступы могут вырастать за пределами кристалла, и IC после упаковки больше, чем площадь кристалла (в 1,2 раза).

В частности, в передовой упаковке 2.5D, помимо TSV на кремниевой подложке, RDL также незаменим. На примере InFO от TSMC, представителя передовой упаковки 2.5D, InFO использует один или несколько голых кристаллов на носителе, которые затем встраиваются в восстановленную пластину из формовочной массы. Затем на пластине изготавливаются соединительные элементы RDL и диэлектрические слои, что представляет собой технологический процесс «chip first» (сначала чип). Однокристальная технология InFO обеспечивает высокое количество выступов, а линии RDL проходят от области чипа наружу, образуя топологию «fan-out» (веерная).

Какую технологию перераспределения слоев следует использовать?

Как мы уже упоминали ранее, существует две технологии RDL: Fan-in RDL и Fan-out RDL. Так как же выбрать подходящую технологию для создания высокопроизводительных, компактных и экономичных электронных устройств? Это зависит от нескольких факторов, таких как тип применения, количество кристаллов и требования к производительности.

Применение

Технология fan-in RDL подходит для таких применений, как датчики, устройства MEMS и устройства RF. Технология fan-out RDL подходит для таких применений, как графические процессоры, системы на кристалле (SoC) и устройства памяти.

Количество матриц

Технология RDL с вентилятором подходит для упаковки одного кристалла, тогда как технология RDL с выходом подходит для упаковки нескольких кристаллов.

Требования к производительности

Технология fan-in RDL подходит для создания небольших и тонких корпусов, тогда как технология fan-out RDL подходит для создания высокопроизводительных корпусов с небольшим форм-фактором.

Сравнение RDL с другими технологиями упаковки интегральных схем

В связи с различиями в технологическом процессе существует несколько технологий упаковки интегральных схем. Более подробную информацию об их различиях можно найти в таблице ниже:

| IC Packaging | Description | Advantages | Disadvantages | Applications |

|---|---|---|---|---|

| Wire Bonding | Connecting the IC to the PCB using wires | Low cost, flexible, proven technology | Limited performance, not suitable for high-frequency and high-power applications | Consumer electronics, automotive, medical devices |

| Flip-Chip Bonding | Chips are bonded face-down to the substrate, Connecting the IC to the PCB using solder bumps | High performance, high-density, low inductance | Expensive, requires precise alignment and underfilling | High-speed data communication, high-power applications, microprocessors |

| Through-Silicon Via (TSV) | Creating vertical interconnects through the silicon substrate | Shorter interconnect lengths, higher performance, smaller form factor | Complex and expensive manufacturing process, thermal and mechanical stress issues | Memory devices, image sensors, 3D ICs |

| Chip-scale package (CSP) | Replacing the lead frame with a substrate | Small form factor, high density, low cost | Limited I/O, susceptibility to mechanical and thermal stress | Mobile devices, wearable technology |

| Integrated Fan-out (InFO) | Integrated package of multiple chips and the soldering point of the pin is outside of the chip | High density, small form factor, low power consumption | Complex manufacturing process, high cost | Mobile devices, IoT, wearable technology |

| High Bandwidth Memory (HBM) | 3D stacking technology | High bandwidth, low power consumption | Expensive, limited scalability | High-performance computing, graphics processing |

| Chip on Wafer on Substrate (CoWoS) | Integrate chip and silicon wafer (substrate) together | High bandwidth, low power consumption, heterogeneous integration | Complex manufacturing process, high cost | High-performance computing, graphics processing |

| Redistribution Layer (RDL) | Creating a patterned metal layer on top of the dielectric layer | High density, fine pitch, low profile | Limited power handling capability, susceptibility to mechanical and thermal stress | Mobile devices, consumer electronics |

| Bump Technology | Depositing small metal bumps on the chip | Low cost, simple manufacturing process, flexible design | Limited performance, not suitable for high-speed and high-power applications | Consumer electronics, automotive, medical devices |

Компании, предлагающие технологические решения для уровня перераспределения

Существует несколько компаний, предлагающих технологические решения в области перераспределительного уровня (RDL), такие как:

Группа ASE

ASE Group — глобальный поставщик услуг по производству полупроводников. ASE Group предлагает широкий спектр технологических решений RDL для различных областей применения, таких как память, микропроцессоры и графические процессоры.

Amkor Technology

Amkor Technology — глобальный поставщик услуг по упаковке и тестированию полупроводников. Amkor Technology предлагает широкий спектр технологических решений RDL для различных применений, таких как датчики, устройства MEMS и силовые устройства.

Тайваньская компания по производству полупроводников

TSMC — это глобальный производитель полупроводников, предлагающий широкий спектр технологических решений RDL для различных применений, таких как системные микросхемы (SoC), запоминающие устройства и силовые устройства.

Заключение

Технология перераспределительного слоя (RDL) — это революционное решение в области упаковки, которое изменило подход к упаковке интегральных схем (ИС). Она позволяет создавать больше соединений на одном чипе, тем самым уменьшая общий размер устройства. Поэтому она используется в различных приложениях, таких как смартфоны, носимые устройства и устройства Интернета вещей. Будущее технологии RDL в упаковке ИС многообещающе, и ожидается, что в ближайшие годы она окажет значительное влияние на электронную промышленность.