Обзор MSP430F169

Микроконтроллер MSP430F169 входит в семейство MSP430 компании Texas Instruments. Он состоит из нескольких устройств, которые имеют различные наборы периферийных устройств, предназначенных для различных применений. Архитектура этих микроконтроллеров в сочетании с пятью режимами низкого энергопотребления была тщательно настроена для оптимизации продолжительности работы от батареи в портативных измерительных приложениях. Кроме того, цифровой генератор (DCO) обеспечивает быстрое пробуждение из режимов низкого энергопотребления в активный режим за менее чем 6 мкс.

Эти микроконтроллеры находят типичное применение в сенсорных системах, промышленных системах управления, портативных измерительных приборах и других подобных областях.

Особенности

- Низкое энергопотребление;

- Пять режимов энергосбережения;

- Трехканальный внутренний DMA;

- Последовательное встроенное программирование;

- Программируемая защита кода с помощью предохранителя безопасности;

- С детектором пониженного напряжения и загрузчиком bootstrap;

- Монитор напряжения питания с программируемым уровнем обнаружения.

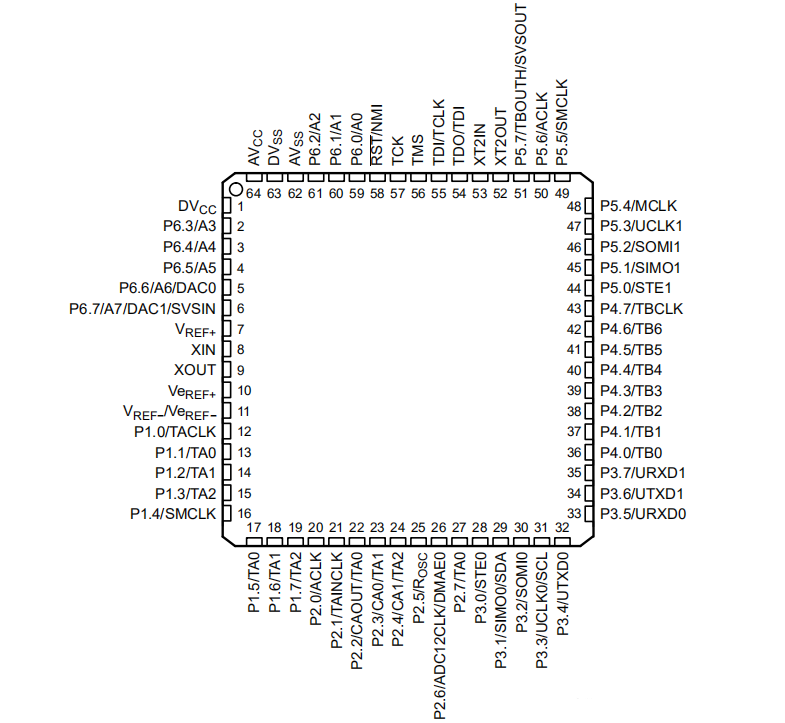

Конфигурация выводов

MSP430F169 доступен в 64-контактном и 100-контактном исполнении с разными конфигурациями контактов.

В 64-контактной версии некоторые ключевые контакты включают:

| Pin Types | Pin Name | Description |

|---|---|---|

| Power Supply Pins | VCC | Positive supply voltage input |

| GND | Ground | |

| RST/NMI | Reset input and non-maskable interrupt | |

| TEST | Test mode input/output | |

| AVSS/AVCC | Ground and voltage reference for ADC | |

| DVSS/DVCC | Ground and voltage reference for digital circuitry | |

| Input/Output Pins | P1.x-P8.x | General-purpose I/O pins |

| Communication Pins | UCA0CLK | USART module A0 clock input/output |

| UCA0STE | USART module A0 STE input/output | |

| UCA0TXD | USART module A0 transmit data output | |

| UCA0RXD | USART module A0 receive data input | |

| UCB0CLK | SPI module B0 clock input/output | |

| UCB0STE | SPI module B0 STE input/output | |

| UCB0SIMO | SPI module B0 transmit data output | |

| UCB0SOMI | SPI module B0 receive data input | |

| UCB0SDA | I2C module B0 data input/output | |

| UCB0SCL | I2C module B0 clock input/output | |

| Timers and Counters | TA0CCR0-TA0CCR6 | Timer A0 capture/compare register 0-6 |

| Timer A0 control register | ||

| TB0CCR0-TB0CCR2 | Timer B0 capture/compare register 0-2 | |

| Timer B0 control register | ||

| Analog Pins | ADC12CLK | ADC12 clock input |

| ADC12MEM0-ADC12MEM15 | ADC12 memory register 0-15 | |

| AVREF+ | Positive reference voltage input for ADC | |

| AVREF- | Negative reference voltage input for ADC | |

| JTAG Pins | TCLK | Test clock input/output |

| TDI | Test data input | |

| TDO | Test data output | |

| Special Function Pins | ACLK | 32.768 kHz crystal oscillator input |

| SMCLK | System master clock output | |

| RTCCLK | Real-time clock input/output |

Спецификация

| Specification | Value |

|---|---|

| CPU | 16-bit RISC |

| Frequency | 8 MHz |

| Flash memory | 16 KB |

| RAM | 2 KB |

| Standby power | 1.1 µA |

| Active power | 330 µA at 1 MHz, 2.2 V |

| Wake-up time | in less than 6 µs |

| Instruction cycle time | 125 ns |

| Supply voltage | 1.8 V to 3.6 V |

| A/D converter | 12-bit |

| Timer/Counter | 2 * 16-bit |

| Operating Temp | -40 to 85 ℃ |

| DMA | 3 |

| I2C | 1 |

| SPI | 2 |

| Peripherals | timers, serial ports, I2C |

| Package | 64-pin QFP or 64-pin QFN |

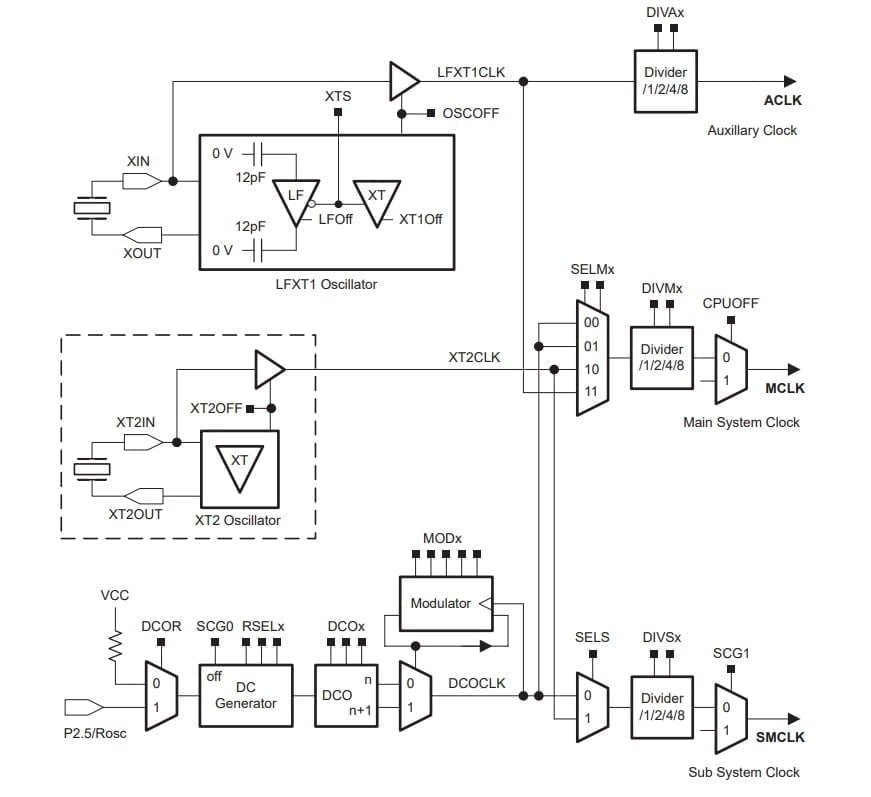

Часовая система MSP430F169

Система тактовой частоты очень важна для однокристального микрокомпьютера. Причина, по которой однокристальный микрокомпьютер MSP430F169 имеет такое низкое энергопотребление, заключается в том, что он оснащен мощной системой тактовой частоты!

Три источника тактового сигнала

1. Низкочастотный LFXT1CLK (32,768 кГц)

Стандартный кварцевый генератор, генератор или внешний источник тактовой частоты могут использоваться для ввода 4 МГц ~ 32 МГц. XT1CLK может использоваться в качестве опорного тактового генератора для внутреннего модуля FLL.

Низкочастотный кварцевый генератор (32,768 кГц) подключается напрямую к однокристальному микрокомпьютеру через выводы XIN и XOUT, и никаких других внешних устройств не требуется (внутри имеется емкость нагрузки 12 пФ). В это время генератор LFXT1 работает в низкочастотном режиме (XTS=0).

Если микроконтроллер подключен к высокоскоростному генератору или резонатору, 0SCOFF=0 может заставить генератор LFXT1 работать в высокочастотном режиме (XTS=1). В это время высокоскоростной кварцевый генератор или резонатор подключается через выводы XIN и XOUT, и требуется внешний конденсатор. Размер конденсатора выбирается в соответствии с характеристиками кварцевого генератора или резонатора.

Если сигнал LFXT1CLK не используется в качестве сигнала SMCLK или MCIK, программное обеспечение может установить OSCOFF=1, чтобы отключить работу LFXT1, тем самым снизив энергопотребление микроконтроллера.

BCSCTL1:

XTS(BIT6)——выбор режима высокой/низкой скорости LFXT1. 0: LFXT1 работает в режиме низкоскоростного кварцевого генератора (по умолчанию); 1: LFXT1 работает в режиме высокоскоростного кварцевого генератора.

2. Высокочастотный XT2CLK (8 МГц)

Для ввода сигнала частотой 4 МГц~32 МГц можно использовать стандартный кварцевый генератор, генератор или внешний источник тактового сигнала.

Генератор XT2 генерирует тактовый сигнал XT2CLK, и его рабочие характеристики аналогичны характеристикам генератора LFXT1 при работе в высокочастотном режиме. Если XT2CLK не используется в качестве тактового сигнала MCLK и SMCLK, генератор XT2 можно отключить с помощью управляющего бита XT2OFF.

BCSCTL1:

XT2OFF (BIT7) — управление высокоскоростным кварцевым генератором XT2. 0: высокоскоростной кварцевый генератор XT2 включен; 1: высокоскоростной кварцевый генератор XT2 выключен.

3. Внутренний генератор DCOCLK (1 МГц)

Стабилизируется модулем FLL.

При выходе из строя генератора DCO автоматически выбирается в качестве источника тактовой частоты для MCLK.

Частота генератора DCO может быть отрегулирована с помощью программного обеспечения, устанавливающего биты DCOx. MODx и RSEL.x. Когда сигнал DCOCLK не используется в качестве тактового сигнала SMCLK и MCLK, генератор DC может быть отключен с помощью управляющего бита SCGO.

После сигнала PUC DCOCLK автоматически выбирается в качестве тактового сигнала MCLK, а источник тактового сигнала MCLK может быть дополнительно установлен на LFXT1 или XT2 в соответствии с требованиями. Последовательность настройки следующая:

- Пусть OSCOFF=1;

- Пусть OFIFG=0;

- Задержка и ожидание не менее 50 пс;

- Снова проверьте OFIFG, если OFIFG=1, повторяйте шаги (3) и (4) до тех пор, пока OFIFG=0.

DCOCTL:

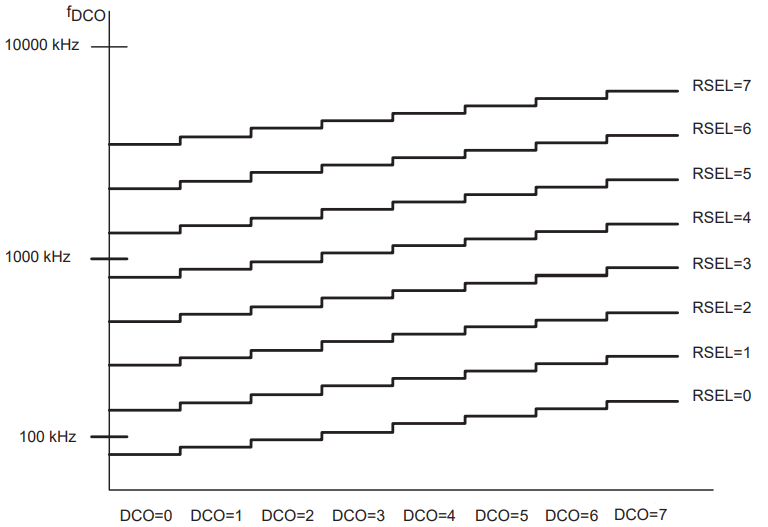

DCOx (BIT7, BIT6, BIT5)——Выбор частоты DCO, можно выбрать 8 видов частот, а частоту DCOCLK можно регулировать по частям. Выбор частоты основан на частотном диапазоне, выбранном RSELx. Связь между DCOx, RSELx и внутренним тактовым генератором следующая:

MODx (BIT4, BIT3, BIT2, BIT1, BIT0) — настройка модулятора ЦАП. Регулятор переключает две частоты, выбранные DCOx и DCOx+1, для точной настройки выходной частоты DCO. Если константа DCOx равна 7, это означает, что выбрана самая высокая частота. В это время MODx недействителен и не может использоваться для настройки частоты.

BCSCTL1:

RSELx (BIT2, BIT1, BIT0) — выбор частотного диапазона генератора DCO, эти 3 бита управляют внутренним сопротивлением для определения номинальной частоты. 0: выбор самой низкой номинальной частоты… 7: выбор самой высокой номинальной частоты.

BCSCTL2:

DCOR(BIT0)——Выбор сопротивления генератора DCO. 0: внутреннее сопротивление; 1: внешнее сопротивление.

Три источника тактовой частоты

1. Вспомогательный тактовый генератор ACLK

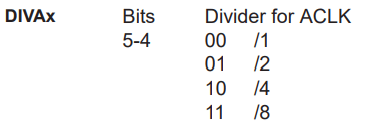

ACLK получается после деления LFXT1CLK на 1, 2, 4 и 8. Он может использоваться в качестве тактового сигнала каждого периферийного модуля и обычно используется для низкоскоростных периферийных устройств.

BCSCTL1:

DIVAx (BIT5, BIT4)——выбор частотного деления ACLK, соотношение выбора частотного деления следующее:

Определение макроса: DIVA_0 (1 частотное разделение/без частотного разделения), DIVA_1 (2 частотного разделения), DIVA_2 (4 частотного разделения), DIVA_3 (8 частотного разделения)

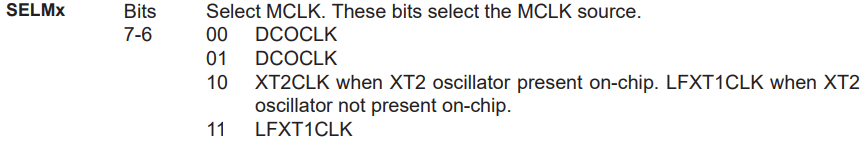

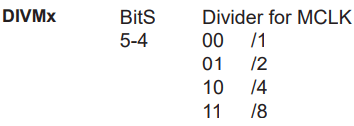

2. Главный тактовый генератор системы MCLK

MCLK может быть получен из LFXT1CLK, XT2CLK и DCOCLK после деления частоты на 1, 2, 4 и 8. Он часто используется для работы ЦП, выполнения программ и других модулей, которые используют высокоскоростные тактовые генераторы.

BCSCTL2:

SELMx (BIT7, BIT6) — выбор источника тактовой частоты MCLK, соотношение выбора тактовой частоты следующее:

Определение макрокоманды: SELM_0 (по умолчанию DCOCLK), SELM_1 (DCOCLK), SELM_2 (XT2CLK), SELM_3 (LFXT1CLK)

DIVMx (BIT5, BIT4) — выбор деления частоты MCLK, соотношение выбора деления частоты следующее:

Определение макрокоманды: DIVM_0 (1 разделение частоты/без разделения частоты), DIVM_1 (2 разделения частоты), DIVM_2 (4 разделения частоты), DIVM_3 (8 разделений частоты)

3. Тактовая частота подсистемы SMCLK

SMCLK может быть получен путем деления частоты XT2CLK и DCOCLK на 1, 2, 4 и 8 и часто используется в высокоскоростных периферийных модулях.

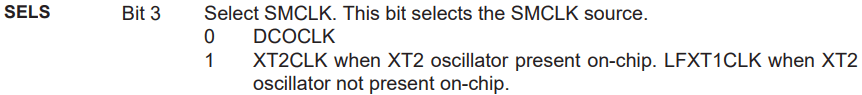

BCSCTL2:

SELSx (BIT3) — выбор источника тактовой частоты MCLK, соотношение выбора тактовой частоты следующее:

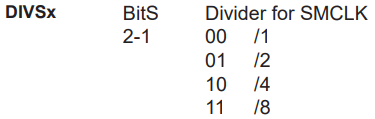

DIVSx (BIT2, BIT1) — выбор частотного деления SMCLK, соотношение выбора частотного деления следующее:

Определение макрокоманды: DIVS_0 (1 деление частоты/без деления частоты), DIVS_1 (2 деления частоты), DIVS_2 (4 деления частоты), DIVS_3 (8 делений частоты)