SWD и JTAG — популярные интерфейсы отладки для микроконтроллеров на базе Cortex-M. Однако эти два интерфейса различаются как по структуре, так и по применению. В этой статье мы расскажем об их контактах, принципе работы, преимуществах и недостатках.

Интерфейс SWD

SWD (Serial Wire Debug) — это протокол, разработанный ARM для программирования и отладки микроконтроллеров. Он основан на архитектуре отладки ARM CoreSight и позволяет читать и записывать регистры микросхем через пакеты данных. SWD — это двухпроводной протокол для доступа к интерфейсам отладки ARM. Он является частью спецификации архитектуры отладочного интерфейса ARM и служит альтернативой JTAG. В случаях, когда макет печатной платы ограничен, а ресурсы выводов ограничены, SWD является хорошим выбором. Многие отладчики на рынке поддерживают отладочные интерфейсы SWD, такие как ST-Link, J-Link, e-Link, GD-Link и другие.

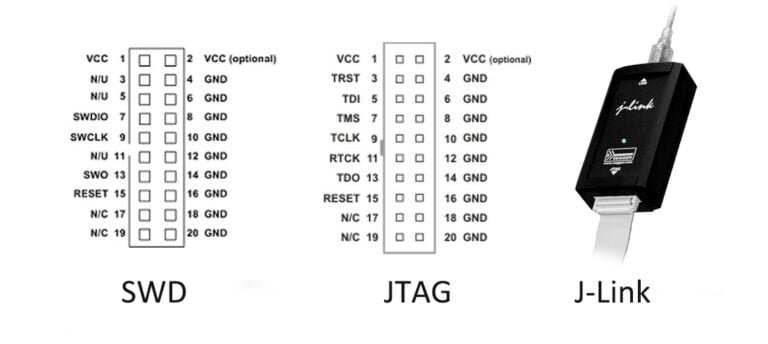

Штифты SWD

SWDIO: вход/выход данных последовательной линии, контакт входа и выхода

последовательных данных SWCLK: тактовый генератор последовательной линии, контакт тактового генератора последовательной линии

SWDIO — это двунаправленный (входной и выходной) контакт для данных, и линия должна быть подтянута на печатной плате (ARM рекомендует 100 К).

Как работает SWD?

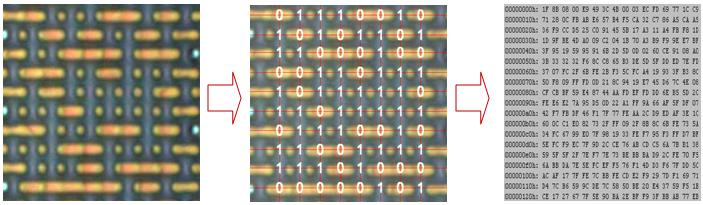

Внешние устройства, такие как отладочные зонды, подключаются к SWDIO/SWCLK для прямого доступа к порту Serial Wire Debug Port (SW-DP). SW-DP может обращаться к одному или нескольким портам доступа (AP), а через AP можно получить доступ к остальным регистрам системы. Важным AP для процессоров серии Cortex M является AHB-AP, который служит ведущим на внутренней шине AHB. Другими словами, AHB-AP может получить доступ к карте памяти внутреннего ядра. Поскольку внутренняя флэш-память, SRAM, отладочные компоненты и периферийные устройства все отображаются в памяти, AHB-AP может управлять всем устройством, включая его программирование. Весь процесс работы SWD является иерархическим, с входом тактовых сигналов от вывода SWCLK и входом/выходом сигналов данных от вывода SWDIO. Изначально отладчик работает на SW-DP, чтобы определить параметры регистров AP, что позволяет манипулировать картой памяти Cortex.

Преимущества SWD

- Уменьшенное количество сигналов

- Надежность при высоких скоростях

- Снижение вероятности сбоев

- Совместимость с JTAG-симуляторами

- Требует меньшего количества контактов для работы

Интерфейс JTAG

JTAG (Joint Test Action Group) изначально использовалась для тестирования микросхем. Эта группа инициировала дискуссии в конце 1980-х годов и в 1990 году официально опубликовала документы с интерпретацией стандартов IEEE. (IEEE — это аббревиатура от Institute of Electrical and Electronics Engineers, международной организации, ответственной за публикацию стандартов, таких как WiFi и Bluetooth). Предложенный ими протокол был задокументирован в стандарте IEEE 1149.1 в 1990 году. С тех пор этот документ подвергался пересмотрам и усовершенствованиям, и на момент написания данной статьи последним стандартом является IEEE 1149.7.

Контакты JTAG

- TDI: вход тестовых данных, последовательный входной контакт.

- TDO: выход тестовых данных, последовательный выходной контакт.

- TCK: Test Clock, тактовый вывод.

- TMS: Test Mode Select, вывод выбора режима (управляющий сигнал).

- TRST: сброс теста, вывод сброса.

Как работает JTAG?

Принцип JTAG заключается в определении порта доступа для тестирования (TAP) внутри устройства. Это позволяет тестировать внутренние узлы с помощью специализированных инструментов тестирования JTAG. Тестирование JTAG позволяет подключать несколько устройств последовательно через интерфейс JTAG, образуя цепочку JTAG для тестирования отдельных устройств. В настоящее время интерфейсы JTAG также широко используются для операций программирования в системе (ISP), таких как программирование устройств FLASH. С точки зрения аппаратной структуры, интерфейс JTAG состоит из двух частей: порта JTAG и контроллера. Устройствами, совместимыми с интерфейсом JTAG, могут быть микропроцессоры (MPU), микроконтроллеры (MCU), PLD, CPLD, FPGA, DSP, ASIC или другие микросхемы, соответствующие спецификациям IEEE 1149.1. Стандарт IEEE 1149.1 требует наличия сдвигового регистра, называемого блоком граничного сканирования (BSU), для каждого контакта микросхемы цифровой интегральной схемы. Он соединяет схему JTAG с основной логической схемой, одновременно изолируя основную логическую схему от контактов микросхемы. Все блоки граничного сканирования микросхемы составляют регистр граничного сканирования (BSR). Схема регистра граничного сканирования активна только во время тестирования JTAG и не влияет на функциональность микросхемы во время нормальной работы.

Протокол JTAG управляет переходом состояния TAP через сигнал TMS. После включения системы контроллер TAP сначала переходит в состояние сброса тестовой логики, а затем последовательно переходит через состояния Run-Test/Idle, Select-DR-Scan, Select-IR-Scan, Capture-IR, Shift-IR, Exit1-IR и Update-IR, прежде чем вернуться в состояние Run-Test/Idle. Во время этого процесса переходы между состояниями управляются сигналом TCK (восходящий фронт), а сигналы TMS используются для выбора состояния TAP. В состоянии Capture-IR в регистр инструкций загружается определенная логическая последовательность; в состоянии Shift-IR в регистр инструкций может быть сдвинута определенная инструкция; а в состоянии Update-IR инструкция, только что введенная в регистр инструкций, используется для обновления регистра инструкций. Наконец, система возвращается в состояние Run-Test/Idle, где инструкция вступает в силу, завершая доступ к инструкции и регистрам. После возврата в состояние Run-Test/Idle на основе содержимого регистра инструкций выбирается необходимый регистр данных и начинается работа с регистрами данных.

Преимущества JTAG

- JTAG не ограничивается чипами ARM; он поддерживается и в других чипах, таких как хорошо известный MSP430.

- JTAG имеет широкий спектр применений для программирования, отладки и производственного тестирования.

- JTAG — это независимая группа, которая развивается вместе с развитием протокола.

Заключение

JTAG и SWD — это два важных интерфейса отладки встроенных систем, каждый из которых имеет свои преимущества и недостатки. Выбор интерфейса зависит от требований проекта, аппаратной поддержки и требований к производительности. Для сложных систем может потребоваться JTAG, чтобы получить больше контроля и функциональности, в то время как SWD может быть более подходящим для систем с ограниченными ресурсами. Учет всех этих факторов поможет вам принять обоснованные решения для более эффективной разработки и отладки встроенных систем.