Что такое интегральная схема?

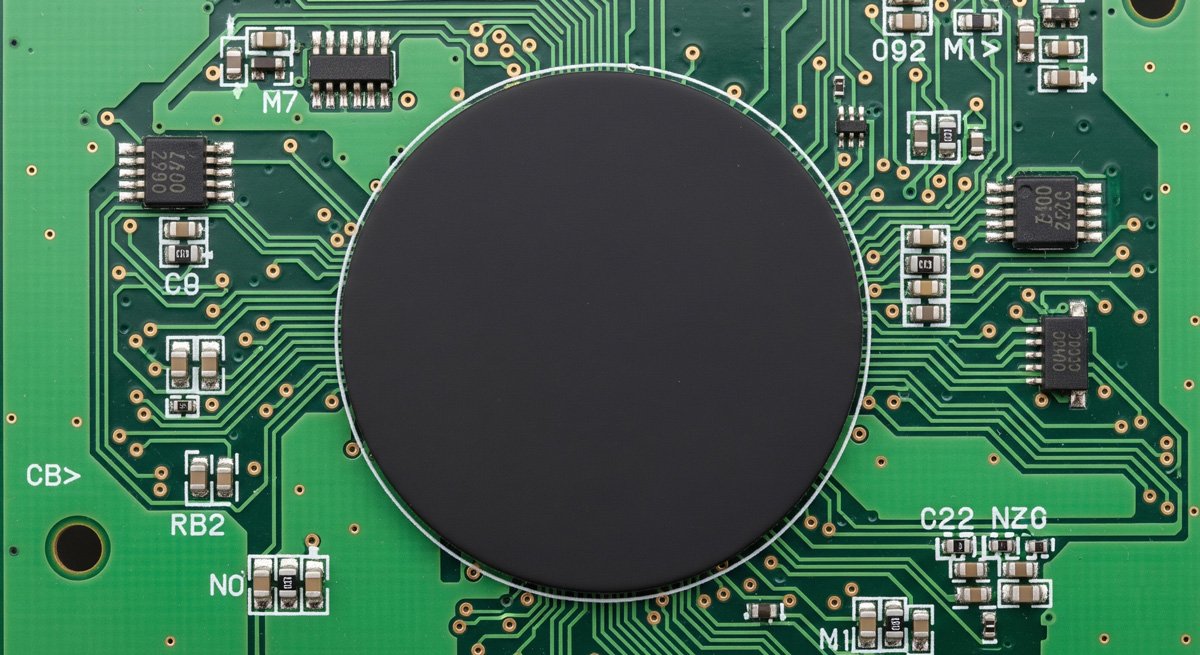

Интегральная схема (ИС) — это электронная схема, построенная на одном полупроводниковом чипе. Это наиболее распространенный тип электронных устройств, используемых в компьютерах, мобильных телефонах и другой электронике. Как правило, IC представляет собой небольшой кусочек кремния размером примерно в одну восьмую дюйма в квадрате, который содержит тысячи или миллионы транзисторов, резисторов и других компонентов печатной платы. Такой тип миниатюрных схем позволяет выполнять различные функции при гораздо меньших размерах и с большей эффективностью, чем если бы компоненты были сконструированы отдельно.

Компоненты интегральной схемы

Интегральные схемы состоят из нескольких компонентов, каждый из которых выполняет определенную функцию. Эти компоненты обычно соединяются между собой с помощью крошечных металлических дорожек, которые используются для передачи электрических сигналов между различными частями схемы. Компоненты обычно очень маленькие, их размеры варьируются от нескольких микрометров до нескольких миллиметров. Это позволяет разместить большое количество компонентов на одном чипе, что обеспечивает более высокую степень сложности и функциональности.

Преимущества интегральных схем

Интегральные схемы — это мощные инструменты, которые позволяют нам повысить сложность и функциональность нашей электроники. Размещая несколько компонентов на одном чипе, мы можем уменьшить количество места, необходимое для устройства. Это, в свою очередь, снижает затраты и повышает эффективность устройства. Интеграция компонентов также помогает уменьшить электромагнитные помехи, позволяя нашей электронике работать более надежно. Интегральные схемы являются основой современной электроники и незаменимы в нашей повседневной жизни.

Применение интегральных схем

Интегральные схемы являются основой большинства современных электронных устройств. Они используются в компьютерах, мобильных телефонах, телевизорах, радиоприемниках и многих других электронных устройствах. Их также можно найти в бытовой технике, такой как стиральные машины, микроволновые печи и посудомоечные машины. Кроме того, они все чаще используются в медицинских устройствах, промышленном оборудовании и автомобильных системах.

Обзор процесса проектирования интегральных схем

Проектирование интегральных схем — это сложный процесс разработки электронных схем. Он включает в себя несколько этапов, в том числе проектирование передней части, проектирование задней части и окончательную сборку. Процесс носит высоко итеративный характер и требует тесного сотрудничества между проектировщиком и инженерами, чтобы обеспечить соответствие проекта всем необходимым спецификациям. На каждом этапе процесса создаются прототипы для тестирования и проверки того, что проекты работают так, как ожидалось.

Дизайн интерфейса

Фронтальный дизайн интегральных схем — это процесс проектирования основных компонентов интегральной схемы (ИС), таких как транзисторы, резисторы и конденсаторы. Это осуществляется с помощью различных инструментов, таких как программное обеспечение для построения схем, логического синтеза и компоновки. Цель фронтального дизайна — создать ИС, отвечающую требуемым спецификациям.

Технические характеристики ИС

Спецификации IC в проектировании IC определяют основные компоненты и атрибуты, которые должны быть включены в схему. Это основа, на которой будет построен весь процесс проектирования. Спецификации должны отражать все требования, необходимые для успешного проектирования IC. Кроме того, они должны быть способны адаптироваться к меняющимся потребностям и технологиям отрасли. Правильные спецификации IC имеют решающее значение для эффективного и результативного процесса проектирования, поэтому важно обеспечить их надлежащее установление для достижения успеха.

Детальный проект

Fabless разрабатывает проектное решение и конкретную архитектуру реализации в соответствии с требованиями спецификации, выдвинутыми заказчиком, и распределяет функции модулей.

Кодирование HDL

HDL — это мощный язык описания аппаратного обеспечения для проектирования интегральных схем. Он обеспечивает эффективный способ описания сложных конструкций и позволяет на раннем этапе проверить функциональность конструкции. HDL широко используется в промышленности, что делает его незаменимой технологией для современных разработчиков интегральных схем. Гибкость и масштабируемость HDL делают его выгодным для использования в различных приложениях и на нескольких платформах. Это позволяет разработчикам создавать эффективные и комплексные проекты интегральных схем, которые хорошо подходят для их конкретных нужд. HDL является важным инструментом для успеха любого проекта по разработке интегральных схем, и его использование должно быть тщательно рассмотрено любым разработчиком, стремящимся создать успешную интегральную схему.

Проверка моделирования

Верификация моделирования является важным этапом в процессе проектирования интегральных схем. Она помогает проектировщикам выявлять потенциальные ошибки и недостатки конструкции на этапе разработки. Этот процесс включает в себя проведение моделирования и тестирования проектов интегральных схем для обеспечения их соответствия требуемым спецификациям и стандартам. Верификация моделирования полезна для обнаружения ошибок, устранения проблем проектирования и оптимизации производительности проекта интегральной схемы. Кроме того, она позволяет проектировщикам лучше понять, как их проекты интегральных схем будут вести себя в реальных условиях. Таким образом, верификация моделирования играет важную роль в обеспечении надежности проектов интегральных схем перед их внедрением в производство.

(Инструменты верификации симуляции: VCS от Synopsys и NC-Verilog от Cadence.)

Логический синтез——Design Compiler

Проверка моделирования прошла успешно, и выполнен логический синтез. Результатом логического синтеза является перевод разработанного и реализованного кода HDL в список цепей на уровне логических элементов. Для синтеза необходимо установить ограничения, которые представляют собой стандарты, которым должна соответствовать синтезированная схема с точки зрения целевых параметров, таких как площадь и синхронизация. Логический синтез должен основываться на конкретной комплексной библиотеке. В разных библиотеках площадь базовой стандартной ячейки (стандартной ячейки) схемы вентилей и параметры синхронизации различаются.

Поэтому выбранные комплексные библиотеки различаются, а синтезированные схемы различаются по времени и площади. Вообще говоря, после завершения синтеза необходимо повторно провести проверку моделированием (это также называется пост-моделированием, а предыдущее называется пре-моделированием).

(Инструмент логического синтеза: Design Compiler от Synopsys)

STA

STA — это статический анализ временных характеристик, который также относится к категории верификации. Он в основном проверяет схему с точки зрения временных характеристик и проверяет, нет ли в схеме нарушений времени установления и времени удержания (нарушений). Это базовые знания о цифровых схемах. Когда эти два нарушения временных характеристик происходят в регистре, нет возможности правильно отобрать данные и вывести их, поэтому обязательно возникнут проблемы с функционированием цифровых микросхем, основанных на регистрах.

(Инструмент STA: Prime Time от Synopsys.)

Формальная верификация

Это также категория верификации, которая заключается в проверке синтезированного списка цепей из функции (STA — это синхронизация). Наиболее часто используемым методом является метод проверки эквивалентности. Используя HDL-проект после функциональной верификации в качестве эталона, сравните функции списка цепей после синтеза, чтобы увидеть, являются ли они функционально эквивалентными. Это делается для того, чтобы убедиться, что функция схемы, описанная исходным HDL, не была изменена в процессе логического синтеза.

(Инструмент формальной верификации: Synopsys Formality.)

Дизайн бэкэнда

Бэкэнд-проектирование интегральных схем — это этап процесса проектирования, на котором создается физическая компоновка схемы. Он включает в себя проектирование металлических масок, трассировку металлических слоев и другие физические аспекты схемы. Бэкэнд-проектирование часто является самой длительной и детальной частью процесса проектирования и имеет решающее значение для обеспечения правильной работы схемы. Оно также может включать в себя передовые технологии, такие как использование слоев перераспределения (RDL) для оптимизации подключения.

Направленная передача силы

Проектирование для тестирования, проектирование для тестируемости. Чипы часто имеют встроенные тестовые схемы, и цель DFT состоит в том, чтобы учитывать будущие тесты при проектировании. Обычный подход к DFT заключается во вставке цепей сканирования в проект, чтобы превратить несканируемые блоки (такие как регистры) в сканируемые блоки. Что касается DFT, то в некоторых книгах есть подробные введения, поэтому легче понять его, сравнивая с изображениями.

(Инструмент DFT: DFT Compiler от Synopsys)

План этажа

Планировка заключается в размещении макроядерного модуля чипа и общем определении размещения различных функциональных схем, таких как IP-модули, ОЗУ, выводы ввода-вывода и т. д. Планировка может напрямую повлиять на окончательную площадь чипа.

(Инструменты планировки: Astro от Synopsys)

CTS

Синтез тактового дерева, синтез тактового дерева, проще говоря, это подключение тактового генератора. Из-за глобальной функции тактового сигнала в цифровом чипе, его распределение должно быть симметрично подключено к каждому регистровому блоку, чтобы при достижении тактового генератора каждого регистра из одного и того же источника тактового сигнала разница в задержке тактового сигнала была минимальной. Это также является причиной, по которой тактовые сигналы необходимо прокладывать отдельно.

(Инструмент CTS: Physical Compiler от Synopsys.)

Планировка и маршрут

Маршрут здесь представляет собой обычную сигнальную проводку, включая проводку между различными стандартными блоками (базовые логические схемы). Например, процесс 0,13 мкм, о котором мы обычно слышим, или процесс 90 нм, на самом деле является минимальной шириной, которую может достичь металлическая проводка, и с микроскопической точки зрения это длина канала MOS-трубки.

(Инструмент для трассировки: Astro от Synopsys)

Извлечение паразитов

Извлечение паразитных элементов из проекта интегральной схемы является важным процессом в разработке интегральных схем. Это процесс извлечения паразитных элементов, таких как емкость, индуктивность и сопротивление, из физической схемы. Этот процесс имеет решающее значение для обеспечения соответствия проекта интегральной схемы требованиям производительности, предъявляемым пользователем. Точность извлечения паразитных элементов также играет ключевую роль в обеспечении ожидаемого поведения проекта. В целом, извлечение паразитных элементов из проекта ИС является важным шагом для достижения хорошей рабочей производительности интегральной схемы.

(Инструмент извлечения паразитных элементов: Synopsys Star-RCXT)

Физическая проверка

Физическая верификация макета интегральной схемы является важным этапом в процессе проектирования ИС. Она проводится после разработки схемы и обычно включает в себя верификацию LVS (Layout vs Schematic), DRC (Design Rule Checker) и ERC (Electrical Rule Checker). Проверка LVS подтверждает, что физическая компоновка соответствует схематическому дизайну. DRC проверяет наличие нарушений правил проектирования, установленных процессом изготовления, а ERC проверяет наличие электрических ошибок. Все эти проверки важны для обеспечения правильности дизайна и его готовности к изготовлению. Физическая верификация помогает гарантировать, что дизайн интегральной схемы соответствует желаемым спецификациям и требованиям.

(Инструмент физической проверки: Hercules от Synopsys)

Завершение проверки физической компоновки означает, что весь этап проектирования микросхемы завершен, и далее следует изготовление микросхемы.

Советы и рекомендации по проектированию интегральных схем

— Подробно изучите требования проекта.

— Разбейте проект на блоки и распределите задачи

.- Проанализируйте требования к питанию и выберите подходящие устройства.

— Тщательно разработайте схему,

учитывая правила проектирования.- Проверьте проект с помощью симуляций.

— Отладьте проект и оптимизируйте макет.

— Сгенерируйте GDS и проверьте проект на целевой плате.

—

Использовать методы оценки и оптимизации энергопотребления.- Выбрать правильные компоненты.

— Учитывать ограничения

по времени и энергопотреблению.-

Использовать инструменты автоматизации проектирования.- Выполнить

проверку и отладку проекта.- Использовать преимущества

передовых инструментов проектирования интегральных схем.- Использовать иерархическое проектирование для сложных проектов.

— Учитывать компромиссы между энергопотреблением, площадью и производительностью.

— Проектировать с учетом тестируемости и отлаживаемости.

— Создать полную документацию по проекту.