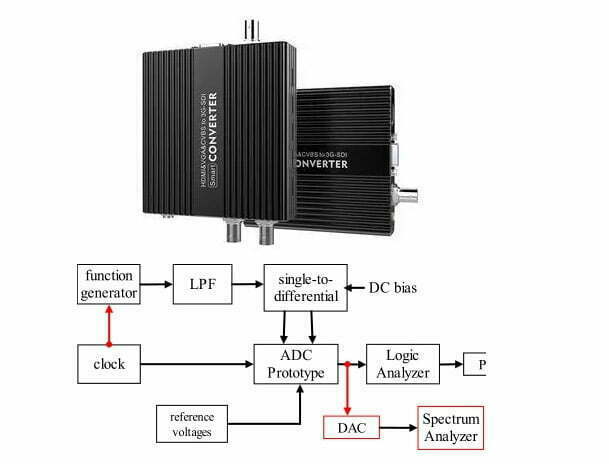

Среди интеллектуальных приборов ключевую роль играют преобразователи ADC и DAC. Мы знаем, что широко используемые в настоящее время микропроцессоры могут обрабатывать только дискретные цифровые сигналы. Без ADC невозможно подать непрерывный аналоговый сигнал из физического мира в микропроцессор. Кроме того, без DAC невозможно вывести аналоговый сигнал из микропроцессора. (нажмите здесь, чтобы узнать больше о цифровом сигнале и аналоговом сигнале)

Аналогово-цифровой преобразователь (АЦП)

Определение ADC

В системе контрольно-измерительных приборов часто возникает необходимость преобразования непрерывно изменяющихся аналоговых величин, таких как температура, давление, расход, скорость, интенсивность света и т. д., в дискретные цифровые величины перед их вводом в компьютер для обработки. Эти аналоговые величины преобразуются датчиками в электрические сигналы (обычно сигналы напряжения) и после усиления усилителями должны пройти определенную обработку, чтобы стать цифровыми величинами. Устройство, преобразующее аналоговые величины в цифровые, обычно называется аналого-цифровым преобразователем (АЦП) или сокращенно А/Ц.

Принцип работы АЦП

В нормальных условиях аналого-цифровое преобразование обычно проходит четыре этапа: выборка, удержание, квантование и кодирование.

Отбор проб и хранение

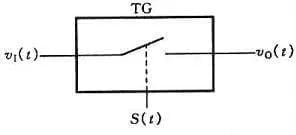

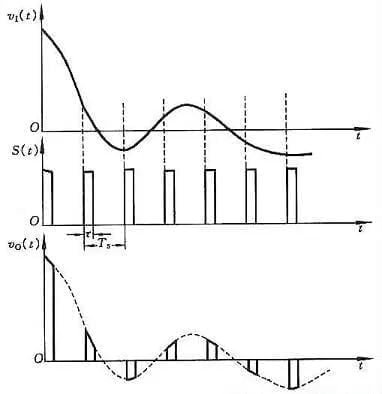

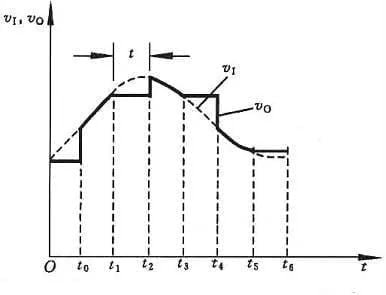

Дискретизация — это преобразование аналоговой величины, которая непрерывно изменяется во времени, в дискретную по времени аналоговую величину. Схематическое изображение процесса дискретизации показано на рисунке 1. Рисунок (а) представляет собой схему схемы дискретизации, в которой передающий затвор управляется сигналом дискретизации S(t), в течение длительности импульса τ сигнала S(t) передающий затвор включен, выходной сигнал vO(t) равен входному сигналу v1, а в течение (Ts-τ) передающий затвор закрыт и выходной сигнал vO(t)=0. Формы сигналов в схеме показаны на рисунке (b).

Из анализа видно, что чем выше частота дискретизирующего сигнала S(t), тем точнее полученный сигнал может воспроизводить входной сигнал после прохождения через фильтр нижних частот. Но проблема заключается в том, что объем данных увеличивается. Чтобы обеспечить подходящую частоту дискретизации, она должна удовлетворять теореме дискретизации.

Теорема дискретизации: предположим, что частота дискретизирующего сигнала S(t) равна fs, а частота самой высокой частотной составляющей входного аналогового сигнала v1(t) равна fimax, тогда fs и fimax должны удовлетворять следующему соотношению: fs≥2fimax, и в инженерной практике обычно принимается fs> (3~5) fimax.

Для преобразования аналогового сигнала, полученного схемой дискретизации, в цифровой сигнал каждый раз требуется определенное время. Чтобы обеспечить стабильное значение для последующего процесса квантования и кодирования, аналоговый сигнал, получаемый каждый раз, должен удерживаться в течение определенного периода времени схемой удержания.

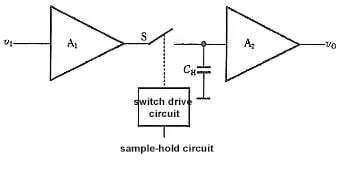

Процесс дискретизации и удержания часто выполняется одновременно с помощью схемы дискретизации-удержания. Схема и выходная форма сигнала схемы дискретизации-удержания показаны на рисунке 2.

Схема состоит из входного усилителя A1, выходного усилителя A2, удерживающего конденсатора CH и схемы управления переключателем. A1 должен иметь высокий входной импеданс в схеме, чтобы уменьшить влияние на источник входного сигнала. Чтобы затруднить разрядку заряда, накопленного на CH во время фазы удержания, A2 также должен иметь высокий входной импеданс, а A2 должен иметь низкий выходной импеданс, что может улучшить нагрузочную способность схемы. Как правило, в схеме также требуется, чтобы AV1·AV2=1.

Теперь в сочетании с рисунком 2 проанализируем принцип работы схемы выборки-удержания. В момент времени t=t0 переключатель S замкнут, и конденсатор быстро заряжается. Поскольку AV1 · AV2=1, v0=vI, период выборки приходится на интервал времени t0~t1. В момент времени t=t1 S размыкается. Если входное сопротивление A2 бесконечно, а S является идеальным переключателем, можно считать, что конденсатор CH не имеет цепи разряда, и напряжение на его обоих концах остается постоянным на уровне v0. Плоский участок от t1 до t2 на рисунке 11.8.2(b) является этапом удержания.

Цепь выборки и удержания может быть реализована с помощью различных типов монолитных интегральных схем. Например, для биполярной технологии существуют AD585 и AD684; для смешанной технологии — AD1154 и SHC76.

Квантование и кодирование

Цифровые сигналы являются не только дискретными во времени, но и не непрерывными по амплитуде. Величина любого цифрового количества может быть только целым кратным заданной минимальной единице количества. Чтобы преобразовать аналоговый сигнал в цифровое количество, в процессе АЦ-преобразования выходное напряжение схемы выборки и удержания также должно быть нормализовано до соответствующего дискретного уровня определенным приближенным способом. Этот процесс преобразования называется квантованием. Квантование, называемое квантованием. Квантованное значение в конечном итоге должно быть представлено кодом посредством процесса кодирования. Код, полученный после кодирования, является цифровой величиной, выводимой АЦП.

Наименьшая единица количества, принимаемая в процессе квантования, называется единицей квантования и обозначается символом △. Это аналоговое количество, соответствующее случаю, когда младший бит цифрового сигнала равен 1, то есть 1LSB.

В процессе квантования, поскольку напряжение дискретизации не обязательно делится на △, неизбежно возникает ошибка до и после квантования. Эта ошибка называется ошибкой квантования и обозначается ε. Ошибка квантования является принципиальной ошибкой, которую невозможно устранить. Чем больше бит имеет АЦП, тем меньше разница между дискретными уровнями и тем меньше ошибка квантования.

В процессе квантования часто используются два приближенных метода квантования: только округление и округление с погрешностью.

только округление метода квантования

Возьмем в качестве примера 3-разрядный АЦП. Пусть входной сигнал v1 находится в диапазоне от 0 до 8 В. При использовании метода округления вверх возьмем △=1 В и отбросим часть, которая не вписывается в квантующий элемент. Если значение находится в диапазоне от 0 до 8 В, аналоговое напряжение между 1 В считается 0△, что представляется двоичным числом 000, а аналоговое напряжение между 1 В и 2 В считается 1△, что представляется двоичным числом 001… Максимальная погрешность этого метода квантования составляет △.

метод округления квантования

Если используется метод округления квантования, применяется квантование △=8V/15, и часть, меньшая половины квантования, будет отбрасываться в процессе квантования, а часть, равная или большая половины квантования, будет рассматриваться как одно квантование. Аналоговое напряжение в диапазоне от 0 до 8 В/15 рассматривается как 0△, что обозначается двоичным кодом 000, а аналоговое напряжение в диапазоне от 8 В/15 до 24 В/15 рассматривается как 1△, что обозначается двоичным кодом 001, означающим ожидание.

Сравнение

Максимальная ошибка квантования│εmax│=1LSB в первом методе квантования с округлением и метод квантования│εmax│=1LSB/2 во втором методе квантования с округлением и округлением, ошибка квантования второго метода меньше, чем первого, поэтому он чаще используется в АЦП.

С быстрым развитием интегральных схем появляются новые идеи проектирования и технологии производства АЦП. АЦП с различной структурой и характеристиками разрабатываются для удовлетворения различных потребностей в области обнаружения и управления.

Типы АЦП

Интеграция ADC

принцип преобразования

Принцип преобразования интегрирующего АЦП основан на интегрировании напряжения и сравнении интегрированного напряжения с другим напряжением для управления счетом, а выход счета является выходом АЦП. Объект интегрирования основан либо на опорном напряжении, либо на опорном напряжении и входном напряжении.

Плюсы и минусы

Преимущества:

- Встроенный АЦП имеет высокое разрешение, а количество разрядов может быть 12 или даже больше.

- Линейность очень хорошая. По сути, входной сигнал сравнивается с интегрированным эталонным напряжением для определения выходного сигнала, поэтому линейность будет зависеть от точности компаратора.

- Топология реализации схемы проста, и для реализации этих устройств используется относительно мало компонентов, поэтому схема относительно проста, а стоимость производства невысока.

Недостаток:

- Основным недостатком является низкая скорость преобразования. В N-разрядном АЦП для преобразования одной точки выборки может потребоваться до 2 N тактов.

Приложения

В основном используется в датчиках и устройствах, таких как вольтметры и амперметры, где точность важнее скорости. Другими словами, скорость дискретизации интегрального АЦП относительно низкая, но точность очень высокая.

классификация

Существуют различные типы интегральных АЦП, наиболее распространенными из которых являются одно- и двунаклонные интегралы. Добавление «наклона» повышает точность за счет увеличения времени преобразования.

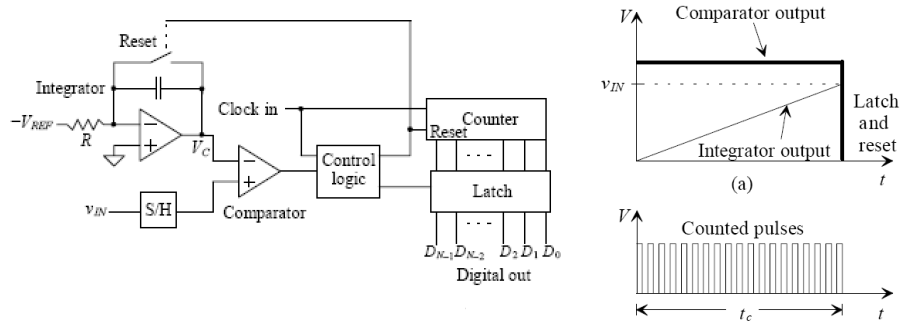

АЦП с одним наклоном интеграла

Компаратор сравнивает входное напряжение со значением интегрированного опорного напряжения (обратите внимание, что мы сделаем его отрицательным, поскольку оно подключено к инвертирующему входу операционного усилителя). Одновременно подсчитывается количество тактов. Когда выход интегратора равен, компаратор выдает логический «0», запуская сброс счетчика и интегратора, а защелка удерживает цифровой выход.

VINVREFVrefVrefVin

Это время преобразования. Я знаю, почему этот интегральный АЦП работает медленно. Давайте рассмотрим худший случай, предположив, что входное напряжение , предположив, что , предположив, что это 20-разрядный АЦП, тогда!

VIN=VREFTCLK=1ustc=220us=1048576us

АЦП с одним наклоном интеграла

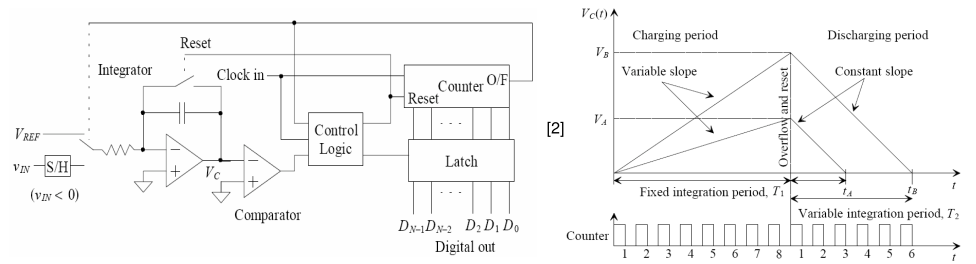

АЦП с двойным наклоном отличается от АЦП с одинарным наклоном тем, что теперь производится сравнение с землей и интегрируются две суммы напряжений. Изначально отрицательный вход подключается к интегратору, который нарастает до переполнения счетчика. Поскольку интегрирование на инвертирующем входе переключается на отрицательное значение, выход интегратора всегда будет положительным и больше нуля, поэтому счетчик будет работать до переполнения, что занимает 2N тактов (=T1).

VCVREFVINVC

В момент времени T2 оно будет равно сумме и, и оно

VC=VC1+VC2=0

Но:

VIN/VREF=T2/T1

Таким образом, согласно принципу преобразования АЦП, АЦП с двойным наклоном работает медленнее, чем АЦП с одинарным наклоном, поскольку интегрирование выполняется дважды, ошибка, связанная с наклоном интегратора, будет скомпенсирована, что в принципе повышает точность.

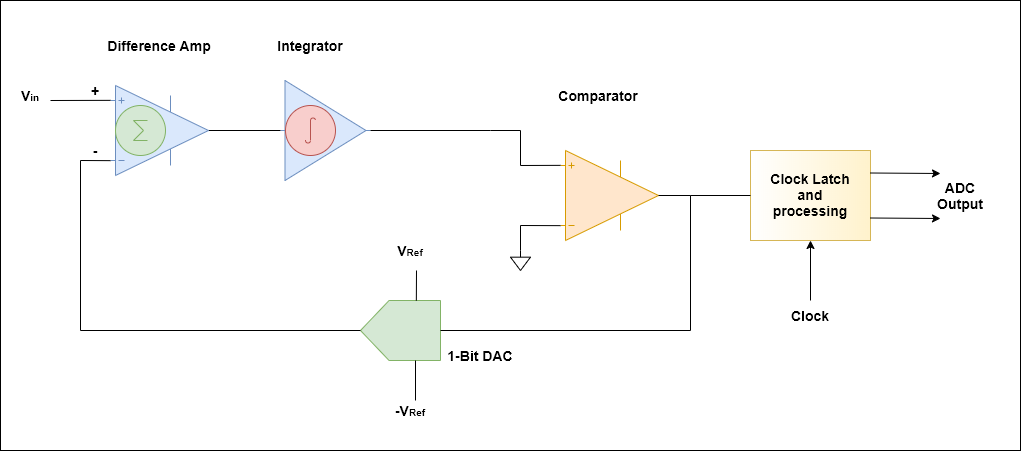

Сигма-дельта Σ-Δ АЦП

Начиная с входа, усилитель разности производит выходной сигнал, который представляет собой разность между Vin и 1-разрядным выходом ЦАП. Выходной сигнал 1-разрядного ЦАП может иметь одно из двух значений: ИЛИ . В этой топологии интегратор можно рассматривать как устройство, вычисляющее скользящее среднее значение предыдущего значения и текущего входного значения.

—Vref+Vref

Таким образом, если предположить, что положительный сегмент компаратора изначально зафиксирован на небольшом значении выше 0 В, компаратор меняет направление. Его значение будет высоким или 1. Затем выход ЦАП будет . На следующей итерации это значение будет вычтено из текущего значения . Поскольку предыдущее значение было 0 В, выход интегратора теперь будет – Vref. В этот момент выход компаратора будет 0, а выход ЦАП будет.

+VrefVin-Vref

На следующей выборке выход интегратора будет равен 0 из-за предыдущего значения, а усилитель разности фактически вычтет , добавив к . Выход компаратора будет равен 1.

-Vref-Vref+VrefVin

Этот процесс продолжается итеративно, поэтому для входа 0 В выход компаратора будет представлять собой постоянный поток 101010…. Помните, что логическая 1 означает , а логическая 0 означает , поэтому, если N выборок отобраны и усреднены, легко увидеть, что среднее значение равно 0 В. Блок обработки после компаратора просто выведет это как одно значение 0000…, предполагая, что эталонное значение равно ( ~ ) или 2 x.

+Vref-Vref-Vref+VrefVref

Теперь, предполагая 1 В, это АЦП 5 В. составляет ±2,5 В. Повторяя те же шаги, что и раньше, выход будет: 1011101… Выход составляет 1,07 В.

Vin±Vref

Вкратце:

АЦП сигма-дельта производит передискретизацию обрабатываемого сигнала (см. раздел «Аналого-цифровая дискретизация» для ознакомления с этим понятием) и фильтрует обрабатываемый сигнал с помощью фильтра нижних частот. Обычно количество битов, преобразуемых с помощью АЦП Flash после фильтра, меньше требуемого количества битов. Полученный сигнал вместе с ошибками от дискретных уровней FLASH возвращается и вычитается из входного сигнала, а затем подается на фильтр. Эта отрицательная обратная связь гасит шум, чтобы он не появлялся на желаемой частоте сигнала. Цифровой фильтр после АЦП (использующий фильтр децимации) снижает частоту дискретизации, отфильтровывает нежелательные шумовые сигналы и увеличивает разрешение выхода (отсюда и название сигма-дельта-модуляция, также известная как дельта-сигма-модуляция).

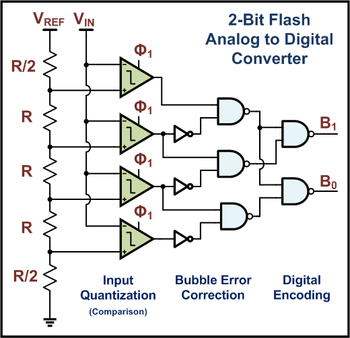

Flash ADC (тип прямого сравнения)

Принцип работы FLASH ADC, пожалуй, самый простой для понимания. На рисунке ниже представлена схема двухразрядного АЦП, состоящего из множества компараторов, каждый из которых снабжен опорным напряжением, на один бит выше предыдущего опорного значения. Таким образом, для 8-разрядного АЦП требуется 256 таких компараторов. Для 10 разрядов — 1024.

LASH ADC (тип прямого сравнения) работает быстро. Он напрямую преобразует входной сигнал без выборки или сложной постобработки. Проблема заключается в том, что для его работы требуется много компараторов, а много компараторов занимают много места на кристалле. Поэтому используйте Fash ADC только в тех случаях, когда вам нужна чрезвычайно высокая скорость, которую невозможно достичь с помощью других реализаций ADC.

Дихотомия, воплощенная в аппаратном обеспечении

В практических приложениях чаще используется другой вариант — полу-FLASH АЦП. Он использует двухэтапный процесс для уменьшения количества преобразователей, необходимых в фактической цепочке преобразования:

Сначала входной сигнал сравнивается с набором уровней, которые лежат ровно в середине . Если он ниже, то старший бит (MSB) устанавливается в 0, а входной сигнал подается на цепочку компараторов с заданным опорным напряжением для преобразования остальных битов.

Если входной сигнал выше, MSB устанавливается в 1, от входного сигнала отнимается . Цепочка компараторов используется снова для получения остальных битов. Таким образом, по сути, полушаговый FLASH АЦП жертвует дополнительным сравнением, чтобы сэкономить половину компаратора. Такой подход можно продолжать развивать и расширять, например, 4-точечный FLASH АЦП и т. д.

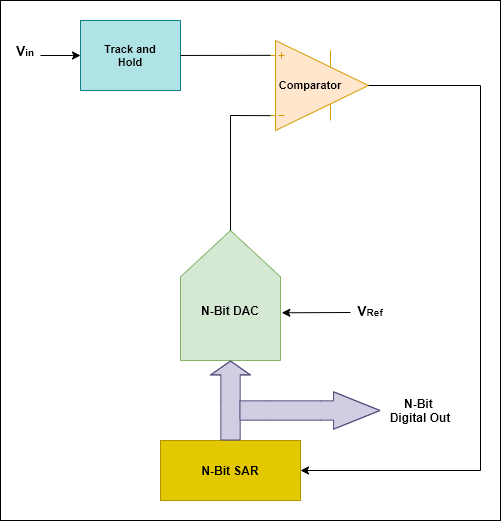

Регистр последовательных приближений (SAR)

Регистр последовательного приближения (SAR) является неотъемлемой частью АЦП последовательного приближения. Он работает с помощью компаратора, постепенно сужая область, содержащую входное напряжение. Для этого преобразователь сравнивает входное напряжение с выходом цифро-аналогового преобразователя, который обычно указывает середину выбранного диапазона напряжений. На каждом этапе процесса оценка сохраняется в SAR.

Например, предположим, что входное напряжение составляет 6,3 В, а начальный диапазон — от 0 до 16 В.

- На первом этапе вводится 6,3 В для сравнения с 8 В (середина диапазона 0–16 В). Компаратор сообщает, что входное напряжение меньше 8 В, поэтому SAR обновляется, чтобы уменьшить диапазон до 0–8 В.

- На втором этапе входное напряжение сравнивается с 4 В (средняя точка диапазона 0–8 В), компаратор сообщает, что входное напряжение превышает 4 В, поэтому SAR обновляется, чтобы отразить, что входное напряжение находится в диапазоне 4–8 В.

- На третьем этапе входное напряжение сравнивается с 6 В (половина диапазона от 4 В до 8 В); компаратор сообщает, что входное напряжение превышает 6 В, и диапазон поиска становится 6–8 В.

Продолжайте эти шаги, пока не достигнете желаемого решения. Его топология выглядит следующим образом:

Для интуитивного понимания посмотрите следующую анимацию:

Последовательный АЦП

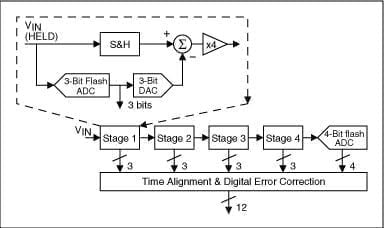

Конвейерный АЦП (также известный как подпрограммный квантователь) использует два или более конвейера. Сначала выполняется грубое преобразование. На втором этапе цифро-аналоговый преобразователь (ЦАП) используется для определения разницы во входном сигнале. Затем эта разница преобразуется в более точные значения, и результаты объединяются на последнем этапе. Это можно считать улучшением по сравнению с АЦП последовательного приближения, где опорный сигнал обратной связи состоит из промежуточных переходов по всему диапазону битов (например, 4 бита), а не только из следующего старшего бита. Объединяя преимущества метода последовательного приближения и флэш-АЦП, этот тип имеет такие преимущества, как высокая скорость, высокое разрешение и небольшой размер корпуса.

В этой схеме аналоговый вход VIN сначала дискретизируется и удерживается стабильным с помощью устройства дискретизации и удержания (S&H), а флэш-АЦП на первом этапе квантует его до трех бит. Затем 3-битный выход подается на 3-битный ЦАП (с точностью 12 бит), и аналоговый выход вычитается из входа. Этот «остаток» увеличивается в 4 раза и отправляется на следующий каскад (каскад 2). Этот добавленный остаток проходит через нижние ступени конвейера, обеспечивая 3 бита на ступень, пока не достигает 4-битного флэш-АЦП, который разрешает последние 4 бита 4LSB. Поскольку биты для каждой ступени определяются в разные моменты времени, все биты, соответствующие одной и той же выборке, выравниваются по времени с регистром сдвига, прежде чем поступают в цифровую логику коррекции ошибок. Обратите внимание, что когда конвейер завершил обработку входных выборок, определив бит приобретения для этого конвейера и передав остаток на следующий конвейер, он может начать обработку следующей выборки, полученной от держателя выборок, встроенного в каждый конвейер. Такая конвейерная обработка является причиной высокой пропускной способности, что также является концепцией конвейерной обработки.

Другие

Помимо вышеупомянутых нескольких распространенных АЦП, существуют также АЦП с принципом баланса заряда, АЦП с разделением времени, АЦП с ЧМ, АЦП с растяжением времени, АЦП с инкрементным кодированием, АЦП Уилкинсона и т. д.

Цифро-аналоговый преобразователь (ЦАП)

Определение DAC

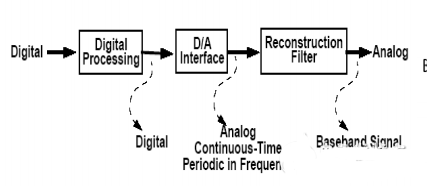

Цифровые данные, обрабатываемые цифровой системой, иногда необходимо преобразовать в аналоговые для практического использования. Это преобразование называется «цифро-аналоговым преобразованием». Схема, выполняющая цифро-аналоговое преобразование, называется цифро-аналоговым преобразователем, или сокращенно ЦАП (цифро-аналоговый преобразователь).

Параметры DAC

Резолюция

Разрешение ЦАП определяется как количество всех возможных выходных аналоговых уровней при различных значениях входного цифрового кода. N-битное разрешение означает, что ЦАП может генерировать 2 N −1 различных аналоговых уровней. Как правило, оно относится к количеству разрядов входного цифрового кода.

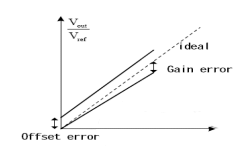

Ошибки смещения и усиления

Смещение определяется как значение фактического выходного аналогового сигнала при вводе кодового значения 0, а погрешность усиления определяется как разница между идеальным полным выходным значением и фактическим выходным значением после вычета смещения, как показано на рисунке.

Точность

Точность ЦАП подразделяется на абсолютную и относительную. Абсолютная точность определяется как разница между идеальным и фактическим выходом, включая различные смещения и нелинейные погрешности. Относительная точность определяется как максимальная интегральная нелинейная погрешность. Точность выражается как отношение полного диапазона, выраженное в эффективных цифрах. Например, 8-битная точность означает, что погрешность ЦАП составляет менее 1/8 2 от полного диапазона выходного сигнала ЦАП. Обратите внимание, что понятие точности не связано с разрешением. ЦАП с разрешением 12 бит может иметь точность только 10 бит, а ЦАП с разрешением 10 бит может иметь точность 12 бит. Точность выше разрешения означает, что передачу сигнала ЦАП можно контролировать с большей точностью.

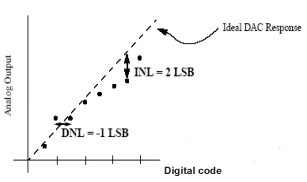

INL — интегральная нелинейность

Когда ошибки смещения и коэффициента усиления устранены, интегральная ошибка линейности определяется как отклонение фактической характеристики передачи выходного сигнала от идеальной характеристики передачи (прямой линии), как показано на рисунке.

DNL — дифференциальная нелинейность

В идеальном ЦАП с минимальным значением 1 LSB на изменение аналогового выхода дифференциальная погрешность линейности определяется как отклонение от 1 LSB на минимальное изменение аналогового выхода (исключая погрешность усиления и смещение). Определяемая нами DNL относится к каждому значению кода цифрового входа, и иногда для определения DNL всего ЦАП используется наибольшая DNL. Идеальный ЦАП будет иметь нулевую дифференциальную погрешность линейности для каждого цифрового входа, в то время как ЦАП с максимальной DNL 0,5 LSB будет иметь минимальное изменение выхода от 0,5 LSB до 1,5 LSB на выход. Интегральная и дифференциальная погрешности линейности ЦАП показаны на рисунке.

Энергия джиттера (площадь импульса глюка)

Максимальная площадь под джиттером, появляющимся на выходе после изменения входного сигнала.

Время оседания

Время установления находится в пределах определенного диапазона погрешности конечного значения и времени, необходимого для полного преобразования выходного сигнала.

Монотонность Монотонный ЦАП — это ЦАП, в котором аналоговый уровень выхода всегда увеличивается по мере увеличения значения входного цифрового кода. Если максимальное DNL контролируется в пределах 0,5 LSB, то монотонность ЦАП может быть гарантирована естественным образом.

Динамический диапазон без паразитных сигналов (SFDR) SFDR — это динамический диапазон без паразитных сигналов, то есть динамический диапазон без шума и гармоник. И шум, и гармоники называются паразитными сигналами.

Принцип DAC

Преобразуйте каждый входной двоичный код в соответствующую аналоговую величину в соответствии с его весом, а затем сложите аналоговые величины, представляющие каждый бит. Полученная общая аналоговая величина пропорциональна цифровой величине, что позволяет реализовать преобразование цифровой величины в аналоговую. Аналоговое преобразование.

Это десятичное значение, преобразованное в двоичное число путем расширения веса бита.

Состав и характеристики DAC

ЦАП в основном состоит из цифровых регистров, аналоговых электронных переключателей, сети весовых коэффициентов разрядов, суммирующего операционного усилителя и источника опорного напряжения (или источника постоянного тока). Используйте цифры цифровых величин, хранящихся в цифровом регистре, для управления аналоговыми электронными переключателями соответствующих цифр, чтобы цифра с цифрой 1 генерировала значение тока, пропорциональное ее весу в сети весов, а затем операционный усилитель управлял каждым значением тока, суммированным и преобразованным в значение напряжения.

Различные сети весовых коэффициентов позволяют собирать несколько видов ЦАП, включая ЦАП с сетью весовых резисторов, ЦАП с инвертированной Т-образной сетью резисторов R-2R и ЦАП с сетью тока с одним значением и т. д. Точность преобразования, производимого ЦАП с сетью весовых резисторов, зависит от точности опорного напряжения VREF, а также от качества аналоговых электронных переключателей, операционных усилителей и значений весовых резисторов. Его недостатком является то, что значения сопротивления каждого весового резистора различны, и при большом количестве разрядов значения сопротивления сильно различаются, что создает большие трудности для обеспечения точности, особенно при производстве интегральных схем. Поэтому в интегральном ЦАП эта схема редко используется отдельно.

Основные технические показатели DAC

Точность и скорость преобразования ЦАП: Точность преобразования обычно описывается разрешением и погрешностью преобразования в ЦАП.

Резолюция

Как правило, для измерения разрешения используется количество бит ЦАП, поскольку чем больше количество бит, тем больше значений (2n) выходного напряжения vO и тем лучше оно может отражать тонкие изменения выходного напряжения.

Кроме того, разрешение можно также определить как отношение минимального выходного напряжения 1 LSB, которое ЦАП может различить, к максимальному выходному напряжению FSR. То есть:

разрешение = 1LSB/FSR = k/k(2n-1) = 1/(2n-1)

Чем меньше значение, тем выше разрешение.

Ошибка преобразования

Ошибка преобразования — это максимальное отклонение между фактическим выходным аналоговым напряжением и идеальным значением. Обычно выражается в процентах или нескольких LSB от отношения этого максимального отклонения к FSR. Фактически, это комплексный показатель трех ошибок.

Скорость преобразования

Скорость преобразования обычно определяется временем установления. Период от момента, когда входной сигнал меняется со всех нулей на все единицы, до момента, когда выходное напряжение стабилизируется в диапазоне FSR±½ LSB (или в диапазоне, указанном FSR±x%FSR), называется временем установления, которое является максимальным временем отклика ЦАП, поэтому его используют для измерения скорости преобразования.

Типы DAC

Тип сопротивления

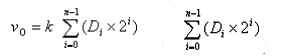

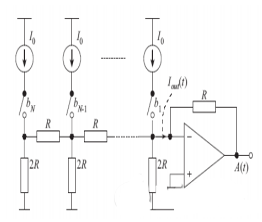

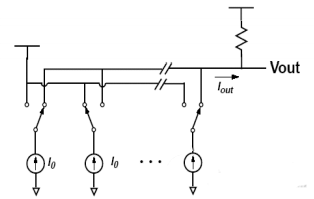

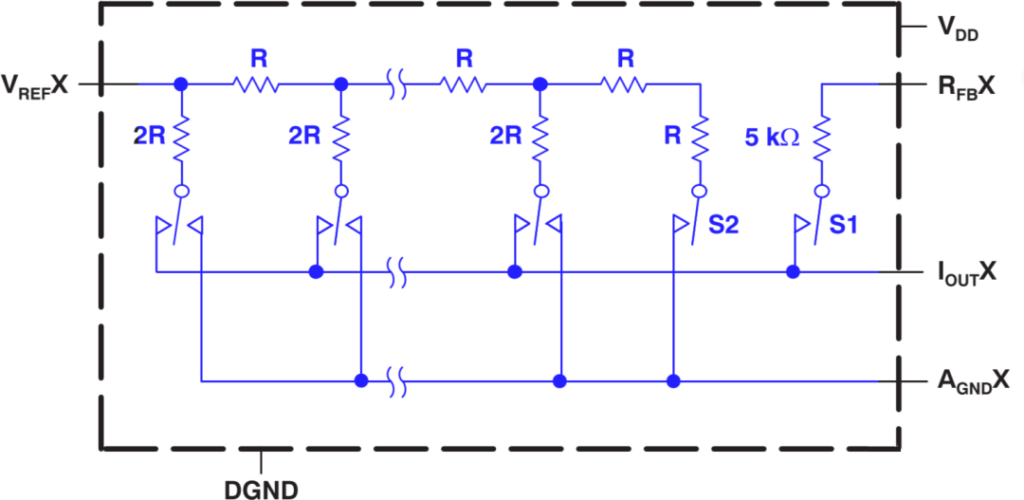

Структура показана на рисунке 1. На рисунке 1 показан преобразователь типа R-2R лестничной сети. Его преимущество заключается в том, что он может достигать очень хорошей линейности. Поскольку все источники тока эквивалентны, мы можем использовать специальную дополнительную технологию, чтобы уменьшить погрешность между ними, а его структура намного проще, чем у резистивного делителя. Недостатком является то, что сопротивление всегда нелинейно, а также содержит паразитную емкость, связанную с сигналом, поэтому трудно достичь полного согласования. В то же время скорость ограничена выходным буфером, и она не может быть очень высокой.

Емкостный тип

Структура показана на рисунке 2. Емкость высшего порядка CN в 1 2N− раз превышает емкость низшего порядка C1. Преимуществом является низкое энергопотребление и более высокая точность согласования по сравнению с резистором. Основными ограничивающими факторами являются несоответствие емкостей конденсаторов, сопротивление в включенном состоянии переключателей, большие RC-задержки и влияние ограниченной полосы пропускания усилителя на скорость ЦАП. Основным недостатком ЦАП с распределением заряда является то, что конденсаторы в процессах CMOS занимают много площади чипа для реализации. Наконец, поскольку емкость в процессе CMOS по своей природе нелинейна, линейность всего ЦАП будет подавлена. Подходит для средних и широких полос высокой точности.

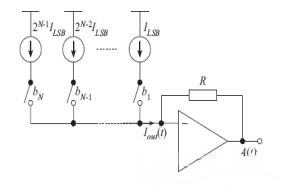

Текущий тип

Структура показана на рисунке 3. Преимущество заключается в том, что при точности менее 10 бит площадь может быть очень маленькой, а скорость не ограничивается полосой пропускания усилителя и большой задержкой RC. Она может достигать очень высокой скорости. Поскольку весь ток протекает непосредственно к выходному выводу, энергопотребление является высокоэффективным и простым в реализации. Недостатками являются чувствительность к несоответствию устройств и ограниченное выходное сопротивление источника тока. Подходит для высокоскоростных широкополосных требований.

Также возможно не использовать операционный усилитель для вывода, а напрямую использовать сопротивление нагрузки для преобразования тока в выходной сигнал напряжения, как показано на рисунке 4. Такая форма позволяет не ограничивать скорость ЦАП полосой пропускания операционного усилителя.

Типичное умножение

Некоторые ЦАП используют постоянное опорное напряжение, а некоторые добавляют сигнал переменного тока к входу опорного напряжения. Последние называются ЦАП умножающего типа, поскольку они могут получать результат умножения цифрового входа и входа опорного напряжения. Как правило, ЦАП умножающего типа могут не только выполнять умножение, но и использоваться в качестве аттенюатора для цифрового ослабления входного сигнала и модулятора для модуляции входного сигнала.

Один DA-преобразователь

В отличие от только что описанной системы преобразования, ЦАП использует специальный метод преобразования цифровых значений в широтно-импульсную модуляцию или частотную модуляцию, которая затем сглаживается с помощью цифрового фильтра для получения широко используемого выходного напряжения (также известного как режим битового потока) для аудио и т. д.

Заключение

АЦП и ЦАП — два важнейших компонента любой цифровой системы. Они помогают преобразовывать аналоговые сигналы в цифровые и наоборот. АЦП (аналогово-цифровой преобразователь) принимает аналоговый сигнал и преобразует его в цифровой, а ЦАП (цифро-аналоговый преобразователь) принимает цифровой сигнал и преобразует его в аналоговый. Оба этих компонента важны для широкого спектра применений, от обработки аудио и видео до передачи данных. В этой статье мы рассмотрели, как работают эти преобразователи и какую роль они играют в различных приложениях. Мы также рассмотрели различные типы преобразователей, различные типы сигналов, которые они могут преобразовывать, а также преимущества и недостатки каждого типа.