FPGA, сокращение от Field Programmable Gate Array (программируемая матрица логических элементов), представляет собой аппаратную реконфигурируемую архитектуру. Другими словами, это микросхема, которую можно запрограммировать для изменения ее внутренней структуры. FPGA уже много лет используются в качестве малосерийной замены микросхем специального назначения (ASIC).

Основная структура FPGA

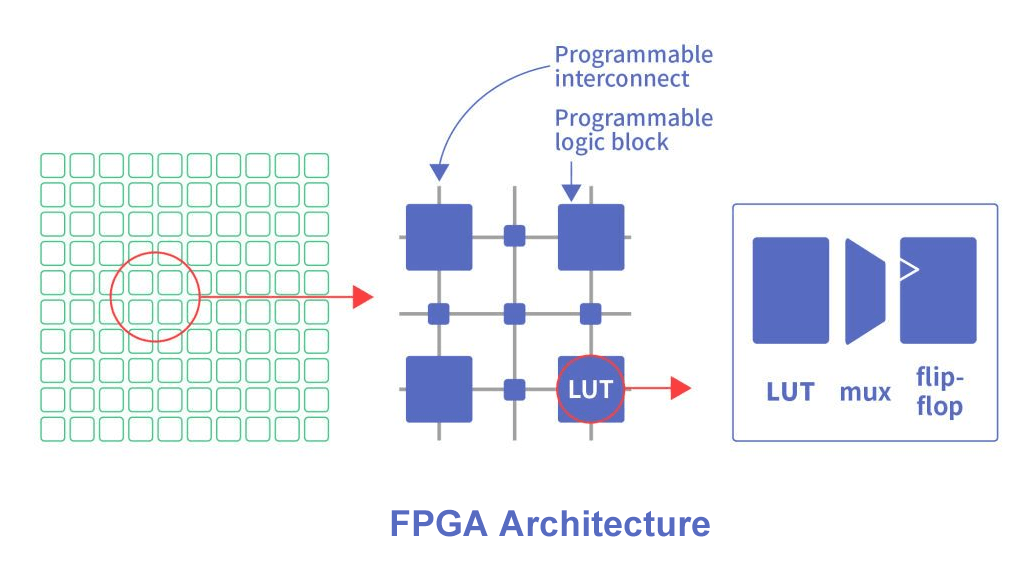

Архитектура FPGA в основном состоит из четырех частей: конфигурируемого логического блока (CLB), блока ввода-вывода (IOB), внутренней проводки (Interconnect) и других встроенных блоков. Внутренняя структура устройства FPGA показана ниже.

Конфигурируемый логический блок (CLB)

CLB — это базовая логическая единица FPGA. Фактическое количество и характеристики варьируются в зависимости от устройства, но каждый CLB содержит настраиваемую матрицу переключателей с 4 или 6 входами, несколько схем выбора (мультиплексоры и т. д.) и триггеры.

Блок ввода-вывода (IOB)

FPGA могут поддерживать многие стандарты ввода-вывода, что делает их идеальным интерфейсным мостом для системных конструкций. Входы-выходы в FPGA сгруппированы по банкам, и каждый банк может независимо поддерживать различные стандарты ввода-вывода. В настоящее время самые передовые FPGA предоставляют более десяти банков ввода-вывода, что обеспечивает гибкую поддержку ввода-вывода.

Внутренняя проводка (соединительная)

CLB обеспечивают логическую производительность, а гибкая маршрутизация межсоединений отвечает за передачу сигналов между CLB и входами/выходами. Существует несколько типов маршрутизации, от выделенных межсоединений CLB (ресурсы коротких проводов) до высокоскоростных горизонтальных и вертикальных длинных проводов (ресурсы длинных проводов) внутри устройства, а также глобальной маршрутизации с низким сдвигом для тактовых сигналов и других глобальных сигналов (глобальные выделенные ресурсы маршрутизации).

Встроенные устройства

Встроенные ядра включают в себя ОЗУ, DSP, DCM (модуль управления цифровыми часами) и другие специфические интерфейсные ядра и т. д.

Особенности FPGA

- Использование FPGA для проектирования схемы ASIC обеспечивает короткий цикл, низкую стоимость, небольшой риск и стабильное качество;

- FPGA использует высокоскоростную технологию CHMOS с низким энергопотреблением;

- Архитектура FPGA, гибкий логический блок, высокая степень интеграции, широкий спектр применения;

- FPGA совместим с преимуществами PLD и общей матрицы вентилей и может реализовывать крупномасштабные схемы;

- Возможно перепрограммирование на месте, а затраты на последующее обслуживание низкие;

- FPGA — это параллельная вычислительная система, которая может одновременно удовлетворять многофункциональным требованиям.

Как работает FPGA?

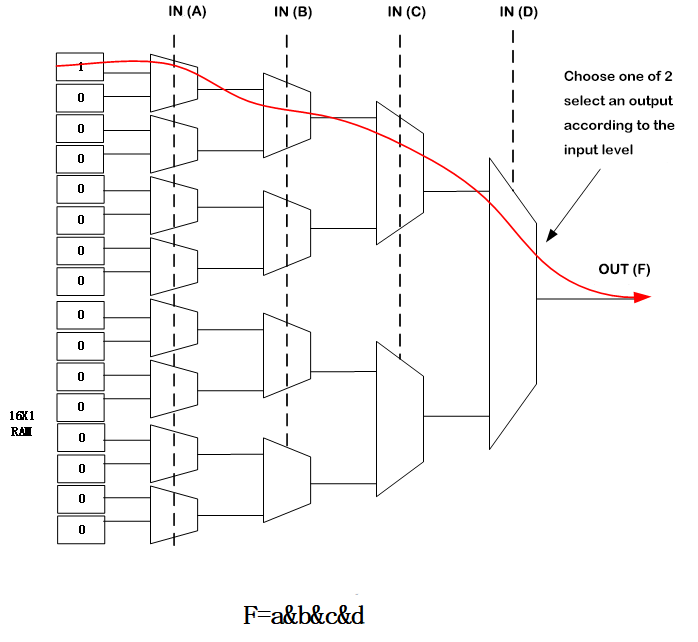

FPGA реализует логические функции путем загрузки данных программирования во внутренние статические блоки памяти. Значение, хранящееся в блоке памяти, определяет логическую функцию логического блока и режим соединения между каждым модулем логического блока или между модулем и входом/выходом, и, в конечном итоге, определяет функцию FPGA. FPGA использует небольшую таблицу просмотра для реализации комбинационной логики, каждая таблица просмотра подключена к входу D-триггера, а D-триггер используется для управления другими логическими схемами или входом/выходом, тем самым формируя комбинированную логическую функцию и реализуя базовый модуль логического блока последовательной логической функции. Эти модули соединены друг с другом или с модулем входа/выхода металлическими проводами.

Вот простой пример, объясняющий принцип работы FPGA:

Как показано на рисунке выше, мы настраиваем 16bitRAM как 0000000000000001, и эта схема эквивалентна F=A&B&C&D;

Только когда A=B=C=D=1, F=1, в противном случае F=0;

«0000000000000001» Эта строка цифр является программированием FPGA.

Логический блок FPGA

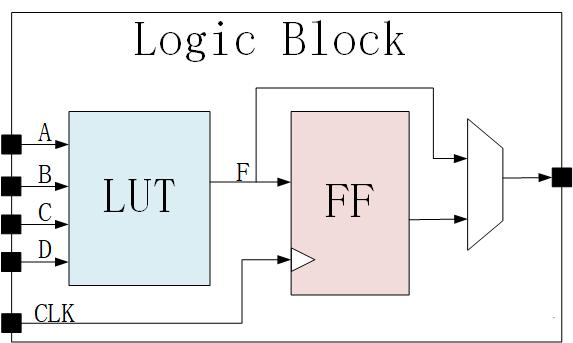

В FPGA есть специальный термин, называемый LUT, таблица просмотра (lookup table).

LUT является наиболее базовой единицей любого FPGA.

LUT может реализовывать только цифровую комбинационную логику, поэтому для реализации фиксации данных добавляется регистр-триггер (ff);

Как показано на рисунке ниже: LUT+ регистры образуют базовую структуру современных FPGA.

Процесс разработки FPGA

Процесс разработки FPGA — это процесс использования программного обеспечения для разработки EDA и инструментов программирования для разработки микросхем FPGA. Процесс разработки FPGA в целом показан на рисунке ниже и включает в себя такие основные этапы, как определение функций/выбор устройств, ввод данных для проектирования, моделирование функций, логический синтез, компоновка и трассировка, реализация, программирование и отладка.

Определение функции/выбор устройства:

Перед началом проекта по разработке ПЛИС необходимо определить функции системы и разделить модули. Кроме того, в соответствии с требованиями задачи, такими как функции и сложность системы, можно распределить скорость работы, ресурсы, затраты и соединения самого устройства. Необходимо найти компромисс между такими аспектами, как производительность, и выбрать подходящую схему проектирования и тип устройства.

Ввод данных для проектирования:

Ввод данных для проектирования означает использование языка описания аппаратного обеспечения для выражения проектируемой системы или схемы в виде кода. Наиболее часто используемым языком описания аппаратного обеспечения является Verilog HDL.

Функциональное моделирование:

Функциональное моделирование означает проверку логической функции схемы, разработанной пользователем, перед логическим синтезом. Перед моделированием необходимо создать тестовую платформу и подготовить тестовые стимулы. Результаты моделирования будут сгенерировать файлы отчетов и выходные сигнальные формы, из которых можно наблюдать изменения сигналов каждого узла. Если обнаружены ошибки, вернитесь к проектированию, чтобы пересмотреть логический дизайн. Обычные инструменты моделирования включают ModelSim от Model Tech, VCS от Sysnopsys и другое программное обеспечение.

Логический синтез:

Так называемый синтез заключается в преобразовании описания более высокого уровня абстракции в описание более низкого уровня. Синтетическая оптимизация оптимизирует сгенерированные логические связи в соответствии с целями и требованиями и делает иерархический дизайн плоским для реализации программным обеспечением FPGA для компоновки и трассировки. Что касается текущего уровня, комплексная оптимизация означает компиляцию входных данных дизайна в логически связанный список сетей, состоящий из базовых логических единиц, таких как И-врата, ИЛИ-врата, НЕ-врата, ОЗУ и триггеры, а не реальных схем на уровне врат.

Макет и реализация:

Под компоновкой и трассировкой можно понимать использование инструментов реализации для отображения логики на ресурсы структуры целевого устройства, определения оптимальной компоновки логики, выбора каналов соединений, связанных логикой и функциями ввода-вывода, а также генерации соответствующих файлов (таких как файлы конфигурации и связанные отчеты); реализация заключается в настройке списка логических цепей, сгенерированного синтезом, для конкретного чипа FPGA. Поскольку только производитель микросхем FPGA лучше всего знает структуру микросхемы, для компоновки и трассировки необходимо выбирать инструменты, предоставляемые разработчиком микросхемы.

Отладка программирования:

Последним этапом проектирования является программирование и отладка. Программирование микросхемы означает создание файлов данных (файлов битового потока, Bitstream Generaon) и загрузку данных программирования в микросхему FPGA; после этого можно провести тестирование платы. Наконец, загрузите файл FPGA (например, файл .bit) с компьютера в микросхему FPGA на плате.

FPGA против CPU и GPU

Как ЦП, так и ГП следуют архитектуре фон Неймана с декодированием инструкций и общей памятью. В отличие от них, ПЛИС имеют принципиально иную архитектуру, которая не зависит от инструкций и не требует общей памяти. Нижеприведенная таблица показывает их различия:

| Feature | FPGA | CPU | GPU |

|---|---|---|---|

| Architecture | Reconfigurable logic | Von Neumann | Von Neumann |

| Instruction | No instructions | Instructions | Instructions |

| Shared Memory | No shared memory | Arbitration and shared memory | Arbitration and shared memory |

| Parallel Processing | Pipeline and data parallelism | Data parallelism | Data parallelism |

| Flexibility | Reprogrammable | Fixed functionality | Fixed functionality |

| Computational Power | Suitable for complex tasks | General-purpose computing | Parallel computing and vector processing |

| Latency | Low latency | Medium latency | Relatively high latency |

| Power Consumption | High power consumption | Medium power consumption | High power consumption |

| Application Areas | Electronics, communication, embedded systems | General-purpose computing | Graphics processing, scientific computing |

Необходимые навыки для инженеров FPGA

- Язык Verilog и его связь с аппаратными схемами

- Инструменты разработки (владение Synplify, vivodo, ISE, Modelsim)

- Знакомство с процессом проектирования FPGA (моделирование, синтез, компоновка и трассировка, анализ временных характеристик)

- Владение оценкой ресурсов (особенно оценкой слайсов, lut, ram и других ресурсов)

- Владение основными концепциями (такими как время установки, время удержания, расчет потока, расчет времени задержки, конкурентный риск, методы устранения глюков и т. д.)

- Цифровые схемы (комбинационные схемы, триггеры, особенно D-триггеры, составляющие делитель частоты, последовательные схемы, которые могут быть описаны на языке Verilog)

Производители ПЛИС

- Xilinx: платформа разработки — ISE, изобретатель FPGA;

- Altera: платформа разработки — Quartus II, изобретатель программируемых логических устройств;

- Actel: платформа разработки — Libero;

- Lattice: платформа разработки — ISPLEVER;

- Atmel