Тестирование ИС заключается в выявлении конструктивных дефектов чипа или физических дефектов, вызванных производственным процессом. Этот процесс может быть осуществлен с помощью различных методов тестирования.

Упаковка ИС — это процесс помещения интегральной схемы (ИС) в защитную упаковку. Этот процесс защищает ИС от повреждений и обеспечивает ее правильную работу. Он также позволяет подключать ИС к другим устройствам и схемам.

Как проверить микросхему с помощью тестера микросхем?

набор для тестирования ic

На рынке доступно несколько различных типов наборов для тестирования ИС, каждый из которых предназначен для конкретной цели. Например, некоторые наборы для тестирования ИС предназначены для тестирования общего назначения. Другие же разработаны для конкретных применений, таких как автомобильные ИС или ИС питания.

Большинство наборов для тестирования ИС включают в себя различные базовые аксессуары, такие как мультиметр, пробы, цифровой тестер ИС и испытательные провода. Некоторые наборы могут также включать более специализированное оборудование, такое как осциллограф или логический анализатор.

Метод испытания

Существует несколько способов тестирования ИС, но наиболее распространенным методом является тестирование в схеме (ICT). Этот тип тестирования выполняется путем подключения испытательного приспособления к тестируемому устройству (DUT). Затем мы проводим серию тестов для проверки основных функций.

ICT можно использовать для тестирования как цифровых, так и аналоговых ИС. Для цифровых ИС тестер посылает серию входных сигналов на DUT. Затем он проверяет выходы, чтобы увидеть, соответствуют ли они ожидаемым результатам. Аналоговые ИС обычно тестируются с помощью метода, называемого динамическим тестированием. Во время этого процесса тестер подает серию сигналов на DUT, а затем измеряет ответ.

Существуют различные компании, производящие ICT-тестеры, вам необходимо выбрать тот, который совместим с вашими конкретными IC. После приобретения тестера вам необходимо создать испытательное приспособление, которое подключается к DUT. Испытательное приспособление может подавать необходимые сигналы на DUT, а также измерять ответ.

После того, как у вас есть и то, и другое, вам нужно написать тестовую программу для проверки результатов. Это может быть трудоемкий процесс, но он важен для обеспечения правильной работы ваших интегральных схем.

Типы тестирования

Тест на непрерывность IC

Тест на целостность ИС прост, и с его помощью можно определить, работают ли ИС должным образом.

Этот тест выполняется путем подключения мультиметра к микросхеме и измерения сопротивления между различными выводами.

Если микросхема работает правильно, сопротивление должно быть низким (обычно менее 10 Ом). В противном случае сопротивление будет высоким (обычно более 10 Ом).

тестирование уровня

Тестирование на уровне ИС — это вид электрического тестирования, позволяющий определить функции и характеристики интегральных схем (ИС).

Это тестирование обычно проводится на IC, которые уже установлены на печатной плате.

Цель тестирования — проверить, что IC функционирует должным образом и соответствует спецификациям для предполагаемого использования.

Существует множество различных методов тестирования на уровне интегральных схем, в том числе логическое тестирование, функциональное тестирование и параметрическое тестирование.

Путь развития упаковки интегральных схем

Упаковка прошла примерно следующий процесс развития:

1. С точки зрения структуры:

TO->DIP->PLCC->QFP->BGA->CSP->WLP и SiP и т. д.

2. Материалы:

Металл, керамика -> керамика, пластик -> пластик;

3. Форма выводов:

Длинный вывод в линию -> короткий вывод или монтаж без выводов -> шариковый вывод

4. Метод сборки:

Вставка в сквозное отверстие -> Поверхностный монтаж -> Прямой монтаж

5. Движущая сила постоянного совершенствования упаковки:

Меньший размер, больше типов чипов, больше входов/выходов

6. Сложности:

Процесс становится все более сложным, и необходимо учитывать теплоотвод и электропроводность при одновременном уменьшении объема.

Особенности и основные конкурентные преимущества

1. Сильные производственные характеристики

Производственная мощность полностью зависит от закупки оборудования (капиталовложений) и, как и в традиционном производстве, также проходит процесс наращивания мощностей и оптимизации процессов. С ростом масштабов приходит накопление опыта и преимущества передовых технологий.

2. Масштаб упаковки и тестирования определяет структуру клиентов.

Крупные производители проектируются будут сотрудничать только с производителями тестов определенного масштаба. Если масштаб не увеличивается, трудно выполнять крупные заказы и оптимизировать структуру клиентов. Поэтому компании с передовыми технологиями и масштабом войдут в благотворный круг: передовые технологии → развитие клиентской базы → расширение финансирования → наращивание производственных мощностей → оптимизация процессов → передовые технологии, и постепенно увеличат отрыв от конкурентов.

3. Основная конкурентоспособность

Две вышеуказанные особенности отрасли определяют основную конкурентоспособность компаний, специализирующихся на профессиональном тестировании интегральных схем:

Возможности в области НИОКР: фокус на разработке процедур тестирования и тестовых решений.

Степень рыночной ориентации: возможности по разработке программ тестирования и оптимизации процессов основаны на опыте тестирования различных типов микросхем, полученном от большого числа клиентов.

Совершенный процесс тестирования: благодаря тесной интеграции верхнего уровня проектирования и обработки пластин, процесс тестирования и технологический процесс постоянно оптимизируются.

Способность к операциям с капиталом: текущая стадия развития в стране определяет, что масштаб является предпосылкой развития. Поэтому способность к финансированию, соответствующая технологической и рыночной мощности, является опорой для развития и роста предприятия.

рынок корпусов и тестирования интегральных схем

1. Масштаб упаковки и тестирования интегральных схем

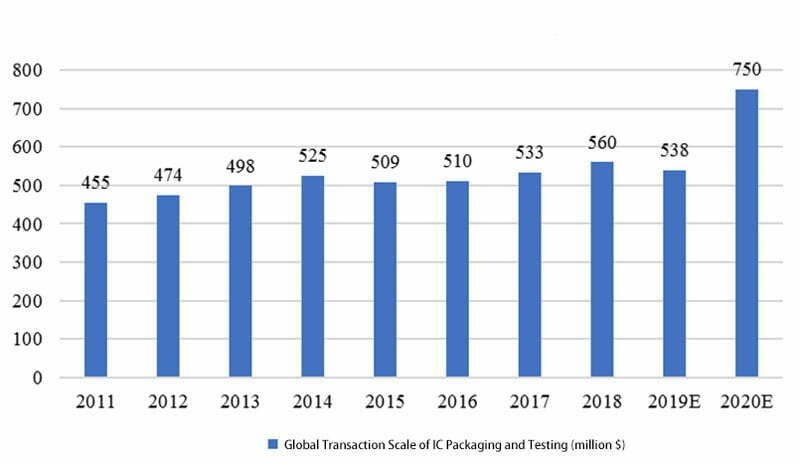

1.1 Глобальные сделки в сфере упаковки и тестирования интегральных схем (2011–2020 гг.)

В 2019 году в целом отрасль полупроводников замедлилась и продемонстрировала отрицательный рост, как и рынок упаковки и тестирования микросхем. Однако впоследствии рынок восстановился благодаря спросу на 5G, ИИ, IoT, облачные вычисления и большие данные. Эксперты прогнозируют, что в 2024 году общий объем рынка упаковки и тестирования микросхем может достичь 75 миллиардов долларов.

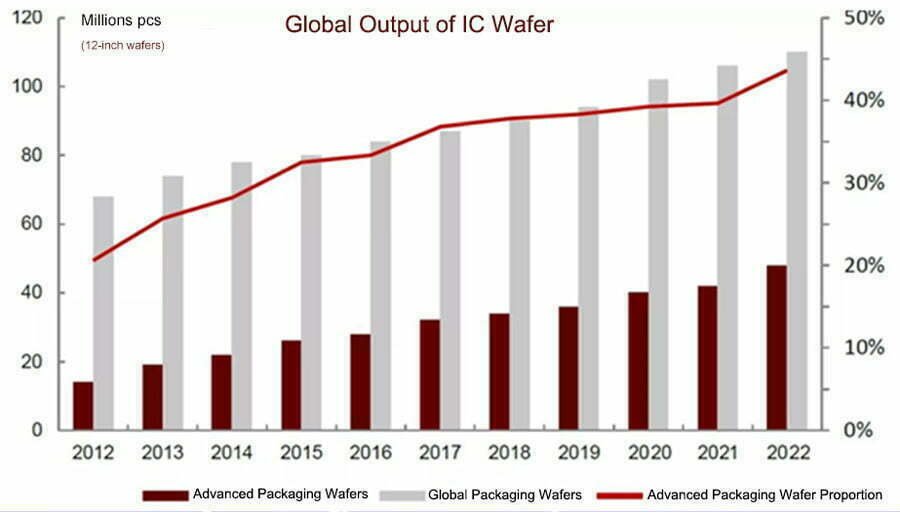

1.2 Мировой объем производства полупроводниковых пластин (2012–2022 гг.)

С ускорением развития таких новых областей, как 5G, IoT и AI, требуемый размер чипов становится все меньше и меньше. В то же время появляется все больше и больше типов чипов. Количество выводов ввода-вывода также значительно увеличилось, и спрос на передовые упаковочные технологии постепенно растет.

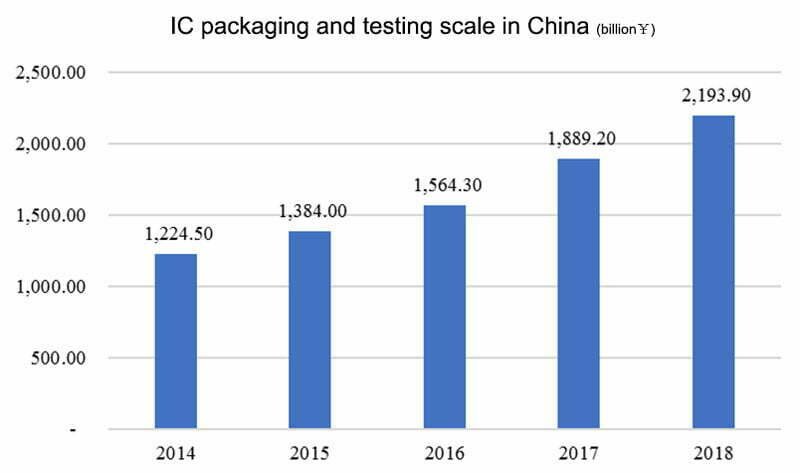

1.3 Масштабы упаковки и тестирования iC в Китае (2014–2018 гг.)

В 2018 году мощности по упаковке и тестированию интегральных схем в материковом Китае достигли 217,44 млрд штук, а объем рынка упаковки и тестирования интегральных схем достиг 219,39 млрд юаней, что на 16,1% больше, чем в предыдущем году.

2. Рост масштабов производства современной упаковки

2.1 Доля передовых IC-корпусов в общем объеме

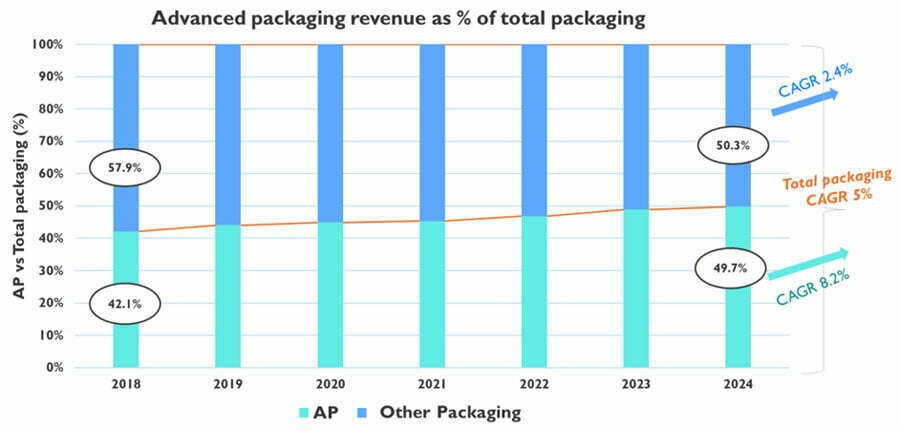

Согласно статистике Yole, несмотря на то, что в 2019 году в целом отрасль полупроводников пережила замедление и отрицательный рост, объем рынка передовых упаковочных материалов сохранит тенденцию к росту. В 2018 году объем рынка передовых упаковочных материалов составил 27,6 млрд долларов США.

Он будет расти со среднегодовым темпом роста 8% и к 2024 году достигнет примерно 44 млрд долларов США. Традиционный рынок упаковки будет расти со среднегодовым темпом роста 2,4%, в то время как среднегодовой темп роста всей отрасли упаковки интегральных схем достигнет 5%.

2.2 Прогноз динамики выручки в сегменте передовых упаковочных материалов (2018–2024 гг.)

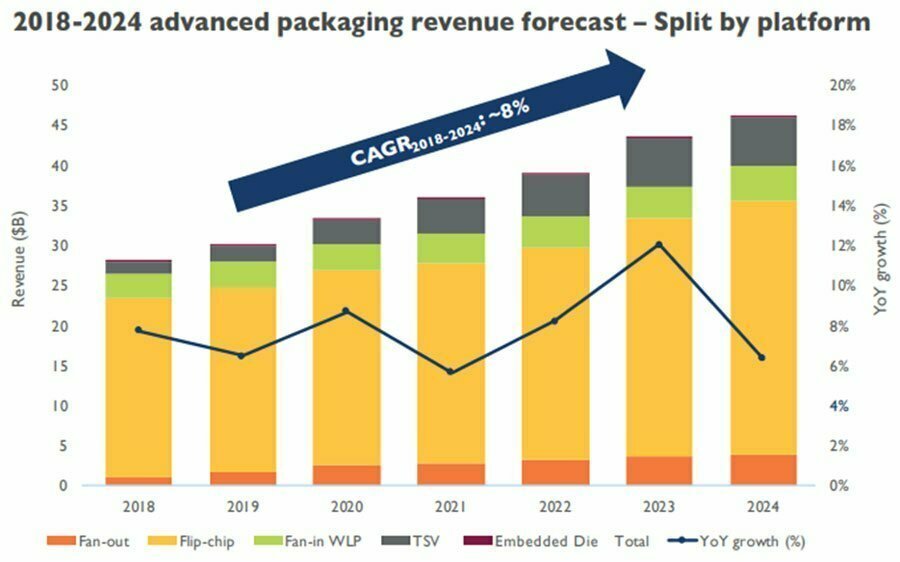

В сфере передовых упаковочных технологий наибольшую долю занимает технология флип-чип. В 2018 году доход от упаковки и тестирования флип-чипов составил около 81% рынка передовых упаковочных технологий. К 2024 году, в связи с быстрым развитием других технологий, эта доля снизится до 72%.

С 2018 по 2024 год самыми быстрорастущими технологиями будут TVS, ED и fan-out. Прогнозируемый темп роста выручки от 2.5D/3D-упаковки (TSV), ED и fan-out-упаковки (Fan-out) составит соответственно 26%, 49% и 26%.

Среднегодовой темп роста Fan-in WLP в 2018-2024 годах относительно низок, всего 6,5%, а объем рынка встроенных микросхем в 2018 году составляет менее 25 миллионов долларов США.

Однако в ближайшие пять лет среднегодовой темп роста составит 49%, и основными движущими факторами будут спрос со стороны средств связи, автомобильной электроники и мобильных рынков.

2.3 Передовые применения в области упаковки

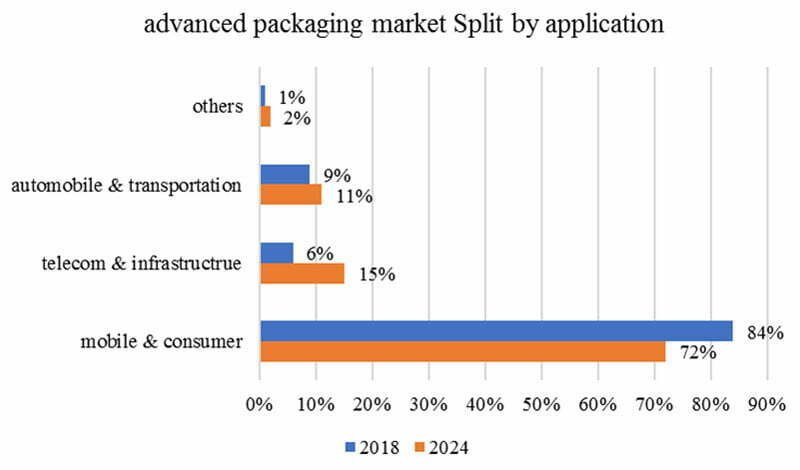

По областям применения в 2018 году на мобильные и потребительские приложения приходилось 84 % всего рынка передовой упаковки. С 2019 по 2024 год среднегодовой темп роста этого сегмента рынка применений составил 5 %, а в 2024 году он составил 72 % всего рынка передовой упаковки.

Сегмент телекоммуникаций и инфраструктуры является самым быстрорастущим сегментом рынка передовой упаковки (около 28%), и его доля рынка вырастет с 6% в 2018 году до 15% в 2024 году.

В то же время доля рынка сегмента автомобилестроения и транспорта выросла с 9% в 2018 году до 11% в 2024 году.

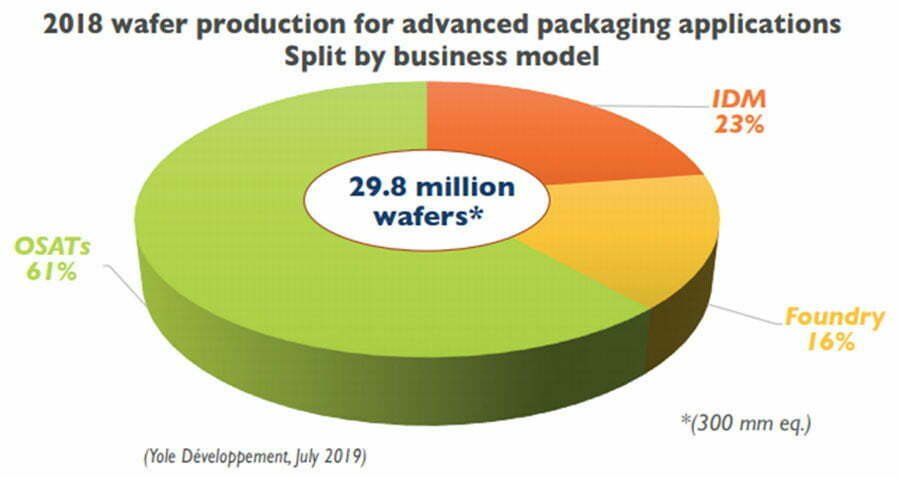

В 2018 году профессиональные фабрики по упаковке и тестированию микросхем составляли 61 % рынка передовой упаковки и тестирования, в то время как компании типа IDM составляли 23 %, а производители типа фабрик — 16 %.

Конкурентная среда

1. 10 ведущих мировых компаний (2018–2019 гг.)

Рынок упаковки и тестирования микросхем относительно концентрирован. Десять ведущих производителей контролируют около 80 % рынка. На рынке доминируют производители из материкового Китая и Тайваня. На протяжении многих лет тайваньская отрасль упаковки и тестирования микросхем захватывала почти половину мировой операционной выручки, прочно закрепившись в десятке лидеров.

Независимо от доходов IDM (таких как Intel и Samsung) от упаковки и тестирования микросхем, ASE и Amkor прочно занимают первые два места в сфере профессиональной упаковки и тестирования микросхем.

2. Возможности и вызовы

Изменения в цепочке поставок полупроводников, сдвиги в бизнес-моделях и неопределенность в торговых отношениях между США и Китаем создали возможности для одних производителей и угрозы для других.

2.1 Расширение производственной цепочки

В этой постоянно меняющейся бизнес-среде цепочка поставок полупроводников претерпевает изменения на всех уровнях. Некоторые поставщики успешно расширили новые бизнес-модели.

Это значительно повлияло на цепочку производства интегральных схем, в то время как другие производители не смогли воспользоваться этим моментом. Разные поставщики имеют разные движущие силы, побуждающие их расширяться в новые сферы бизнеса.

Например, такие софтверные компании, как Google, Microsoft, Facebook и Alibaba, разрабатывают собственные процессоры, чтобы обеспечить интеграцию/настройку на системном уровне и контроль над цепочкой поставок на уровне сборки.

Самым большим изменением является то, что фабрики начинают расширяться в бизнес передовой упаковки. Хотя они являются относительно «новичками», их влияние огромно.

2.2 Инновации в технологии упаковки

TSMC лидирует в области инноваций в сфере фанат-аут упаковки и передовых платформ 3D упаковки. Компания предлагает широкий спектр продуктов, таких как InFO (и его варианты), CoWoS, WoW, 3D SoIC и другие.

Передовые упаковочные технологии стали зрелым направлением бизнеса для TSMC. Компания ожидает, что в 2019 году этот сегмент принесет ей 3 миллиарда долларов дохода, что позволит ей занять четвертое место в рейтинге OSAT.

UMC является крупным поставщиком кремниевых интерпозеров для 2,5D-упаковки. Недавно компания заключила партнерское соглашение с Xperi с целью оптимизации и коммерциализации технологий ZiBond и DBI для различных полупроводниковых устройств.

Между тем, Wuhan Xinxin (XMC) поставляет 3D IC TSV-корпуса для датчиков изображения и высокопроизводительных приложений. В совокупности эти игроки сыграли важную роль в переходе от подложек к кремниевым платформам.

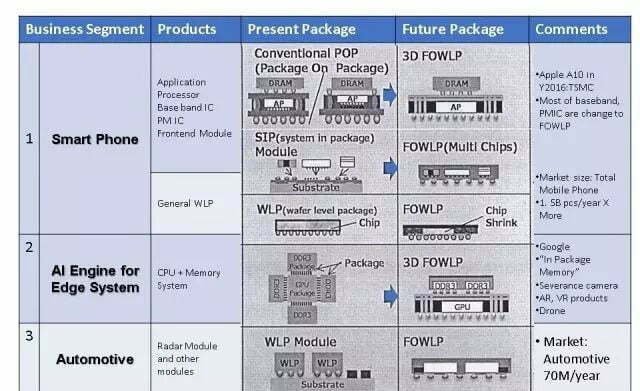

2.3 Упаковка на системном уровне, как правило, пользуется популярностью

Существует тенденция, при которой участники цепочки производства упаковки SiP расширяют свою деятельность вверх и вниз по цепочке. В традиционной цепочке производства упаковки SiP представительными компаниями в области упаковки и тестирования интегральных схем являются Changdian Technology и ASE, которые в основном предоставляют стандартные продукты для упаковки и тестирования на функциональном уровне. Представительной компанией в области упаковки на системном уровне является USI, которая в основном занимается упаковкой систем на уровне модулей. Эти две компании находятся в отношениях «верх-низ» по цепочке, и их процессы и оборудование различаются.

2.4 Встроенные микросхемы

С другой стороны, производители подложек для интегральных схем и печатных плат, такие как Samsung Electro-Mechanics (SEMCO), Unimicron, AT&S и Shinko Electric (Shinko), используют преимущества встроенных микросхем (и пассивных компонентов) в панельных фан-аут-корпусах и органических подложках. компоненты) в сфере передовых упаковочных технологий и отнимают долю рынка у OSAT (особенно в сфере передовых упаковочных технологий).

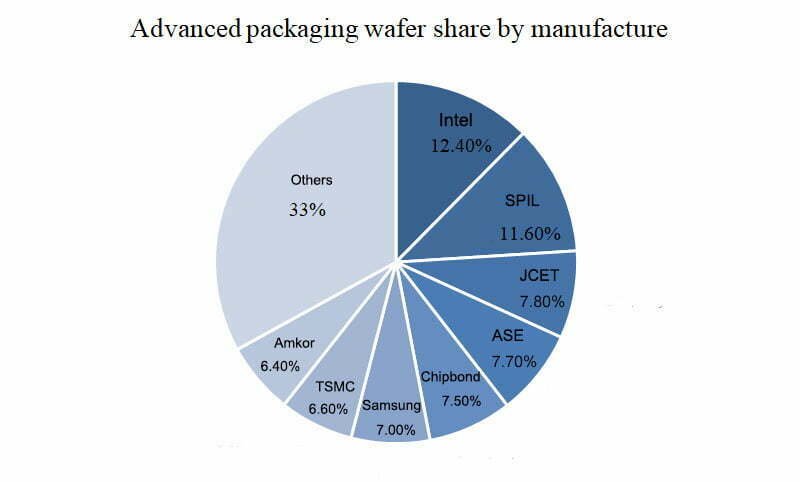

3. Доля рынка передовых упаковочных пластин

По сравнению с общей концентрацией рынка упаковки и тестирования, концентрация рынка передовой упаковки и тестирования относительно низка. В 2017 году на долю 8 ведущих производителей приходилось 67 % рынка передовой упаковки.

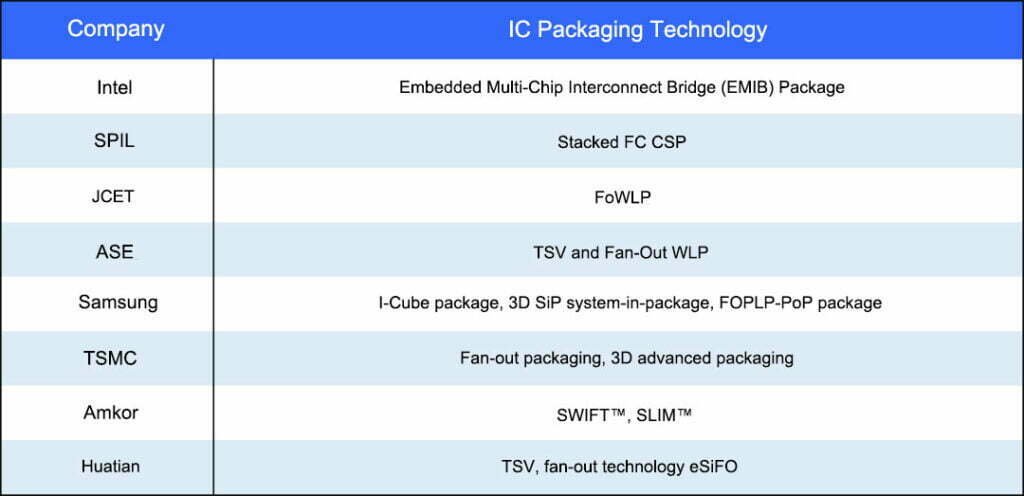

Поставщики на рынке передовых упаковочных решений имеют различные области специализации:

Ситуация в китайской индустрии производства микросхем

Китайская индустрия упаковки интегральных схем началась очень рано и быстро развивалась, в основном опираясь на традиционные упаковочные продукты. В последние годы отечественные производители прошли через слияния и поглощения. В настоящее время технологическая платформа Китая в основном синхронизирована с зарубежными производителями. Более того, передовые технологии упаковки, такие как BGA, TVS, WLCSP и SiP, были запущены в массовое производство.

Однако между общим доходом от передовой упаковки на Тайване и в США все еще существует определенный разрыв. Согласно статистике TrendForce, доход от передовой упаковки в Китае в 2018 году составил около 52,6 млрд юаней. Он составил 25% от общего дохода от упаковки и тестирования в стране, что ниже глобального показателя в 41%. Таким образом, в будущем еще есть большой потенциал для роста.

Рынок передовых упаковок интегральных схем в Китае

Кроме того, существует большой разрыв между упаковочными компаниями материкового Китая и ведущими международными производителями. Особенно очевиден этот разрыв в области технологий упаковки интегральных схем высокой плотности, таких как технология упаковки чипов HPC. Технология многочипового 3D-упаковки SoC, предложенная TSMC. В ней используется структура без выпуклых соединений, что позволяет значительно повысить общую скорость вычислений CPU/GPU и памяти. Intel также предложила аналогичную концепцию 3D-упаковки, в которой память укладывается на чипы CPU и GPU.

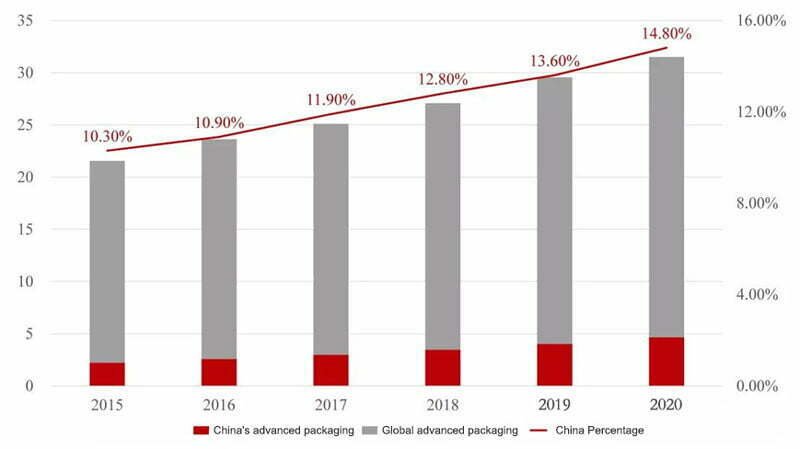

Объем мирового производства на рынке передовых упаковочных материалов в Китае относительно невелик, но он быстро растет, а его доля увеличивается. Данные Yole. В 2017 году объем производства передовых упаковочных материалов в Китае составил 2,9 млрд долларов США, что составляет 11,9% от мирового объема, а к 2020 году он достигнет 4,6 млрд долларов США, что составляет 14,8% от мирового объема. Согласно данным, в 2018 году китайские компании, занимающиеся упаковкой и тестированием, ускорили рост производственных мощностей в области передовой упаковки, причем темпы роста составили 16%, что в два раза превышает мировой показатель.

движущая сила рынка

Существует два пути развития передовых упаковочных технологий:

один из них заключается в уменьшении размера, чтобы он приблизился к размеру чипа. Важным показателем является соотношение площади чипа к площади упаковки. Чем ближе это соотношение к 1, тем лучше, включая WLCSP, FC, Bumping, Fanout и т. д.

Второй путь — функциональное развитие, которое делает акцент на гетерогенной интеграции и обеспечивает многофункциональность при миниатюризации системы, включая TSV, SIP и т. д.

1. Технология SIP

Глобальный процесс производства полупроводников приближается к физическому пределу диодов. Наиболее передовой процесс — 7 нм. Из-за огромных инвестиций дальнейшее улучшение характеристик чипов с точки зрения производства становится все более дорогостоящим. Начиная с упаковки чипов, технология SIP (system-in-package) объединяет чипы с различными функциями, такими как логические чипы и память.

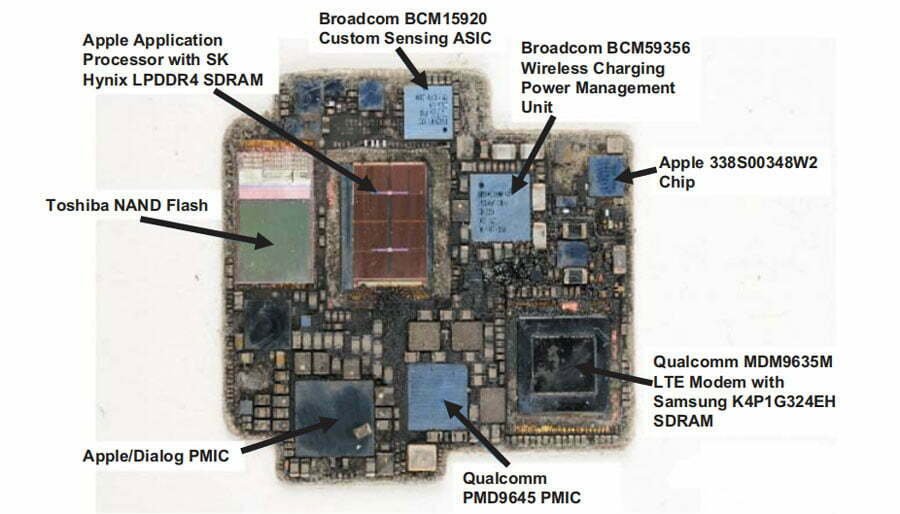

Пассивные компоненты IPD, RF RF и датчики, а также другие чипы упаковываются в один модуль, что позволяет уменьшить размер чипа, улучшить его производительность и снизить энергопотребление. Интернет вещей (IoT) является важным сценарием применения, который способствует развитию технологии упаковки SIP, а носимые устройства являются областью с большим потенциалом применения технологии «система в корпусе» в будущем. Датчик распознавания отпечатков пальцев, датчик 3D-распознавания лиц, беспроводная сеть WiFi и другие функциональные модули в Apple Watch упакованы вместе, что является использованием технологии модулей «система в корпусе» (SiP) ASE.

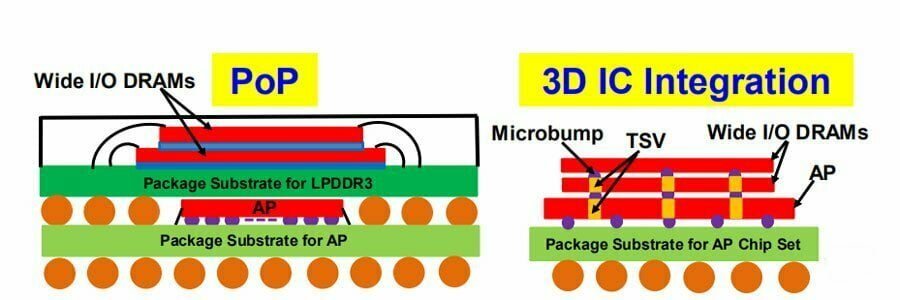

Технология SIP успешно интегрирует интегральные схемы, дискретные устройства, оптические устройства, память, многослойные керамические конденсаторы и чип-резисторы в тонкие, плоские и короткие подложки без взаимного влияния их информации. Мы считаем, что Apple, по крайней мере, на один-два года опережает конкурентов в области применения системной упаковки. В зависимости от различных требований к применению и сложности продукта, типы систем в корпусе SiP можно разделить на 2D-модули, содержащие несколько активных и пассивных компонентов, и более сложные 3D-модули. Например, PiP (Package-in-Package) в системе, PoP (Package-on-Package) и технология упаковки 2.5D/3D в системе.

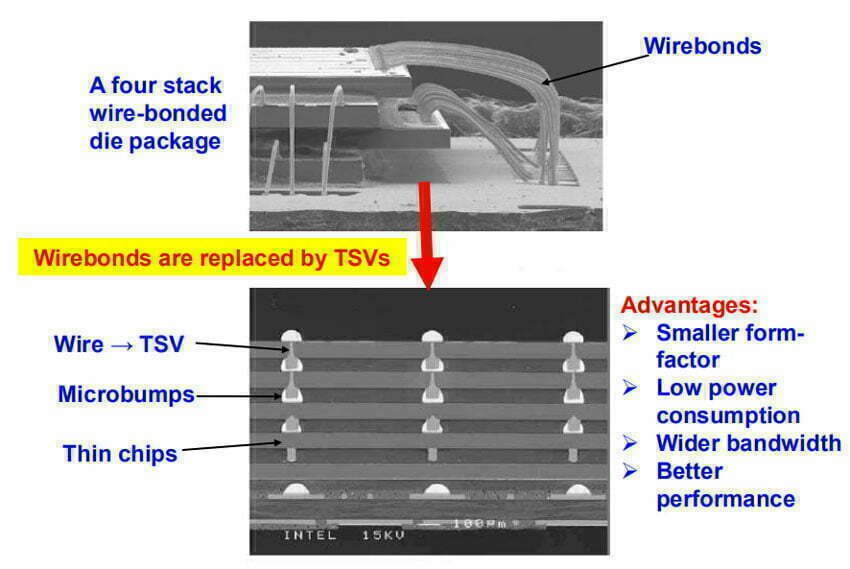

2. Технология TSV

Как представитель технологии 3D-упаковки, технология TSV в будущем найдет более широкое применение в области упаковки флэш-памяти 3DNANDFLASH и упаковки памяти DRAM. Память стала подразделом с наибольшим потенциалом роста в отечественной полупроводниковой отрасли. Два крупных проекта в области памяти, Yangtze Memory (NAND FLASH) и Hefei Changxin (DRAM), будут запущены в массовое производство в 2020 году, что, несомненно, станет огромной возможностью для роста отечественных производителей, обладающих передовыми технологиями упаковки.

3. Расширение

С вступлением в эру 5G для получения более высокой скорости передачи данных и пропускной способности необходимо использовать в качестве средства передачи электромагнитные волны более высокой частоты, а длины волн становятся короче и достигают уровня миллиметровых волн. Две основные частоты в эпоху 5G, полоса частот ниже 6 ГГц и полоса частот миллиметровых волн 28 ГГц, из-за увеличения частоты, в результате снижения длины волны антенна становится короче, поэтому ожидается, что в эпоху чипов 5G антенна будет интегрирована в чип, чтобы упростить конструкцию и снизить затраты.

Существует две возможные технологии упаковки для чипов 5G следующего поколения: AiP (Antenna in Package) с подложкой и фан-аут упаковка без несущей платы. Поскольку вторая схема фан-аут упаковки не требует подложки, она может еще больше снизить затраты и уменьшить размер чипа на основе интеграции нескольких чипов, поэтому технология фан-аут упаковки может стать основной технологией упаковки чипов 5G.

Каждый электронный модуль в автомобиле использует различные технологии упаковки, и для упаковки миллиметрового радиолокационного чипа в автомобильной электронике также будет использоваться большое количество технологий упаковки Fan-out.

Отечественный завод по упаковке и тестированию Changdian Technology приобрел технологию упаковки eWLB после поглощения Xingke Jinpeng, став одним из первых производителей упаковки и тестирования в области миллиметрового радара. Ожидается, что Huatian Technology приложит усилия в этой области после недавних технологических прорывов.

Направление развития технологий

Существует два типа упаковки полупроводников: традиционная упаковка и усовершенствованная упаковка. С постоянным расширением масштабов усовершенствованной упаковки ее доля постепенно приблизилась к традиционной упаковке и превзошла ее. Для полупроводниковой промышленности упаковка и тестирование больше не являются отдельным звеном в производственном процессе, как в прошлом, а представляют собой интегрированное решение, сочетающее в себе дизайн, материалы и оборудование.

Поэтому передовое упаковывание становится все более важным в области упаковывания и тестирования полупроводников. Согласно прогнозу Yole, к 2020 году глобальный рынок передового упаковывания достигнет 44% от общего объема услуг по упаковыванию интегральных схем, с годовым операционным доходом примерно 31,5 млрд долларов США; рынок передового упаковывания Китая достигнет 4,6 млрд долларов США в 2020 году, с совокупным годовым темпом роста 16%. С технической точки зрения, FOWLP, SiP и 3DTSV являются тремя наиболее востребованными передовыми технологиями упаковки и тестирования.

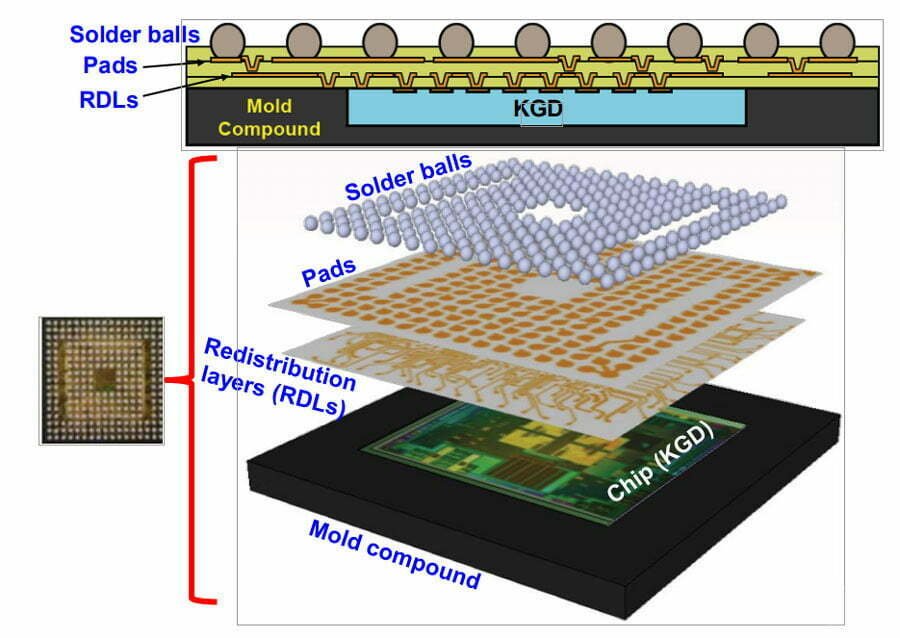

1. Упаковка FOWLP

Пакет FOWLP относится к новому методу объединения нескольких кристаллов из гетерогенных процессов в компактный пакет. Впервые он был предложен компанией Intel. Преимущества FOWLP по сравнению с технологией фанатной упаковки: уменьшенная толщина пакета, масштабируемость (для увеличения количества входов/выходов), улучшенные электрические характеристики, хорошие тепловые характеристики и процесс без подложки.

2. Упаковка SiP

Система в корпусе (SiP) — это новый тип технологии упаковки, представляющий собой высший уровень в области упаковки интегральных схем, который объединяет один или несколько чипов интегральных схем и пассивных компонентов в одном корпусе. SiP — это идеальное решение, которое сочетает в себе преимущества существующих основных ресурсов и процессов производства полупроводников, позволяя снизить затраты и сократить время вывода продукта на рынок. В то же время она позволяет преодолеть такие трудности, как совместимость процессов, смешивание сигналов, шумовые помехи и электромагнитные помехи в SOC. Кроме того, область применения SiP очень обширна. В настоящее время наибольшую долю, около 70 %, занимает производство смартфонов.

Растущий спрос на упаковку SiP вызван коммерческим использованием технологии 5G. Во-первых, из-за увеличения стоимости автономных RF, общий объем рынка RF-фронтэндов быстро вырос. Существует общая тенденция к модуляризации RF-фронтэнда, 5G-антенны миллиметрового диапазона и компонентов RF-интеграции, которые обычно основаны на GaAs. 5G-антенна в основном состоит из LCP (жидкокристаллического полимера), и упаковка SiP хорошо подходит для гетерогенной интеграции. Ожидается, что упаковка SiP станет более популярной в секторе RF.

3. 3D-упаковка — TSV

3D-упаковка улучшает основные характеристики, такие как размер, вес, скорость, производительность и энергопотребление, и считается большинством производителей полупроводников наиболее перспективным методом упаковки. По мере того как передовые технологии упаковки продолжают распространяться на передовые технологии с высокой производительностью и высокой плотностью интеграции, TSV, известная как технология 3D-упаковки четвертого поколения, как ожидается, станет устойчивой движущей силой для будущего развития передовых технологий упаковки.